Fターム[5B046JA04]の内容

Fターム[5B046JA04]の下位に属するFターム

論理シミュレーション (393)

Fターム[5B046JA04]に分類される特許

201 - 220 / 960

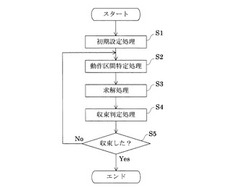

非線形要素の特性が区分折れ線近似されたシステムの動作点を電子計算機により求める方法、そのプログラム、当該プログラムを記録した記録媒体及びシミュレーション装置

【課題】非線形要素の特性が区分折れ線近似された非線形システムの動作点を高速且つ確実に収束することができる方法等を提供する。

【解決手段】解x(n)が属する非線形要素の動作区間を特定する動作区間特定処理と、動作区間における非線形要素の直線の傾き及び切片を計算し、傾き及び切片から非線形システムを表す方程式を線形化した式に基づいて、解x(n)を求める処理と、解x(n)が属する前記非線形要素の動作区間と、解x(n−1)が属する動作区間とが一致した場合に解x(n)を求める解とする処理とを備え、動作区間特定処理では、X軸を基準としたときの解x(n)が属する第1動作区間と、Y軸を基準としたときの解x(n)が属する第2動作区間とをそれぞれ求め、第1動作区間及び第2動作区間のうち解x(n−1)が属する動作区間に近い方を非線形要素の動作区間として特定する。

(もっと読む)

半導体装置設計システム

【目的】 回路トポロジ制約を含む制約式を用いて、個人の技量に依存せず、コンピュータのタクト時間を短縮できる半導体装置の自動設計システムの構築を目的とする。

【構成】 回路図内に含まれるトランジスタのそれぞれの回路定数を制約式に基づいて算出する第1の手段と、回路定数が反映された回路図に対して電気的特性の算出を行う第2の手段と、電気的特性の算出結果が設計仕様を満たすようになるまで、パラメータへの代入値を変更しながら上記手段の処理をループさせる第3の手段と、キルヒホッフの電流則を反映する制約条件を回路図から抽出して制約式に含ませる第4の手段とを、出力制御部107とシミュレータ制御部104と入力制御部105と回路シミュレータ部103とトポロジ制約抽出部106で構成することを特徴とする。

(もっと読む)

材料設計統合システム

【課題】 本発明は、1つの統合システムで、分子のポテンシャルエネルギーや力の計算が可能なソフトウェアや分子動力学法ソフトウェアを統合プラットフォームの指令に基づき連動処理させることによって、効率的な材料設計を可能にするシステムを提供する。

【解決手段】 本発明は、分子のポテンシャルエネルギーや力の計算が可能なソフトウェアや分子動力学法ソフトウェアを統合プラットフォームの指令に基づき連動処理させることによって、従来手法では完了できなかった計算、従来手法では手間がかかっていた計算、複数の従来手法の組み合わせが必要で新規なソフトウェアを作成しないとできなかった計算を1つの統合システムによって効率的に実施可能にするものである。

(もっと読む)

パワーインテグリティ解析装置及び方法並びにプログラム

【課題】切り欠き等の複雑な形状を含むPDNを、高速に解析することができるパワーインテグリティ解析装置を提供する。

【解決手段】パワーインテグリティ解析装置1は、多層構造の回路基板に含まれる電源層及びグラウンド層の形状とその配置を示す構造情報を入力する構造情報入力部10と、電源層及びグラウンド層を格子状に分割し、対向する2つの単位面によって挟まれた3次元領域を単位セルとして画定する単位セル画定部11と、各単位セルに単位セル等価回路の基本構成を適用し各単位セルの単位面の大きさと単位面間の距離とに基づいて、各単位セルの等価回路を構成する接地キャパシタ及びインダクタの値を決定して各単位セルの等価回路を生成した後、互いに隣接する単位セルの等価回路を連結して全体の等価回路を生成する等価回路生成部13と、所定の位置に電圧を印加したときに他の位置に生じる電圧値を計算するパワーインテグリティ計算部14とを備える。

(もっと読む)

検証装置、検証方法及び検証プログラム

【課題】シミュレーション精度が悪い部分についての検証精度の低下を抑制する。

【解決手段】検証装置は、シミュレーションにより第1及び第2のパターンを算出して、第1及び第2のパターンのシミュレーションデータを作成する手段と、製造プロセスにより製造された半導体装置が有する第1のパターンの寸法と、シミュレーションデータにおける第1のパターンの寸法との差分値を記憶する記憶手段と、差分値からシミュレーションデータにおける第2のパターンの移動量を算出する手段と、シミュレーションデータにおける第2のパターンの位置を、所定方向に移動量の値に応じて移動させて、第1のパターンと第2のパターンとの重なり面積が所定基準を満たすか否かを判定する手段と、所定基準を満たしていないと判定された場合、エラー情報を出力する手段と、を備える。

(もっと読む)

設計支援プログラム、設計支援装置および設計支援方法

【課題】ノイズ発生による回路性能の変化を把握するとともに、ノイズによる性能劣化を回避するクロックツリーの設計を支援する。

【解決手段】設計支援装置100は、対象回路設計情報101を取得すると、ノイズによる影響を把握するためアナログ回路に関する情報を取得して、ノイズ入力タイミングと性能変化との関係を検証する(ステップS110)。また、ノイズを発生させる回路を把握するためデジタル回路に関する情報を取得し、回路内で発生するノイズを算出する(ステップS120)。そして、ステップS110,120にて得た情報を用いてノイズの入力タイミングを回路性能への影響の小さいタイミングに調整する(ステップS130)。最後に、回路全体の動作タイミングを、特定した入力タイミングの期間と、ステップS120によって算出されたノイズのピークとが重複しないようなタイミングに調整したクロックツリーを設計する(ステップS140)。

(もっと読む)

自動回路設計用パレートデータ生成プログラム、方法及び装置、並びに自動回路設計プログラム、方法及び装置

【課題】設計者における最適化処理時間を削減しつつ、要求仕様を満たす又は満たさない場合でも当該要求仕様に近い回路を自動設計する。

【解決手段】特定の機能を有する回路構成とプロセス制約条件との組み合わせにて、要求仕様の各項目についての解仕様空間における非劣解であるパレート最適解の集合を抽出し、さらに回路構成及びプロセス制約条件との全ての組み合わせについてのパレート最適解と、各プロセス制約条件についてのパレート最適解とをさらに抽出する。このようなデータを設計者に頒布することによって、パレート最適解を生成する時間を節約することができるようになり、設計者は、このようなデータを用いて希望する機能を有する最適な回路を設計することができるようになる。

(もっと読む)

論理エミュレーション方法及び論理エミュレーションプログラム

【課題】効率的な時分割多重化論理回路挿入を行う論理エミュレーションの提供。

【解決手段】ハードウェア記述言語により記述した内部論理機能ブロック接続状態を論理分割し、該分割した機能ブロックを接続する論理的接続ピン数が物理的ピン数を超えると判定したとき、論理的接続ピン数が物理的ピン数以下に収まるように時分割多重化回路を挿入したFPGA用データを生成する第1機能と、該生成したFPGA用データを用い、コンピュータの1システムクロック期間中に、予め設定した多重化起動トリガ数にピン多重度数を乗算した数の駆動クロックを発生させ、該論理エミュレーションを実行する第2機能と、時分割多重化回路が多段挿入されている接続状態を検出し、該多段挿入を禁止するように物理的論理素子用データを修正する第3機能と、この修正物理的論理素子用データを用いて設定した最大駆動クロック数により論理エミュレーションを実行する第4機能とを実行させるもの。

(もっと読む)

タイヤ性能シミュレーション方法、タイヤ性能シミュレーション装置、及びタイヤ性能シミュレーションプログラム

【課題】精度良くひずみエネルギーロスを求める。

【解決手段】タイヤ性能シミュレーション方法は、タイヤを複数の要素にメッシュ分割したタイヤモデルについて転動解析を実行し(ステップ104)、転動解析の解析結果に基づいて、要素の変位の時刻歴分布とCauchy応力の時刻歴分布とを求め(ステップ106〜108)、変位の時刻歴分布に基づいて、Greenひずみの時刻歴分布を求め(ステップ110)、変位の時刻歴分布とCauchy応力の時刻歴分布とに基づいて、2ndPiora-Kirhihoff応力の時刻歴分布を求め(ステップ112)、Greenひずみの時刻歴分布と2ndPiora-Kirhihoff応力の時刻歴分布とに基づいて、Greenひずみと2ndPiora-Kirhihoff応力とに位相差を付与することにより、要素のひずみエネルギーロスを求め(ステップ114)、各要素のひずみエネルギーロスを加算することによりタイヤのひずみエネルギーロスを求める(ステップ116)。

(もっと読む)

ばらつき分布シミュレーション装置及び方法

【課題】プロセス変動が回路特性に及ぼす影響を予測可能とするシミュレーション方法を提供する。

【解決手段】MOSFETを有する半導体回路のばらつき解析用に、MOSFETのSPICEパラメータの設定値を算出する回路シミュレーション装置であって、当該回路シミュレーション装置は、MOSFETのばらつき特性に影響を及ぼす変数として、MOSFETの製造条件又は素子構造に関する変数を含み、当該変数により定義される物理量とSPICEパラメータとの間に物理的な相関を有する普遍的関数により構成された中間モデル式を記憶する記憶部101と、この中間モデル式に含まれる変数に関する情報を設定するための設定部102と、設定部に設定された情報と、記憶部に記憶された中間モデル式とに基づいて、SPICEパラメータの設定値を算出する算出部103と、上記半導体回路のプロセス変動依存性を出力する出力部104とを備える。

(もっと読む)

回路シミュレーション方法

【課題】半導体抵抗素子の端子部寄生抵抗を正確に見積もることができる回路シミュレーション方法。

【解決手段】端子部と抵抗本体部とを有するウェル抵抗素子102と、端子部上に形成されたコンタクトCTと、を備えた半導体回路のシミュレーション方法。コンタクトCTと抵抗本体部との間の端子部の寄生抵抗Rt0を、次式によりモデル化する(ただし、ρ0、L'0、W'0:フィッティングパラメータ、L':前記ウェル抵抗素子の長手方向の前記端子部の長さ、W':前記ウェル抵抗素子の幅方向の前記端子部の幅)。 (もっと読む)

(もっと読む)

回路シミュレーション方法

【課題】半導体抵抗素子の端子部寄生抵抗を正確に見積もることができる回路シミュレーション方法。

【解決手段】半導体抵抗素子102と、半導体抵抗素子102の端子部上に、半導体抵抗素子102の幅方向と長手方向とにそれぞれ等間隔に配置された複数のコンタクトCTと、複数のコンタクトCT上に形成された配線101と、を備えた半導体回路のシミュレーション方法。1つのコンタクトCTの抵抗値と、長手方向において隣接するコンタクトCT間の半導体抵抗素子102による寄生抵抗値との比を、定数kとして定義し、半導体抵抗素子102の端子部と、複数のコンタクトCTと、を含む寄生抵抗ネットを、定数kを用いることによりモデル化する。

(もっと読む)

タイミングライブラリ検査装置、タイミングライブラリ検査方法、及びタイミングライブラリ検査プログラムを格納する記憶媒体

【課題】タイミングの見落としに起因するLSIの誤動作及びタイミング調整回路と消費電力の増加問題を解決する。

【解決手段】タイミングライブラリ検査装置は、LSIのタイミング制約値を含むタイミングライブラリ入力部12と、そのライブラリから、LSIのタイミング制約の基準となる基準端子毎のタイミング制約を受ける制約端子のタイミング制約値を含み、複数の基準端子と制約端子の波形鈍りを行方向及び列方向に持つルックアップテーブルで表されるタイミング制約データを抽出する抽出部14aと、抽出されたデータに対し、隣接する2つのタイミング制約値の差を算出し、その増加又は減少を示す増減データ作成部14bと、14bによって作成された増減データに増加及び減少が含まれているか否かを判定する判定部14cと、含まれていると判定された場合に、タイミングライブラリに特異点が含まれることを報知する出力する出力部18と、を備える。

(もっと読む)

眼鏡のフィッティングシミュレーションシステム、眼鏡のフィッティングシミュレーション方法及びプログラム

【課題】 眼鏡フレームが個人の顔にフィットするように調整する作業をシミュレートすることが可能な眼鏡のフィッティングシミュレーションシステム、眼鏡のフィッティングシミュレーション方法及びプログラムを提供すること。

【解決手段】 標準顔形状モデルと、複数の部品の形状モデルから構成される眼鏡フレームの形状モデルとを記憶する記憶部と、個人の複数の顔画像から特徴点を抽出し、抽出した特徴点の三次元位置情報に基づいて、前記標準顔形状モデルを変形して個人の顔形状モデルを生成する顔形状モデル生成部と、生成された前記顔形状モデルに対して、前記眼鏡フレームの形状モデルの位置を合わせる位置合わせ部と、位置合わせが行われた前記眼鏡フレームの形状モデルを構成する少なくとも1つの部品の形状モデルを、前記顔形状モデルに合わせて変形する眼鏡フレーム形状モデル変形部とを含む。

(もっと読む)

テストベンチの作成方法、テストベンチ作成装置

【課題】アナログ回路の入力スティミュラスの発生タイミングを回路の状態に同期して決定することができるテストベンチの作成方法等を提供すること。

【解決手段】ノード電圧とアナログ回路の状態の関係を規定する回路仕様情報、を指定するステップS100と、テスト仕様指定情報を指定するステップS200と、回路仕様情報に基づき、ノード電圧からシミュレーション実行中の状態を検出する状態検出テストベンチを生成するステップS300と、テスト仕様指定情報の時系列情報に、状態検出テストベンチが検出した状態が一致する場合に、シミュレーション実行中の状態遷移を特定する特定情報を出力する状態判定テストベンチ、を生成するステップS400と、テスト仕様指定情報に登録された電圧、電流まで過渡状態時間をかけて変化させるスティミュラス最適化テストベンチを生成するステップS500と、を有する。

(もっと読む)

形状シミュレーション装置、形状シミュレーションプログラム、半導体製造装置及び半導体装置の製造方法

【課題】シミュレーションの精度を向上できる形状シミュレーション装置を提供する。

【解決手段】シミュレーション装置のフラックス演算部は、有効立体角Se、ウェハ開口率Rw及びセミローカル開口率Rsに基づいて、計算点221毎の入射フラックスΓを演算する。有効立体角Seは、計算点221が当該計算点221を含むローカル領域223におけるパターンに遮蔽されずに開放される範囲を計算点221側から見込んだ立体角である。ウェハ開口率Rwは、ウェハ201を覆うマスク207の面積に対するマスク207の開口面積の比である。セミローカル開口率Rsは、ローカル領域223を含み、ウェハ201よりも狭いセミローカル領域227の面積に対する当該セミローカル領域227におけるマスク207の開口面積の比である。

(もっと読む)

回路設計支援方法、回路設計支援装置および回路設計支援プログラム

【課題】回路全体の動作速度に影響を与えない範囲でのセル最適化を支援すること。

【解決手段】半導体集積回路内のパスの遅延分布から、半導体集積回路全体の動作タイミングに影響を与えることのないパスの動作遅延の上限値を上限パスディレイとして求める。上限パスディレイを用い、セルサイズの変更が半導体集積回路全体の動作タイミングに影響を与える可能性のあるクリティカルパスを求める。クリティカルパス上に含まれるセルのセルサイズを小さくしないこと、およびクリティカルパス上に含まれないセルのセルサイズを小さくする場合には当該セルを含むパスの遅延が上限パスディレイを超えないことをセルサイズ最適化の制約条件とする。

(もっと読む)

建物の空気流シミュレーション方法

【課題】外気風を利用して複数の部屋の通風状態を三次元的に予測するためのシミュレーション方法を提供する。

【解決手段】複数の部屋及び部屋どうし或いは内外を連通する開口部5を有する住宅に於ける空気流のシミュレーションを行なうに当たり、建物Aの内部及び外周部位で当該建物の外部を流れる風が建物の外壁に衝突したときの挙動を予測し得る所定の範囲を予め設定された寸法を持った直方体で仕切り、且つ建物の外周部位で前記所定の範囲よりも更に外側の所定範囲を前記直方体の寸法よりも大きい寸法を持った直方体で仕切り、自然風を設定して、該自然風が住宅の影響を受けて該住宅に沿った外周部を流れる際の挙動や、住宅に形成された開口部から屋内に入り込んで他の開口部から出て行くまでの挙動を立体的に予測する。

(もっと読む)

シミュレーション装置およびシミュレーション方法

本発明は、カスケード通信システムのためのシミュレーション装置およびシミュレーション方法に係わる。カスケード通信システムは、送信器から受信器に向かって連続する番号1〜Nが付与される複数のノードを備える。本方法は、カスケード通信システムのシミュレーションを行うために必要なシミュレーションパラメータを取得し、各ノードの逆伝達関数を計算し、N番目のノードから1番目のノードに向かって順番に現ノードを決定し、現ノードにおいて付加されるべき雑音を現ノードの前ノードのシミュレーション信号に付加し、現ノードにおいて付加されるべき雑音が付加された前ノードのシミュレーション信号を利用することにより、現ノードの逆伝達関数に基づいて、現ノードのシミュレーションを行ってシミュレーション信号を生成し、すべてのノードのシミュレーションが終了したか判定し、すべてのノードのシミュレーションが終了していなければ、付加する工程および現ノードのシミュレーション信号のためのシミュレーションを行う工程を繰り返し、すべてのノードのシミュレーションが終了していれば、現ノードのシミュレーション信号に基づいてカスケード通信システムのコストを決定する。 (もっと読む)

画像処理回路のシミュレーション装置、画像処理回路のシミュレーション方法、画像処理回路の設計方法、及び画像処理回路のシミュレーションプログラム

【課題】目視による動画像に対する画像処理結果の効果の定性的及び定量的な評価を容易化できる画像処理回路のシミュレーション装置等を提供する。

【解決手段】複数のフレーム画像により構成される動画像に対して画像処理を行う画像処理回路の動作をシミュレーションする画像処理回路のシミュレーション装置1は、画像処理回路に対応する機能を具備する画像処理モジュールと、画像処理モジュールを実行し、各フレーム画像に対して前記画像処理を行うモジュール実行手段63と、モジュール実行手段63で実行された画像処理モジュールによる画像処理が行われた画像データに対してグループ化を実行する結果グループ化実行手段66と、当該フレームより前の1又は複数のフレームの各フレーム画像に対して画像処理が行われた過去フレーム処理後画像データに対する所与の演算結果を記憶する記憶手段とを含む。

(もっと読む)

201 - 220 / 960

[ Back to top ]