Fターム[5B046JA05]の内容

Fターム[5B046JA05]に分類される特許

1 - 20 / 393

活動センサでデジタル回路を設計するシステム及び方法

【課題】SoC回路の場合であっても、機能記述ファイルに基づいてデジタル回路がそれ自体の出力変数(温度など)を計算できるようにする。

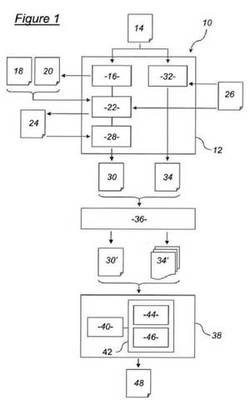

【解決手段】デジタル回路の機能記述を含むファイル14に基づいたデジタル回路シミュレータ12とシミュレータ12に供給されるテストベンチ26を実行する時にデジタル回路から出力変数30’を予想する手段28とイベントカウンタ34’とを含み、イベントは、テストベンチ26を実行する時にシミュレータ12によって提供された制御信号を用いて検出される。システムは、イベントカウンタからの出力データを用いてデジタル回路の出力変数30’を計算するモデルを反復して最適化することによって、イベントカウンタ34’の一部を選択する手段40、44とイベントカウンタの選択された部分及び最適化された計算モデルを登録する手段40、44とを更に含む。

(もっと読む)

回路検証装置および回路検証方法

【課題】半導体デバイスのシミュレーションに必要なパラメータを読み出すための構成を簡素化する。

【解決手段】ハードウェア記述言語に基づく論理回路が形成された半導体デバイス(102)のエミュレーションのための信号をデバイスへ入力する手段(140)と、論理回路に対応したハードウェア記述言語によりシミュレーションを実行する手段(110)と、シミュレーションに係るパラメータをデバイスから取得する手段(107)と、取得したパラメータをシミュレーションに適用する手段(111)と、パラメータ取得前に論理回路を修正する手段(130)とを備える。論理回路を修正するとき、その論理回路にてパラメータを記憶する記憶素子がリング型のシフトレジスタとして動作するためのバイパス配線(101A)と、バイパス配線を介して各記憶素子のパラメータを読み出す読出部(101B)とを付加する。

(もっと読む)

論理シミュレーション装置および論理シミュレーション方法

【課題】トランスポートモデルを用いた論理シミュレータにおいて、スパイクの影響を論理動作の結果から確認できるようにする。

【解決手段】この論理シミュレーション装置では、2つの標準遅延フォーマット(SDF)ファイルを用いて論理シミュレーションを実行し、その結果を比較することにより、スパイクが被シミュレーション回路に及ぼす影響を確認することができる。一方のSDFファイルは、被シミュレーション回路を構成する論理ゲートと配線の理想的な遅延時間情報を記述したものである。そして、他方のSDFファイルは、論理ゲートの立ち上がりおよび立ち下がりの遅延時間が、互いに同一の値に設定されており、配線の立ち上がりおよび立ち下がりの遅延時間が、互いに同一の値に設定されている。すなわち、スパイクのパルス幅が変化したり、スパイク自体が消滅したりしないように設定されている。

(もっと読む)

シミュレーション装置及びシミュレーション方法

【課題】処理負担を軽減させることができるシミュレーション装置及びシミュレーション方法を提供する。

【解決手段】シミュレーション装置のコンピュータ11は、メモリ111と、遅延除去部112と、波形比較部113と、を備える。メモリ111は、対象回路を構成する素子の遅延情報を格納する。遅延除去部112は、素子による遅延を考慮した対象回路のシミュレーション結果である遅延シミュレーション波形から、遅延情報に基づいて、素子による遅延を除去した遅延除去済み波形を生成する。波形比較部113は、遅延除去済み波形と、素子による遅延を考慮しない対象回路のシミュレーション結果である無遅延シミュレーション波形と、を比較し、比較結果を出力する。

(もっと読む)

修正プログラム、修正装置、および修正方法

【課題】アサーションの修正作業の効率化を図ること。

【解決手段】アサーションA5は、対象回路DUTの設計情報101によるシミュレーションで不成立となったアサーションである。修正装置100で分解されたプロパティp1〜p4は、アサーションA5の論理構造にしたがって木構造データT5となる。プロパティp1〜p4は、テストベンチ102に組み込まれ、対象回路DUTのシミュレーションにより、成立、不成立が判断される。修正装置100は、プロパティp1に、「||X」を追加することで、プロパティp1を修正する。したがって、修正後にシミュレーションすると、クロックの立ち上がり時に、レジスタRb,Rcのビット値B,Cは「0」、レジスタRxのビット値Xは「1」になった場合、修正プロパティP1は成立する。

(もっと読む)

検証支援プログラム、検証支援方法、および検証支援装置

【課題】シミュレーション時間の短縮化を図ること。

【解決手段】検証支援装置が、検証対象回路の回路情報に所定入力パターンを与えるシミュレーション101のうちの(1)の実行中に、CDCジッタJ1を検出する。検証支援装置が、CDCジッタJ1の検出時のシミュレーション101の実行状態を複製する。検証支援装置が、複製されたシミュレーション101の実行状態のうちの第2のクロックドメイン内の素子の出力を、検出された出力値と異なる論理値に設定する。検証支援装置が、設定後の実行状態に基づくシミュレーション102(第2のシミュレーション)をシミュレーション101と排他的に実行する。論理シミュレータは複数のシミュレーションを並列実行できないため、論理シミュレータがいずれか一方のシミュレーションを実行中には他方のシミュレーションの実行は待機する。

(もっと読む)

モデル変換装置、モデル変換方法、およびプログラム

【課題】煩雑な手間や時間をかけることなく、シミュレーション用インターフェースモデルと動作合成用インターフェースモデルとを等価性を保ったまま相互に変換することが可能なモデル変換装置、モデル変換方法、およびプログラムを提供する。

【解決手段】固定された記述スタイルのシミュレーション用インターフェースモデルおよび固定された記述スタイルの動作合成用インターフェースモデルの各代数表現を変形し変形後の代数表現の双方が一致すれば数学的にモデルに等価性があるとして、モデルの相互変換を行う処理部を有し、処理部は、代数的に等価性を保つ以下の3つの操作a,b,cによる階層チャネルおよび集約チャネルモデル変換の相互等価変換を行う。a:ペイロード公開、およびペイロード隠蔽操作の相互等価変換、b:インターフェースおよびチャネル分解、およびインターフェースおよびチャネル集約、c:プロセスリマッピング操作。

(もっと読む)

非同期インターフェース検証装置、非同期インターフェース検証方法及びそのプログラム

【課題】RTLでの非同期インターフェースの検証を可能とする。

【解決手段】非同期インターフェース検証装置は、タイミング変更部120と、シミュレーション部121とを具備している。タイミング変更部120は、非同期インターフェースのRTL(Register Transfer Level)検証において、RTL100における非同期インターフェースの同期化部(F/F)の動作タイミングをクロックサイクルベースで変化させる。シミュレーション部121は、前記動作タイミングを変化させたRTLを用いてシミュレーションを実行し、非同期インターフェースが正常な動作をするか否かを検証する。

(もっと読む)

検証装置、検証方法及びプログラム

【課題】検証する範囲を少なくして、検証コストや検証時間の増大を抑制する。

【解決手段】抽出部12が、第1のクロック信号で動作する回路部21と、第2のクロック信号で動作する回路部22とを含む検証対象回路(論理回路20)から、ハンドシェイクの手順に従って回路部21と回路部22間でのデータの送受信を行うハンドシェイク部23を抽出し、検証部13が抽出されたハンドシェイク部23の信号が、その手順を満たすかを検証し、手順を満たさない信号があるとき、回路部21と回路部22のうち当該信号を出力する側で、当該信号が手順を満たさなくなる条件が回路動作時に起こり得るか検証する。

(もっと読む)

ソフトウェアシミュレーション装置、シミュレーション方法、及びプログラム

【課題】不定値を適切に扱うことができるソフトウェアシミュレーションを実現するシミュレーション装置、シミュレーション方法、及びプログラムを提供すること

【解決手段】所定回路シミュレータ90は、所定の回路(たとえばフリップフロップ回路、メモリ回路)の動作を模擬(シミュレーション)する。不定値変換手段30は、所定回路シミュレータ90からの出力が不定値である場合に"0"または"1"に変換して後段のシミュレータに出力する。

(もっと読む)

設計検証方法及びプログラム

【課題】 本発明の課題は、検証仕様に従った経路探索の結果を用いて、経路外のブロックの動作の抽象度を変更することにより高速にかつ適切にシミュレーションを行えるようにすること。

【解決手段】 上記課題は、コンピュータによって実行される設計検証方法であって、複数のブロックで構成される回路の検証に係る端子情報に基づいて、記憶部に格納されたネットリストを参照することによって、該ブロック間の接続関係に従って経路を探索し、前記ネットリスト内に記述される、前記探索された経路外のブロックの動作の抽象度を変更することを特徴とする設計検証方法により達成される。

(もっと読む)

検証方法及び検証プログラム

【課題】回路検証に用いるシナリオ等のプログラムを効率的に開発する。

【解決手段】コンピュータが、検証対象に対する命令を記述したシナリオ(S65)の所定記述部分の命令実行を制限する制限情報を含んだ設定制限リスト(S67)を用い、その内容を示すシナリオチェッカ(S69)を生成する。コンピュータは、検証対象のシミュレーション(S74)において、シナリオ(S65)の上記所定記述部分の命令実行時に、シナリオチェッカ(S69)を用いて当該命令が制限情報を含むか否かチェックし、その結果(S75)を出力する。

(もっと読む)

マルチサイクルパス検出装置及びマルチサイクルパス検出プログラム

【課題】ユーザ仕様依存のマルチサイクルパスを短時間で自動検出するマルチサイクルパス検出装置を提供する。

【解決手段】マルチサイクルパス検出装置10は、RTLデータとネットリストとのいずれかと、RTLシミュレーションで使用されたユーザ検証パタンとを基に論理検証を実行する論理検証部11と、前記論理検証の結果に基づき、半導体集積回路のパスを特定パスとして特定し、かつ、特定パスの始点のデータ値と終点のデータ値との比較を行う始点終点データ比較部12と、特定パスを伝搬する0と1とのいずれかのデータでありクロック信号のサイクル数をデータ幅とするデータを対象として、始点終点データ比較部12によるデータ比較結果に基づき、最小のサイクル数を示すデータ幅最小値を抽出するデータ幅最小値抽出部13と、データ幅最小値に応じて、特定パスにおけるマルチサイクル数を決定するマルチサイクル数決定部14とを備えた。

(もっと読む)

論理集積回路のCADシステム及びスピントロニクス論理集積回路の設計方法

【課題】設計フローの最小限の変更のみでスピントロニクス論理集積回路の設計体系を確立する。

【解決手段】論理集積回路のCADシステムは、ハードウェア記述言語で記述された動作記述レベルあるいは論理ゲートレベルの論理集積回路ネットリストから、論理合成ツールの入力となるスピントロニクス論理ゲートを含む動作レベルの論理集積回路ネットリストへの変換手段を含む。変換手段は、指定される不揮発化対象の論理信号を入力とする組み合わせ回路の一部をスピントロニクス論理回路に変換する。

(もっと読む)

集積回路装置、検証装置及び検証方法

【課題】集積回路装置が仕様通りとなっているかの検証の容易化を図る。

【解決手段】集積回路装置10は、マスターモジュール11と、マスターモジュール11に接続されたインターコネクト12と、インターコネクト12によってマスターモジュール11の接続先とされるスレーブモジュール13を含む。集積回路装置10は更に、そのスレーブモジュール13に対してインターコネクト12から送信されてくる読み出し命令信号を受信する固定値応答回路14を含む。インターコネクト12から読み出し命令信号を受信した固定値応答回路14は、インターコネクト12によってマスターモジュール11の接続先とされたスレーブモジュール13固有の固定値を、インターコネクト12に送信する。この固定値に基づき、接続先が仕様通りか否かを検証する。

(もっと読む)

消費電力検証支援装置

【課題】必要な波形データの取得ができ、かつ、シミュレーション時間を短縮することができる消費電力検証支援装置を提供することである。

【解決手段】実施の形態の消費電力検証支援装置は、消費電力概算部と、比較判定部と、遅延制御部と、ダンプ処理部とを有する。消費電力概算部は、指定信号を観測する第1のシミュレーションの所定時間毎に消費電力を概算する。比較判定部は、消費電力概算部で概算された消費電力の概算値を閾値と比較し、比較結果から所定時間毎にダンプ処理を行うか否かを判定する。遅延制御部は、全信号を観測する第2のシミュレーションを第1のシミュレーションに対して所定時間遅延させて実行させる。ダンプ処理部は、比較判定部の判定結果に基づき、ダンプ処理を行うと判定された所定時間の間の全信号の波形データを記録する。

(もっと読む)

論理回路検証装置、論理回路検証方法およびプログラム

【課題】論理シミュレーションに基づく論理回路の検証に要する時間を削減すること。

【解決手段】論理回路検証装置は、複数のモジュールを有する論理回路に対する論理シミュレーションを行うとともに、該複数のモジュールのそれぞれに対するコード・カバレッジ(コードの網羅率)を取得する論理シミュレータと、複数のモジュールのそれぞれに対するコード・カバレッジを参照し、コード・カバレッジが所定の割合よりも低いモジュールに対して第1のHDLコードを用いるとともに、それ以外のモジュールに対して第1のHDLコードに対するモデルよりも抽象度の高いモデルに基づく第2のHDLコードを用いて論理シミュレーションを行うように、論理シミュレータに指示するカバレッジアクセラレータと、を備えている。

(もっと読む)

検証機能を有する半導体デバイス

【課題】内部バスの検証モジュールを有する半導体デバイスを提供する。

【解決手段】内部バスと、第1の接続点において前記バスに接続されたマスターと、第2の接続点において前記内部バスに接続され、前記マスターと通信可能に設けられたスレーブと、検証モジュールとを備えた半導体デバイス。前記検証モジュールは、前記マスターが前記スレーブに供給した制御信号を検出し、当該検出信号に基づいて、前記内部バスの通信量に関するデータを生成する。前記制御信号は、前記マスターが前記スレーブを制御するための信号であって、例えば、書き込み信号、読み出し信号、バースト信号等を含む。前記検証モジュールは、各制御信号がアサートされた回数に基づいて、前記内部バスの通信量に関するデータを生成してもよい。前記検証モジュールは、前記内部バスに接続された検証用マスター及び検証用スレーブをさらに有してもよい。

(もっと読む)

半導体集積回路のレイアウト方法及びプログラム

【課題】パワードメインを自動作成する。

【解決手段】設計された回路が仕様を満たしているか否かを評価するための機能シミュレーション処理(9)と、上記機能シミュレーション処理の結果に基づいて、活性化タイミングが所定の範囲内で揃う論理ブロック毎にクラスタ分割することでパワードメインを得るクラスタ分割処理(10)とがコンピュータで行われる。これにより、パワードメインは、コンピュータで行われる処理によって得られるため、人手(設計者の手作業)によって求める場合に比べてパワードメインの最適化を図ることができる。

(もっと読む)

検証支援プログラム、検証支援装置、および検証支援方法

【課題】回路について定義したシナリオ外でのバグの特定の容易化を図ること。

【解決手段】クロックClkの立ち上がりクロックタイミングt5では、レジスタRの値が「3」から「5」に変化しているが、いずれのアサーションA1,A2どおりではない予期しない変化である。具体的には、その1サイクル後の立ち上がりクロックタイミングt6において、レジスタRの値「5」と期待値R_specの「3」が不一致となるため、アサーション外でのレジスタRの値の変化であるとしてエラー検出される。このように、アサーションA1,A2で定義されていないシナリオで発生するバグが検出できるため、アサーションにより検証対象回路の振る舞いを網羅できない場合であっても、バグの検出が可能となる。そして、検証者が、特定されたバグについてデバッグすることで、検証対象回路についてアサーション外でレジスタRの値が変化しないことを保証することができる。

(もっと読む)

1 - 20 / 393

[ Back to top ]