Fターム[5B057CH14]の内容

画像処理 (340,757) | 処理部 処理装置、処理システム (15,018) | バス、転送 (552)

Fターム[5B057CH14]に分類される特許

81 - 100 / 552

シンクライアントシステム、シンクライアントサーバ、シンクライアント端末、プログラム及び記憶媒体

【課題】画面転送型のシンクライアントシステムにおいて、端末に表示される機密情報が不正に撮影されて機密情報が流出したときの流出元を特定する。

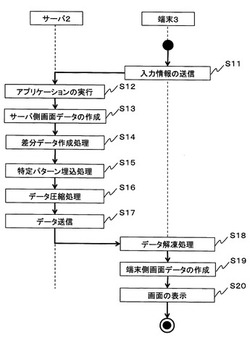

【解決手段】端末3は、入力情報をサーバ2に送信する(S11)。サーバ2は、アプリケーションを実行し(S12)、サーバ側画面データを作成し(S13)、前回作成したサーバ側画面データと今回作成したサーバ側画面データとを比較し、今回作成したサーバ側画面データの中で差のある部分のみを差分データとして作成し(S14)、差分データに対し、特定パターンを埋め込み(S15)、特定パターンを埋め込んだ差分データを圧縮し(S16)、端末3に送信する(S17)。端末3は、データを受信して解凍し(S18)、前回の端末側画面データに対して、解凍して得た差分データを更新して端末側画面データを作成し(S19)、表示装置37に表示する(S20)。

(もっと読む)

幾何学変換を行うためのシステム、方法及び記憶媒体

【課題】簡易かつ高速に信号の幾何学的変換を行う方法及びシステムを提供すること。

【解決手段】一実施例における本システムは、入力画像における画素のウィンドウを構成する入力パッチを有する。本システムは変換セレクタをさらに有し、該変換セレクタは、制御データを生成し、処理する現在の画素の位置に基づいて幾何学変換マッピングを制御する。一実施例における本システムはハードウェア幾何学変換エンジンを有し、その幾何学変換エンジンにより、制御データを用いて、入力ウィンドウから出力画素へパスを切り替えることで、幾何学変換マッピングを実行する。一実施例における本システムは補間器をさらに有し、その補間器は、幾何学変換エンジンからの複数の出力及び制御データを利用して、入力ウィンドウ中の複数のパスを切り替えることで、補間された幾何学変換マッピングを行う。

(もっと読む)

画像形成装置、画像形成方法、および画像形成プログラム

【課題】ページ番号の小さいページの処理が優先的に完了するように並列処理を実行して画像の出力待ちの状態を低減し、処理の高速化を実現することができる画像形成装置、画像形成方法、および画像形成プログラムを提供する。

【解決手段】PDL処理部での処理をDL生成部31によるDLデータ生成処理(前処理)と描画部32によるバンド描画処理(後処理)とに分け、PDL処理管理部43の制御部431が、DL生成部31を起動してDLデータ生成処理を実行させる場合には、複数ページ分の処理に複数のCPUコアを割り当てて複数ページ分のDLデータの生成を並列処理で実行させながら、DLデータの生成後に描画部32を起動して描画処理を実行させる場合には、ページ番号の小さいページの処理に複数のCPUコアを優先的に割り当てて、当該ページの複数バンドの描画を並列処理で実行させる。

(もっと読む)

画像処理装置、画像処理方法、コンピュータープログラム

【課題】画像処理に関する技術を提供する。

【解決手段】表示画像に対応する画像データを、表示画像を縦横それぞれ複数に分割した各部分画像に対応する画像データ毎に処理する画像処理装置であって、部分画像に対応する画像データを入力する入力部と、各部分画像に対応して設けられ、部分画像に対応する画像データを受け取り、画像処理を行う複数の画像処理部と、複数の画像処理部が処理した各部分画像に対応する画像データを、並列的に、走査方向に沿って順次入力することによって、表示画像に対応する画像データを入力する画像合成入力部と、順次入力される部分画像の画像データを順次記憶する記憶部と、表示画像の走査方向に沿って存在する複数の部分画像にそれぞれ対応する画像データを、まとめて1つの単位ブロックとして扱い、記憶部に順次記憶される画像データを、各単位ブロック毎に、並列的に所定の走査方向に順次出力する画像合成出力部とを備える。

(もっと読む)

画像処理装置及び画像処理方法

【課題】ダイレクトメモリアクセスを用いた画像処理の処理速度を向上させる。

【解決手段】メモリ10に書き込まれている画像処理パラメータ及び画像データを、DMAで読み込むとともに、読み込んだ画像データを画像処理パラメータにもとづいて画像処理する画像処理装置1であって、画像処理パラメータDMAC40は、メモリ10に書き込まれている画像処理パラメータのうち、リードDMAC50の画像データ読み込み処理に必要な位置パラメータを、他のパラメータよりも優先的にメモリ10から読み込んで第一レジスタ部31に設定するとともに、位置パラメータの設定の終了後、他のパラメータをメモリ10から読み込んで第二レジスタ部32に設定する構成とする。

(もっと読む)

画像処理装置、画像処理回路、及び画像処理方法

【課題】ブロック単位で処理を行う画像処理装置において、フィルタリング処理時間をより短くする。

【解決手段】原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理装置は、画素データを複数方向にシフト可能なレジスターを用いて、ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する。

(もっと読む)

画像形成装置およびその制御方法

【課題】 画像処理回路に接続されるデータバスの本数を減らすことができる画像形成装置およびその制御方法を提供する。

【解決手段】 画像処理用の複数の機能ブロックを選択的に設定可能に有するとともに、その機能ブロック用のデータバスを選択的に設定可能に有する画像処理回路を備え、この画像処理回路における機能ブロックの設定を指示するとともに、その機能ブロックの設定に対応するデータバスの設定を少なくとも1つのデータバスについては複数の機能ブロックに兼用として指示する。

(もっと読む)

画像処理装置、プログラム及び画像処理方法

【課題】複数の演算部を用いてラスタライズ処理を実行する際のメモリ使用量の増大を抑えること。

【解決手段】ページ記述言語データに基づいてバンド単位で生成された中間データをラスタライズ処理する場合に使用されるワーク領域を有するRAM11と、複数のコアを有し、中間データに対して行うラスタライズ処理を複数のコアを用いて実行する制御部10と、を備えた画像処理装置であって、制御部10は、コアの数に基づいて各中間データを構成するバンドを複数に分割して複数の分割領域を生成し、コア毎にラスタライズ処理を行う分割領域を割り当てる画像処理装置。

(もっと読む)

グループ撮像検査のデータ処理

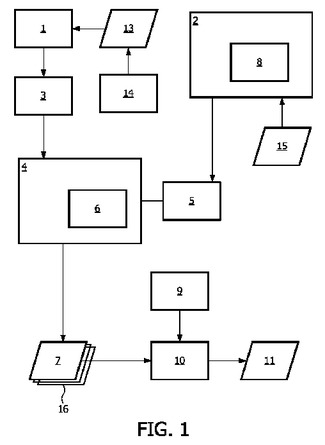

マルチ被写体ボリュームを処理するシステムが、同時にスキャンされる複数の被写体を含む入力ボリューム画像データセット13を受信するボリューム入力部1を有する。メタデータ入力部2は、被写体の個別の1つに関するメタデータ15を受信する。被写体ファインダー3は、入力ボリューム画像データセット13の複数の部分を特定する。各部分は、被写体の1つを含む。ボリューム画像データセット生成器4は、複数の別々のボリューム画像データセット16を生成する。各別々のボリューム画像データセット7は、入力ボリューム画像データセットの部分の1つを含む。メタデータハンドラ5は、被写体を含む部分を備える別々のボリューム画像データセット7と、被写体に関するメタデータ15とを関連付ける。  (もっと読む)

(もっと読む)

信号処理装置、信号処理システム、遊技機

【課題】インタラクティブな遊技機、ゲーム機などの画像展開と音声再生、役物の動作とのタイミング等を総合的に制御できる信号処理装置を提供する。

【解決手段】グラフィックス用ロジック6と音声用ロジック7とを同じ統合化LSI5に搭載して命令体系を連携する。前記グラフィックス用ロジック6は、上位CPU10の命令を解読する命令解読部20と、画像デコード部22とを備え、音声用ロジック7における音声デコード部21は命令解読部20を介した命令により動作する。

(もっと読む)

画像処理デバイス排他制御装置、制御方法、プログラム及び記録媒体

【課題】画像処理デバイス制御において不整合が起きない排他制御を行う装置を提供する。

【解決手段】1以上のタスクで画像データに対して画像処理を行う画像処理デバイスへのアクセス要求が競合する場合の画像処理デバイス制御であって、1以上のタスクからアクセスされる、デジタル画像データに対して画像処理を行う画像処理デバイスと、画像処理デバイスへのアクセスを制御する画像処理デバイス制御手段と、1スレッドを実行するタスク単位で、複数のタスクを非同期で実行するCPUと、1以上のタスクで前記画像処理デバイス制御手段による画像処理デバイスアクセス要求が競合する場合に、前記画像処理デバイスごとに画像処理デバイスアクセスの競合を防止する排他制御手段と、を有する。

(もっと読む)

データ転送制御装置、データ転送システム、及びデータ処理システム

【課題】記憶資源を効率的に使用する。

【解決手段】各々が転送されたデータを転送された順に処理する画像処理部(第1〜第4画像処理部11〜14)の各々に対応させて設けられデータを一時的に記憶するための複数の中間バッファ32と、各々が画像処理部の各々に対応するように定められた互いに重複しない複数の記憶領域を備えた単一の記憶装置50の記憶領域から予め定められた順にデータを読み出し上記対応させて設けられた中間バッファ32に書き込む複数のDMA制御部33と、各々が画像処理部の各々に対応させて設けられ対応する画像処理部からの要求に応じて該画像処理部に対応する中間バッファ32に書き込まれたデータを書き込まれた順に読み出して対応する画像処理部に転送する複数の画像処理部I/F31と、複数のDMA制御部33の各々に対して排他的に記憶装置50からデータを読み出す権利を付与して排他制御を行う排他制御部40とを設ける。

(もっと読む)

画像処理装置

【課題】複数のプロセッサ要素を1次元に結合してなる分散メモリ型プロセッサアレイを備えた画像処理装置により、1行の画素数がプロセッサ要素数より多い画像を処理する場合の効率向上を図る。

【解決手段】画像処理プロセッサ100は、複数個のプロセッサ要素をリング状に1次元に結合してなる分散メモリ型プロセッサアレイ120を備え、処理対象の画像の1行の画素数がプロセッサ要素数より大きいときに、該画像を折り畳んでプロセッサ要素のローカルメモリに格納する。各プロセッサ要素のメモリアクセス制御部は、ローカルメモリアクセスにより画像の所定の行に含まれる画素に対する読出要求があった際に、ローカルメモリに格納された、上記所定の行の全ての画素をローカルメモリから読み出すことが可能である。なお、ローカルメモリアクセスは、プロセッサアレイ120内部に生じるメモリアクセスである。

(もっと読む)

電子機器及び電子機器システム

【課題】容易に表示画像を変形させることができる電子機器を提供する。

【解決手段】携帯型の電子機器4であって、画像を表示する表示部10と、前記電子機器の傾きを検出する検出部40と、前記検出部において検出した検出値に基づいて、前記表示部に表示された前記画像の前記画像データを変形する画像制御部44と、前記画像制御部において変形した前記画像データを外部機器6に対して送信する通信部50とを備える。

(もっと読む)

画像処理装置、および画像処理装置の動作方法

【課題】画像データの転送によって生じる不具合を軽減させることが可能な技術を提供する。

【解決手段】画像処理装置1Aは、出力画像における所定画素の、入力画像上での対応位置を取得する相対座標取得部301と、対応位置の位置情報を記憶する第1記憶手段と、入力画像における入力画素の画素値を順次に読み出させる読出制御部303と、読み出された入力画素の画素値を入力とし、入力された入力画素の中から、入力画素による格子点の組を編成する編成手段と、上記位置情報に基づいて、所定画素の画素値の算出に用いる対応位置周辺の周辺画素の画素値が読み出されたか否かを判定する判定手段と、周辺画素が読み出されたと判定された場合に、格子点の組を構成する画素の画素値を、所定画素に関する周辺画素の画素値として記憶するローカルメモリと、上記周辺画素の画素値を用いた補間によって、所定画素の画素値を算出する画素値算出部306と備える。

(もっと読む)

画像処理装置、画像形成装置、及び画像処理プログラム

【課題】複数の画像処理手段の画像処理が並列に実行される時間を長くする。

【解決手段】待機状態から起動した後は前段のモジュールから単位データ量ずつ画像データを取得して画像処理を行い、画像処理後の画像データ又は処理結果を後段のモジュールへ出力する機能を備え、前段から単位データ量の画像データの取得に失敗した場合は待機状態となり、実行する画像処理の種類又は内容が互いに異なる複数の画像処理モジュール38と、前段のモジュールからの画像データが書き込まれ、該書き込まれた画像データが後段のモジュールによって読み出されるバッファ40Aを備えたバッファモジュール40とが連結された画像処理部において、バッファ40Aに書込まれた画像データのデータ量がバッファモジュール40に連結された画像処理モジュール38の各々に応じて定まるデータ量となった場合に後段の像処理モジュール38を起動する。

(もっと読む)

画像処理装置、仮想マシン間の動作モジュール実行制御方法、及び動作モジュール実行制御プログラム

【課題】仮想マシン間のRMI通信対応における通信I/Fの追加・変更の作業負荷を軽減できる画像処理装置、仮想マシン間の動作モジュール実行制御方法、及び動作モジュール実行制御プログラムを提供する。

【解決手段】画像処理装置100は、標準機能と標準機能を利用した拡張機能とが異なる仮想マシン211,212上で動作する装置であって、標準機能を実現する複数の動作モジュール30と、各仮想マシン21上で動作し、複数の動作モジュール30に対して共通の仮想マシン間通信を行う通信インタフェース部411,412と、を有し、通信インタフェース部40が、動作モジュールインタフェース実現部52を生成する生成手段51を有し、仮想マシン211,212それぞれに生成された一対の動作モジュールインタフェース実現部521,522を介して、仮想マシン間通信により、仮想マシン21上の動作モジュール30の実行を制御し、拡張機能を実現することを特徴とする。

(もっと読む)

SIMD型マイクロプロセッサおよびSIMD型マイクロプロセッサのデータ転送方法

【課題】複数の画素データフォーマット変換を効率よく、かつ、回路規模の増大を抑えるように構成したSIMD型マイクロプロセッサおよびSIMD型マイクロプロセッサのデータ転送方法を提供する。

【解決手段】SIMD型マイクロプロセッサ1に、一列に並べられた複数のPE10を接続する転送バス20と、その転送バス20を分割するスイッチ21と、を備え、各PE10には、A1変換レジスタ13、A2変換レジスタ14と、B1変換レジスタ15、B2変換レジスタ16と、A1変換レジスタ13、A2変換レジスタ14の格納内容を転送バス20に出力する入出力回路22、23と、転送バス20上のデータをB1変換レジスタ15、B2変換レジスタ16に格納する入出力回路24、25と、入出力回路22、23、24、25及びスイッチ21をPEコントロール部30からのデータにより制御するデコーダ26と、を備える。

(もっと読む)

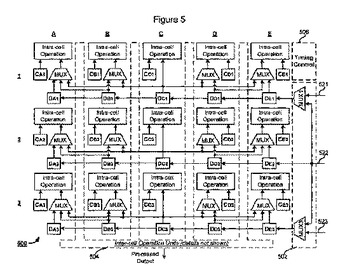

画素速度での画像処理のための方法および装置

本発明の実施形態は、処理演算が、画素の新しいラインまたはフレームに移行するときでも、メモリフェッチおよび画素出力の一定速度を維持するために、2−D画像処理において、改良されたタイミング制御を提供する。本発明に従って改良されたタイミング制御は、現在のライン上のエッジ画素ブロックの新しい列が、複製される、またはゼロに設定される間に、次のラインまたはフレームの第1の画素ブロック内の画素データの新しい列をプリフェッチすることによって、アイドルメモリ帯域幅を利用するため、着信画素速度と発信画素速度との間の1対1関係は、付加的なクロックサイクルまたはメモリ帯域幅を伴うことなく維持される。現在のライン上のエッジ画素ブロックが、処理されることに伴って、次のラインまたはフレームの第1の画素ブロック内のデータは、余剰クロックサイクルまたは余剰メモリ帯域幅を伴わずに、計算のための準備ができる。  (もっと読む)

(もっと読む)

イメージプロセッサ及びそれを含む電子装置及びイメージプロセッシング方法

【課題】多様な解像度のマルチメディアソースに対するイメージプロセッシング能力を向上させることができるイメージプロセッサを提供する。

【解決手段】イメージプロセッサ100は、ローテーションブロック120と、ラインバッファブロック130と、スケーリングブロック140と、を含む。前記ローテーションブロックは、ローテーション情報に基づいて生成されるアドレスに基づいて、再配列されたソースイメージのピクセルデータをメモリから受信して出力することができる。前記ラインバッファブロックは、前記ローテーションブロックから出力される再配列されたピクセルデータを臨時に保存することができる。前記スケーリングブロックは、前記ラインバッファブロックから出力される再配列されたピクセルデータを水平及び垂直方向にスケーリングすることができる。

(もっと読む)

81 - 100 / 552

[ Back to top ]