Fターム[5B060CA03]の内容

Fターム[5B060CA03]の下位に属するFターム

連続アクセスの高速化 (134)

Fターム[5B060CA03]に分類される特許

1 - 20 / 48

情報処理装置及び情報処理方法

【課題】バスマスタがDRAMによるプリチャージ動作を制御するためのより低コストな方法を提供し、これによってDRAMへのアクセス速度を向上させる。

【解決手段】第1のアドレスへのアクセス後、第2のアドレスへのアクセス前に、DRAMにおいてプリチャージ動作が必要であるか否かを判定する。プリチャージ動作は必要ないと判定した場合には第1のアドレスに対するアクセス後にオートプリチャージを行わないことを指定する命令を、プリチャージ動作が必要であると判定した場合には第1のアドレスに対するアクセス後にオートプリチャージを行うことを指定する命令を、バスマスタがメモリコントローラに対して要求するバーストアクセスの種類を示す信号を用いてメモリコントローラへと送信する。

(もっと読む)

記録装置及びその動作の制御方法

【課題】記録装置が省電力モードからの復帰する時に、SDRAMに関する不要な初期化処理を省略して高速な復帰処理を行うことである。

【解決手段】動作状態から停止状態に遷移する際、SDRAMをセルフリフレッシュ動作させるかどうかの情報をフラグに保持する。停止状態からの復帰時にフラグを参照し、停止状態においてSDRAMがセルフリフレッシュ動作を行っていた場合は初期化処理を省略する。

(もっと読む)

電子機器、及び画像処理装置

【課題】ページミスを発生させるアクセス要求よりも他のアクセス要求を優先させて、レイテンシーを低減させる。

【解決手段】調停回路は、アクセス要求を受け付けた場合、当該アクセス要求が、当該アクセス要求よりも前にメモリーコントローラーに出力した他のアクセス要求であって処理が終了していないアクセス要求と、ページミスを発生させないかどうかを判定する。当該アクセス要求がページミスを発生させる場合は、当該アクセス要求の出力を所定期間停止させ、その後のページミスを発生させないアクセス要求を、優先的に出力する。

(もっと読む)

データ転送システム

【課題】動作効率を向上できるデータ転送システムを提供する。

【解決手段】1つの実施形態によれば、第1の速度でデータをそれぞれ転送する複数のラインを有するバスと、前記バスに接続された複数のマスタ装置と、前記バスに接続されたスレーブ装置とを備え、前記スレーブ装置は、前記バスにそれぞれ接続され、前記バスを介して前記マスタ装置から転送指示をそれぞれ前記第1の速度で受信する複数のスレーブインターフェースと、前記複数のマスタ装置の間における処理内容の関連性に依存した順番で前記複数のマスタ装置が優先順位付けされた優先順位情報に従って、前記複数のスレーブインターフェースで受信した転送指示の処理順を決定する調停部と、前記調停部により決定された処理順に従い、転送指示に応じた外部との間のデータ転送処理を前記第1の速度より速い第2の速度で行う処理部とを有することを特徴とするデータ転送システムが提供される。

(もっと読む)

半導体記憶装置、及び記憶媒体

【課題】ガベージコレクション処理による処理負荷を軽減し、ガベージコレクション処理の処理時間を短縮する。

【解決手段】フラッシュメモリ10は、予め定められたデータサイズ領域を示すページ単位でデータを書き込み可能な不揮発性記憶部11と、不揮発性記憶部11の指定された領域であって、複数のページを含む該指定された領域における有効データを一時記憶する記憶部12と、不揮発性記憶部11のページに有効なデータがあるか否かを示すアドレスマップ情報に基づいて、指定された領域における有効データを記憶部12に記憶させた後に、記憶部12に記憶された有効データを連続したページに書き込むガベージコレクション処理、及びガベージコレクション処理によって変更されたアドレスマップ情報を出力する処理を実行するコントロールロジック部13とを備える。

(もっと読む)

記憶装置、ホスト装置、回路基板、液体容器及びシステム

【課題】アクノリッジを一括して送受信し、且つ、書き込み処理時間を短縮することができる記憶装置、ホスト装置、回路基板、液体容器及びシステム等を提供すること。

【解決手段】記憶装置100は、バスBSを介して接続されるホスト装置400との通信処理を行う制御部110と、ホスト装置400からのデータが書き込まれる記憶部120と、記憶部120のアクセス制御を行う記憶制御部130とを含む。制御部110は、バスBSに接続される複数の記憶装置100に対するホスト装置400によるデータの書き込み期間の終了後に、ホスト装置400からの複数の記憶装置100に対するブロードキャストのアクノリッジ返信要求情報を受信し、且つ、自身の記憶部120にデータが正常に書き込まれている場合に、ホスト装置400に対してアクノリッジを返信する。

(もっと読む)

メモリシステム

【課題】複数の不揮発性半導体メモリを有するメモリシステムで発生する消費電力のピークを低く抑えることができる。

【解決手段】チップ1は、コントローラ20から第1制御信号を受け取ると、第1動作のうちの第1サブ動作を実行して、第1動作を中断する。コントローラ20は第1動作が中断されると、第2制御信号をチップ2に送信する。第2制御信号を受け取ると、チップ2は第2動作のうちの第3サブ動作を実行して、第2動作を中断する。コントローラ20は第2動作が中断されると、第3制御信号をチップ1に送信する。第3制御信号を受け取ると、チップ1は第1動作を再開し、第2サブ動作を実行する。コントローラ20は第2サブ動作が終了すると、第4制御信号をチップ2に送信する。第4制御信号を受け取ると、チップ2は第2動作を再開し、第4サブ動作を実行する。

(もっと読む)

情報処理装置、情報処理装置の制御方法、及び、プログラム

【課題】記憶容量や種類が異なる複数のストレージの組み合わせによるミラーリング制御を実現可能にするとともに、複数の記憶装置の全空間を使用可能にする。

【解決手段】複数のストレージ22,23を備える記憶部を有する画像形成装置において、操作部からの設定指示に応じて、ストレージコントローラ部21が、ストレージ22,23に対してミラーリング領域を設定する。コントローラ部21は、データをストレージ22,23に記憶する場合、記憶すべきデータが重要度の高いデータであるか判定する。ストレージコントローラ部21は、重要度の高いデータと判定されたデータをストレージ22,23のミラーリング領域に格納し、重要度の低いデータと判定されたデータをストレージ22の非ミラーリング領域に格納するように制御する。

(もっと読む)

メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】アクセス要求により頻繁に指定される論理ブロックに対応する物理ブロックへのアクセスを効率的に行う。

【解決手段】アクセス要求により、そのときまでに指定された論理ブロックについて、その論理ブロックに対応する物理ブロックにアクセスするための論理ブロック情報が所定個数保持される。この論理ブロック情報の保持では、優先順位の高い論理ブロック情報が優先順位の低い論理ブロック情報より優先される。この優先順位の管理では、アクセス要求により頻繁に指定される論理ブロックに対応する論理ブロック情報の優先順位が高くなる。アクセス要求を受けたときに、そのアクセス要求により指定された論理ブロックに対応する論理ブロック情報が保持されていれば、その保持されている論理ブロック情報に基づいて指定された論理ブロックに対応する物理ブロックへのアクセスが行われる。

(もっと読む)

半導体集積回路、及びリクエスト制御方法

【課題】論理規模を増大させることなく、複数のバスマスタからのリクエスト発行数を増加させる。

【解決手段】本発明による半導体集積回路100は、複数のキュー330と、複数のバスマスタ1、2から発行されたリクエストのアクセス先のアドレスに基づいて、リクエストを複数のキュー330のいずれかに振り分けるリクエスト振り分け部301と、複数のキュー330から選択したキュー内のリクエストを、外部デバイス5に発行するリクエストセレクタ302とを具備する。

(もっと読む)

メモリ制御システム

【課題】CPUからメモリへのアクセス時間を短縮する。

【解決手段】内部メモリ206は外部メモリ203に格納されているデータの複製を所定サイズのデータブロック単位で格納している。読み出し対象データの複製が内部メモリ206に格納されていない場合に、メモリアクセス制御プログラム210は、読み出し対象データを外部メモリ203から読み出し、読み出した読み出し対象データをCPU201の読み出し要求元に供給し、その後、メモリアクセス制御プログラム210は、読み出し対象データを含むデータブロックを外部メモリ206から読み出し、DMAコントローラ703を用いて、読み出したデータブロックを内部メモリ206に格納する。

(もっと読む)

携帯電話

【課題】インターネット端末として利用可能な携帯電話を提供する。

【解決手段】制御部(8)は、電源投入時には、ファイルストレージ用フラッシュメモリ(13)から必要なプログラムを読出してRAM(12)へ転送し、RAMを命令メモリとして利用して処理を実行する。インターネット接続時には、制御部は、ファイルストレージ用フラッシュメモリから所定のプログラムを読出してRAM(12)へ転送して処理を実行する。インターネットからの受信データは、制御部の制御の下に、RAM(12)に格納された後ファイルストレージ用フラッシュメモリに格納する。

(もっと読む)

メモリ制御回路

【課題】実際のシステムにメモリデバイスを組み込んだ際に利用されないメモリアドレス空間を利用し、上記で述べたようなページミス時のアクセスペナルティを軽減する。

【解決手段】メモリ制御回路は、メモリデバイスへのアクセス種別およびアクセスアドレスを判別し適切なメモリデバイスに対してアクセスコマンドを発行させるコマンド振り分け手段と、実際のメモリデバイスにアクセスコマンドを発行させるコマンド発行手段とを備える。コマンド振り分け手段はメモリアクセスがライトであった場合には、アドレス変換手段が示すデバイスの物理アドレスに対しライトコマンドを発行する。メモリアクセスがリードであった場合には前記アドレス変換手段が示す物理アドレスの状態を確認して最適なデバイスに対してリードコマンドを発行する。

(もっと読む)

メモリコントローラおよびデータ処理装置

【課題】複数のメモリアクセスリクエスタからのリクエストでも、バスの使用効率を高めるためのグループ化が可能なメモリコントローラおよびデータ処理装置を提供する。

【解決手段】リクエストキュー22は、複数のメモリアクセスリクエスタから受信したリクエストを格納する。併合部31は、リクエストキュー22内のリクエストのうち、DDR2−SDRAMにおける1回の読出しサイクルまたは書込みサイクルでアクセス可能なリクエストを併合する。メモリインタフェース部27は、リクエストに従って、DDR2−SDRAMに対してアクセスを行ない、併合された複数のリクエストに対するDDR2−SDRAMのアクセスを一括して行なう。

(もっと読む)

リクエスト順序制御システム、リクエスト順序制御方法およびリクエスト順序制御プログラム

【課題】リクエストを受け付けてから後続リクエストの処理が完了するまでの時間を短縮することを課題とする。

【解決手段】システムボード1では、IOC10が、先行リクエストの種別または後続リクエストの種別に応じて、リクエストの順序制御をIOC10が担当するかCPU20が担当するかを判定する。そして、IOC10が、リクエストの順序制御をCPU20が担当すると判定された場合には、先行リクエストに続いて、後続リクエストをCPU20に送信する。そして、CPU20が、先行リクエストをメモリ30に送信し、先行リクエストの処理が完了した後に、後続リクエストをメモリ30に送信するように順序を制御する。

(もっと読む)

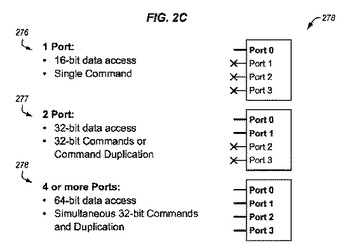

シリアルポートメモリ通信の待ち時間および信頼性を改善するための方法およびシステム

メモリ待ち時間を短縮するための方法、装置およびシステムが開示される。一実施形態では、ホストコンピュータシステムとメモリとの間のデータを、複数の時間間隔にわたって、メモリでポートまたはポート群を介して通信し、このホストコンピュータはメモリと連結される。さらに、データに関連したコマンドを、単一の時間間隔にわたって、ホストコンピュータシステムとメモリとの間でポートまたはポート群を介して通信する。  (もっと読む)

(もっと読む)

複数のデバイスへ同時書き込み操作を行うことにより高まるフラッシュメモリデバイスにおけるメモリ性能

【課題】読み出しおよび書き込み操作を行う際にかかる時間を短縮するために、非揮発性メモリをセクタフォーマットで組織化されたデジタル情報の記憶用に採用し、それによりシステムの全体的な性能を上げ、同時にこのデジタルシステムの製造経費を削減する、デジタルシステムを提供する

【解決手段】コントローラはセクタ単位に構成された情報を転送し、各セクタはホストと不揮発性メモリバンクとの間にユーザデータ部分およびオーバーヘッド部分を含み、2つの不揮発性メモリデバイス内の同じセクタに関連する2バイトのセクタの記憶および読み出しを同時に行う。各不揮発性メモリデバイスは、メモリロケーションの行によって規定され、ここで、少なくとも2つの半導体デバイスの対応する行が、その内部に2セクタの情報を、不揮発性メモリデバイスのメモリ行の1つに維持された2つのセクタに関連するオーバーヘッド情報と共に維持する。

(もっと読む)

メモリ制御装置、半導体試験装置およびメモリ制御方法

【課題】リードモディファイライトの動作を高速に行うことを目的とする。

【解決手段】DRAM1に対してリードモディファイライトの制御を行うメモリ制御装置であって、DRAM1にデータを記憶するときに、このデータのうちリードモディファイライトの対象となるデータと同一のデータの一部または全部を記憶するデータ記憶部10と、データ記憶部10に記憶されたデータを読み出して変更を行い、DRAM1に書き込みを行うデータ処理部9と、を備えている。予めデータ記憶部10にリードモディファイライトの対象となるデータを書き込むことで、リードモディファイライト処理を行うときには、データ記憶部10からのデータを変更処理することが可能になる。これにより、DRAM1からのデータ読み出しがなくなり、リードモディファイライトの処理が高速になる。

(もっと読む)

ブート方式

【課題】キャッシュ方式によって行っていたデータの先読みを、機能的なグループ単位での先読み方式とし、効率化、及びブート時間の短縮を図る。

【解決手段】起動時あるいは処理内容の変更時に、DMA装置109によって、プロセッサ101を介さずに、外部メモリ113から、プロセッサ101に接続された内部メモリ105にデータを読み込むことによって、プロセッサ101が所望の処理を開始するプロセッサのブート方式において、データを格納するデータ分割格納手段と、必要とする外部メモリ113におけるデータのブロックのアドレスと、格納する内部メモリ105のアドレスの関係を記述した変換テーブル107によって、外部メモリ113から内部メモリ105への読み込み処理を行う変換テーブル手段と、から成るブート方式とする。

(もっと読む)

データストリーム処理装置

【課題】連続的なデータストリームを処理するためのパラメータを有効に高速メモリに蓄えて利用するデータストリーム処理装置を提供する。

【解決手段】連続的なデータストリームを順次処理する処理手段(処理部5)と、データストリームを処理するためのパラメータが記憶され処理手段の処理する個々のデータに応じてランダムにアクセスされる記憶手段とを備え、記憶手段には、処理手段が現在処理しているデータストリームを処理するための現パラメータと、次のデータストリームを処理するための次パラメータとが順次切り替えて記憶される少なくとも2つの記憶領域(メモリ3A、3B)が設けられる。

(もっと読む)

1 - 20 / 48

[ Back to top ]