Fターム[5B060CB00]の内容

メモリシステム (7,345) | ロード/ストア制御 (453)

Fターム[5B060CB00]の下位に属するFターム

ロードバッファ/ストアバッファ制御 (270)

データ修飾を伴うロード/ストア (51)

ロードとストア競合処理 (34)

同一アドレスに対するロードとストア (19)

Fターム[5B060CB00]に分類される特許

1 - 20 / 79

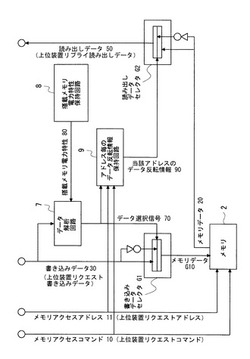

記憶装置および記憶装置制御方法

【課題】消費電力の低減を図ることが可能な記憶装置を提供する。

【解決手段】初期化時の予備テストとして'0'および'1'の試験データをメモリ2に書き込み、書き込み時点から一定時間経過後のそれぞれのメモリ2の温度を比較した結果を搭載メモリ電力保持回路8に搭載メモリ電力特性80として保持し、以降、メモリ2にデータを書き込む際に、データ解析回路7にて書き込みデータの'0'と'1'との個数を抽出して、保持した搭載メモリ電力特性80に基づき書き込みデータをそのまま書き込むかまたは'0'と'1'とを反転した反転データとして書き込むかを判別し、判別した結果をデータ選択信号70として出力し、書き込みデータセレクタG1にて、書き込みデータの'0'と'1'とを反転させた反転データを生成した後、出力されたデータ選択信号70に基づき書き込みデータそのままかまたは前記反転データかのいずれかを選択してメモリ2に書き込む。

(もっと読む)

メモリコントローラ

【課題】プロセッサにて処理されるデータが格納されるメモリの容量を削減する。

【解決手段】メモリコントローラ2は、メモリ領域RBのアドレスBnに書き込みデータYを書き込むようにプロセッサ1からの書き込み要求を受け取ると、メモリ領域RAのアドレスAmから読み出すようにプロセッサ1から指示された読み出しデータXと、メモリ領域RBのアドレスBnに書き込むようにプロセッサ1から指示された書き込みデータYが一致するかを判定し、それらの読み出しデータXと書き込みデータYが一致する場合、書き込みデータYをメモリ領域RBのアドレスBnに書き込まないようにする。

(もっと読む)

メモリシステム、コントローラ、およびメモリシステムの制御方法

【課題】トリム要求によりセクタ単位で不要であることが通知された領域について、フラグ用の追加記憶領域を要さずに不要か否かの情報を保持することが可能なメモリシステムを提供する。

【解決手段】実施形態のメモリシステム2は、不揮発性メモリ6と、ホスト1が指定する論理アドレスと前記不揮発性メモリ上での物理アドレスとの対応を管理単位毎に保持する論物変換テーブルを備えた記憶手段4を備える。メモリシステム2は、前記管理単位より小さいデータ量を単位として論理アドレスの削除領域を指定した削除通知を前記ホスト1から受け取った場合に、当該削除領域に含まれる前記管理単位に満たない領域と前記論物変換テーブルにおいて対応する物理アドレスの前記不揮発性メモリ6上の領域に所定のデータパターンを書き込むコントローラ3を備える。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】ブロック間転送の頻度を低減し、ブロック間転送に基づくアクセス処理の効率低下を抑制する。

【解決手段】書き込み先ブロックとして管理されている物理ブロック内の物理ページに、ホストシステムから与えられるデータが書き込まれる。物理ブロック内の無効データが格納されている物理ページのページ数がカウントされ、当該ページ数が一番大きい物理ブロックが特定される。当該物理ブロックに格納されている有効データが、転送先ブロックとして管理されている物理ブロック内の物理ページに転送される。書き込み先ブロックとして管理されている物理ブロックと転送先ブロックとして管理されている物理ブロックは異なる物理ブロックが選択される。

(もっと読む)

フラッシュメモリの制御システム

【課題】複数のセクタを使用してデータを保存するとともに、常時一定量の書き込みデータをフラッシュメモリ内に確保しておくことができるフラッシュメモリの制御システムを提供する。

【解決手段】 複数のセクタを使用してデータの書き込みを行うフラッシュメモリの制御システムにおいて、

各セクタの状態を示す状態フラグに基づいてデータの書き込みを行う書き込み制御部を有することを特徴とする。

(もっと読む)

メモリシステム及びそのデータ転送方法

【課題】不揮発性メモリからの読み出し動作においてレイテンシを短縮する。

【解決手段】メモリシステム10は、データを格納する不揮発性メモリ11と、不揮発性メモリ11からのデータを一時的に格納するバッファ15と、バッファ15からのデータの誤りを訂正する訂正回路17と、訂正回路17からのデータを一時的に格納するバッファ18と、バッファ18からのデータを受けるバス20と、不揮発性メモリ11及びバス20間のデータ転送のための複数のコマンドを発行するコマンドシーケンサ群と、複数のコマンドをデコードし、データ転送を制御するための複数の制御信号を生成するコマンドデコーダ群と、誤り訂正不能による読み出しエラーが発生した場合に、CPU22に割り込みを発生する割込回路21とを含む。コマンドシーケンサ群は、割り込みが発生した場合でも、不揮発性メモリ11からのデータ転送を継続する。

(もっと読む)

データプロセッサ及びデータの管理制御方法

【課題】書き込み単位が消去単位よりも小さな不揮発性メモリを用いて頻繁にデータの書き換えを行う用途に少ないリソースで対応することができるデータプロセッサを提供する。

【解決手段】書き込み単位が消去単位よりも小さな複数の不揮発性メモリブロックにデータを記憶して管理するために、一対の主メモリブロックと、それよりも記憶容量の小さな副メモリブロックとを消去及び書き込みの対象とし、データを更新するときはデータ(Data#i)とその属性を示すデータヘッダ(Data_DH#i)とを副メモリブロックに順次書き込み、副メモリブロックの空き領域がなくなったとき、副メモリブロックのデータと一の主メモリブロックのデータとをデータヘッダを参照して最新の状態にマージし、マージされたデータを他の主メモリブロックに書き込み、当該一の主メモリブロックを消去して、データ保持に用いる主メモリブロックを交互に切換える制御を行う。

(もっと読む)

書き込み装置、書き込み方法、及び書き込みプログラム

【課題】フラッシュメモリの記憶領域に対する書き込み回数の平準化の程度を一層高めることで、フラッシュメモリの寿命を実質的に延長することができる、書き込み装置、書き込み方法、及び書き込みプログラムを提供すること。

【解決手段】フラッシュメモリ4における連続する記憶領域に順に情報を書き込む書き込み装置1であって、フラッシュメモリ4に情報を書き込む場合、当該フラッシュメモリ4において情報が最後に書き込まれた記憶領域を特定し、当該特定した記憶領域の次の記憶領域から順に、情報を連続して書き込みが可能な空き記憶領域を検索する検索部3aと、この検索部3aによって検索された空き記憶領域に対応する記憶領域に情報を書き込む書き込み部3bとを備える。

(もっと読む)

記憶装置

【課題】迅速な処理でウェアレベリングを実現する記憶装置を提供すること。

【解決手段】不揮発性メモリ52は、アドレスが付されたブロックを複数有し、当該複数のブロックに当該ブロックの数よりも少ない数のユーザデータを記憶するユーザデータ領域52Aと、ユーザデータ領域52Aへのユーザデータの記憶を制御するデータを含む管理データを記憶する管理データ領域52Bとを備え、管理データ領域52Bは、制御部により最も新しく記憶されたユーザデータが記憶されているユーザデータ領域52Aのブロックに付されているアドレスを管理データとして記憶するアドレス記憶部521Bを有し、制御部は、新たにユーザデータを記憶させる場合、アドレス記憶部521Bに記憶されたアドレスより大きいアドレスが付されたユーザデータ領域52Aのブロックにユーザデータを記憶させた後、当該ブロックに付されたアドレスをアドレス記憶部521Bに記憶させる。

(もっと読む)

メモリシステム

【課題】2値領域と多値領域との間のデータ転送を効率的に行う。

【解決手段】メモリシステム30は、ページ単位で書き込みが行われ、かつ、1ビットを記憶単位とする第1の記憶領域と、nビット(nは2以上の整数)を記憶単位とする第2の記憶領域とを有する不揮発性メモリ32と、第1の記憶領域から読み出された読み出しデータと、外部から入力された入力データとを結合してnページからなる書き込みデータを生成し、この書き込みデータを第2の記憶領域に書き込む制御部31とを含む。

(もっと読む)

電子機器

【課題】電子機器では、フラッシュメモリなどの不揮発性半導体メモリを電子機器の記憶部として実用可能にすることが求められている。

【解決手段】電子機器1は、データ書込み処理において既に書込まれたデータに対する上書きが禁止されている不揮発性半導体メモリ16を有し、実データおよび当該実データに対応した管理データを記憶する第1記憶部53と、データ書込み処理において任意の値へのデータ上書きが可能な第2記憶部54と、第1記憶部53に対するデータアクセスを制御する制御部52とを有する。制御部52は、第1記憶部53に記憶されている管理データを、第2記憶部54にコピーし、第2記憶部54に記憶されている管理データを参照して、第1記憶部53の実データにアクセスする。

(もっと読む)

半導体記憶装置

【課題】不揮発性半導体記憶素子内のブロックの消去回数を減少させるとともに、書き込み効率の向上を実現する。

【解決手段】コントローラ10は、複数のデータを第一の単位で第一の記憶領域11に記憶する第一の処理と、第一の記憶領域11から出力されるデータを、第一の単位の二以上の自然数倍かつ第三の単位よりも小さい第一の管理単位で第四の記憶領域14に記憶する第二の処理と、第一の記憶領域11から出力されるデータを、第一の管理単位の二以上の自然数倍である第二の管理単位で第三の記憶領域13に記憶する第三の処理と、第四の記憶領域14内で最も古い割り当て順序を持つ第三の単位の領域を、第二の記憶領域12に移動する第四の処理と、第二の記憶領域12内の有効データを選択し、第二の単位の空き領域を持つ第三の単位の領域にコピーする第五の処理とを実行する。

(もっと読む)

データ記憶システムおよびデータ記憶方法、実行装置および制御方法、並びに制御装置および制御方法

【課題】データを書き込む処理速度を改善させる。

【解決手段】不揮発性メモリ13は、データの書き換え時に消去が必要であり、それぞれが独立して動作可能な複数のバンクBA1乃至BANを有し、各アドレスにランダムアクセス可能である。メモリコントローラ12は、不揮発性メモリ13の消去動作を隠すように、データの書き込みを制御する。そして、ホスト11は、ホストアプリケーションを実行し、不揮発性メモリ13のバンクを並列動作させる個数を示すインターリーブ数を決定して、メモリコントローラ12に通知する。さらに、ホスト11は、ホストアプリケーションが使用するホスト11でのアドレス空間、および、ホストアプリケーションにおいて設定されているアクセス単位をメモリコントローラ12に通知する。本発明は、例えば、不揮発性メモリにデータを記憶させるデータ記憶システムに適用できる。

(もっと読む)

半導体記憶装置

【課題】不揮発性半導体記憶素子内のブロックの消去回数を減少させるとともに、書き込み効率の向上を実現する。

【解決手段】コントローラ10は、複数のデータを第一の単位で第一の記憶領域11に記憶する第一の処理と、第一の記憶領域11から出力されるデータを、第一の単位の二以上の自然数倍である第一の管理単位で第二の記憶領域12に記憶する第二の処理と、第一の記憶領域11から出力されるデータを、第一の管理単位の二以上の自然数倍かつ第三の単位よりも小さい第二の管理単位で第四の記憶領域14に記憶する第三の処理と、第四の記憶領域14内で最も古い割り当て順序を持つ第三の単位の領域を、第三の記憶領域13に移動する第四の処理と、第三の記憶領域13内のデータを選択し、選択されたデータを第二の単位の空き領域を持つ第三の単位の領域にコピーする第五の処理と、を実行する。

(もっと読む)

半導体記憶装置

【課題】不揮発性半導体記憶素子内のブロックの消去回数を減少させるとともに、書き込み効率の向上を実現する。

【解決手段】コントローラ10は、複数のデータを第一の単位で第一の記憶領域11に記憶する第一の処理と、第一の管理単位で第四の記憶領域14に記憶する第二の処理と、第一の記憶領域11からのデータを、第二の管理単位で第五の記憶領域15に記憶する第三の処理と、第四の記憶領域14内で最も古い割り当て順序を持つ第三の単位の領域を、第二の記憶領域12に移動する第四の処理と、第二の記憶領域12内のデータを選択し、第二の単位の空き領域を持つ第三の単位の領域にコピーする第五の処理と、第五の記憶領域15内で最も古い割り当て順序を持つ第三の単位の領域を、第三の記憶領域13に移動する第六の処理と、第三の記憶領域13内のデータを選択し、第二の単位の空き領域を持つ第三の単位の領域にコピーする第七の処理とを実行する。

(もっと読む)

半導体記憶装置

【課題】不揮発性半導体記憶素子内のブロックの消去回数を減少させるとともに、書き込み効率の向上を実現する。

【解決手段】コントローラ10は、複数のデータを第一の単位で第一の記憶領域11に記憶する第一の処理と、第一の管理単位で第四の記憶領域14に記憶する第二の処理と、第一の記憶領域11から出力されるデータを、第二の管理単位で第三の記憶領域13に記憶する第三の処理と、第四の記憶領域14内の第三の単位の領域を選択し、選択された領域を第二の記憶領域12に移動する第四の処理と、第四の記憶領域14内のデータを選択して第二の単位の空き領域を持つ第三の単位の領域にコピーし、第三の単位の領域を第二の記憶領域12に割り当てる第五の処理と、第二の記憶領域12内のデータを選択し、選択されたデータを第二の記憶領域12において第二の単位の空き領域を持つ第三の単位の領域にコピーする第六の処理と、を実行する。

(もっと読む)

情報処理装置及びプロセッサ並びに情報処理方法

【課題】情報処理装置について、装置構成を複雑化させることなく、動作の高速化と高信頼性を実現する。

【解決手段】本発明の一例である情報処理装置1は、プロセッサ2と、プロセッサ2に使用される不揮発性メモリ3と、プロセッサ2から不揮発性メモリ3への書き込みが発生した場合に、書き込み位置の重複回数を抑えるために当該書き込み位置がずれるように書き込みアドレスを発生させるアドレス発生手段16と、書き込みの新しさを表わす順序情報19を発生させる順序発生手段17と、アドレス発生手段16によって発生された書き込みアドレスに対して、順序発生手段17によって発生された順序情報19を対応付けて、書き込み情報21を記憶する書き込み制御手段18とを具備する。

(もっと読む)

フラッシュメモリを備えた制御装置及びフラッシュメモリへのデータ書込み方法

【課題】メモリ領域を書込管理のために使用することなく、CPU内蔵型のフラッシュメモリの書込みの効率化を図ることができる、フラッシュメモリを備えた制御装置及びフラッシュメモリへのデータ書込み方法を提供すること。

【解決手段】書込み制御部4aは、フラッシュメモリ2の2以上のブロックを組み合わせて構成された組み合わせブロックの各アドレスに対してデータの書込みを行うもので、組み合わせブロックにデータを書込む際、組み合わせブロックのアドレスの中に初期状態のアドレスが存在する場合には、先頭のアドレスにデータを書込み、初期状態のアドレスが存在しない場合には、次順の書込み対象となるブロックを初期化し、当該初期化されたブロックのアドレスの中の先頭のアドレスにデータを書込む。

(もっと読む)

不揮発性メモリの自動書き換え中断方法と不揮発性メモリおよびマイクロコンピュータ

【課題】不揮発性メモリの自動書き換え処理が所定の時間内に自動で中断できるようにする。

【解決手段】不揮発性メモリ100において、コマンド解読部110が外部から入力されるコマンドを解読した結果により、書き換え制御部120は複数個の分割制御フローから構成される制御フローを実行し、メモリアレイ130の書き換えを制御する。書き換え制御部120は、1つの分割制御フローが完了する毎に制御フローを中断し、メモリアレイ130を読み出し可能な状態にする。

(もっと読む)

メモリコントローラ

【課題】プロセッサにて処理されるデータが格納されるメモリの容量を削減する。

【解決手段】メモリコントローラ2は、メモリ領域RBのアドレスBnに書き込みデータYを書き込むようにプロセッサ1からの書き込み要求を受け取ると、メモリ領域RAのアドレスAmから読み出すようにプロセッサ1から指示された読み出しデータXと、メモリ領域RBのアドレスBnに書き込むようにプロセッサ1から指示された書き込みデータYが一致するかを判定し、それらの読み出しデータXと書き込みデータYが一致する場合、書き込みデータYをメモリ領域RBのアドレスBnに書き込まないようにする。

(もっと読む)

1 - 20 / 79

[ Back to top ]