Fターム[5B060CC01]の内容

メモリシステム (7,345) | アクセスタイミング制御 (460) | タイミング信号制御 (406)

Fターム[5B060CC01]の下位に属するFターム

サイクル長制御、ウェイトサイクル制御 (23)

クロック制御(クロック選択、クロック切替) (133)

Fターム[5B060CC01]に分類される特許

1 - 20 / 250

演算装置

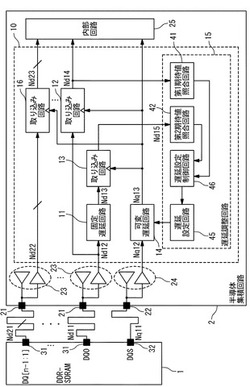

メモリインターフェース回路、および、そのメモリインターフェース回路の動作方法

【課題】メモリコントローラにおいて、DQとDQSのスキュー調整を行うためのパスの素子を最小限にとどめる。

【解決手段】データストローブ信号DQSを段階的に遅延させて遅延データストローブ信号Nq13を生成する可変遅延回路14と、データストローブ信号DQSの遅延値を設定する遅延調整回路15と、データ信号DQを、遅延調整回路15に供給するデータ供給回路とを具備するメモリインターフェース回路10を構成する。データ供給回路は、第1経路と第2経路とを備えるものとする。第1経路は、遅延データ信号Nd13を生成する固定遅延回路11と、遅延データストローブ信号Nq13に同期して遅延データ信号Nd13を取り込む第1データ取り込み回路13とを備える。第2経路は、第2データ取り込み回路12を備え、遅延データストローブ信号Nq13に同期してデータ信号Nd12を取り込む。

(もっと読む)

半導体装置

【課題】高速且つ低コストで、メモリ容量の拡張性を確保できる使い勝手の良い情報処理システムを提供する。

【解決手段】レイテンシを一定に保ち、高速且つ低コストで、メモリ容量の拡張性を確保できる使い勝手の良い情報処理システムである。情報処理装置、揮発性メモリおよび不揮発性メモリを含む情報処理システムを構成する。情報処理装置、揮発性メモリおよび不揮発性メモリは直列接続させ、接続信号数を少なくすることにより、メモリ容量の拡張性を保ちつつ、高速化を図る。情報処理装置はレイテンシを計測し、レイテンシの補正動作を行うことでレイテンシを一定に保つ。不揮発性メモリのデータを揮発性メモリへ転送させる際は、エラー訂正を行い、信頼性の向上を図る。これら複数のチップからなる情報処理システムを、各チップが相互に積層して配置され、ボールグリッドアレイ(BGA)やチップ間の配線技術によって接続された情報処理システム・モジュールとして構成する。

(もっと読む)

半導体装置

【課題】被制御チップの出力回路から制御チップの入力回路へ伝送されるデータ信号の位相を、入力回路に供給される同期信号の位相に一致させる。

【解決手段】半導体装置は、第1の被制御チップ110とそれと積層する制御チップ120を備える。第1の被制御チップは、同期信号に応じてデータ信号を出力する第1の回路117と、そのデータ信号を遅延同期信号に同期してデータ端子へ出力する入出力回路118と、出力回路を模した回路であって、遅延同期信号に同期してレプリカ信号を第1のレプリカ端子へ出力するレプリカ回路119とを含む。制御チップは、同期信号を出力し、データ信号を受ける第1の制御回路126と、同期信号を遅延させて遅延同期信号として出力する遅延調整回路130と、レプリカ信号の位相と同期信号の位相とを比較する位相比較回路128と、位相比較回路の比較結果に基づいて遅延調整回路の遅延量を制御する遅延制御回路129とを含む。

(もっと読む)

メモリシステムの書き込みタイミングを較正する方法および装置

【課題】メモリの書き込み動作の実行に必要な信号のタイミングを較正する手法を提供する。

【解決手段】メモリ制御装置が、書き込み−読み出し−検証の動作を実行してデータストローブ信号とクロック信号との間のクロックサイクル関係を較正する(308)ように構成されており、クロック信号に対するデータストローブ信号の遅延をクロック周期単位で変化させることを含む。メモリチップの位相検出器は、クロック信号、マーキング信号、およびデータストローブ信号を含む複数の信号をメモリ制御装置から受信し、マーキング信号は、クロック信号の中の特定のクロックサイクルをマーキングするパルスを含み、マーキング信号を用いて、クロック信号の中の特定のクロックサイクルに窓を掛け、データストローブ信号を用いて窓掛けクロック信号を捕捉して、フィードバック信号を生成する。このフィードバック信号は、メモリ制御装置に返される。

(もっと読む)

半導体装置およびそれを利用した情報処理システム

【課題】半導体装置において、温度変化によるデータのラッチタイミングの調整によって生ずるシステムのビジー期間を抑制しなければならない。

【解決手段】タイミング制御回路116は、任意の温度でデータDQiとストローブ信号がキャリブレーションによってマッチングされたストローブ信号DQS,DQSBを受信し、内部ストローブ信号IDQS、IDQSBを生成し、ラッチ回路118に出力する。ラッチ回路118は、内部ストローブ信号IDQS、IDQSBのエッジのタイミングでデータDQiをラッチする。タイミング制御回路116は、温度検知回路124と内部ストローブ信号IDQS、IDQSBの伝送経路に間挿され、温度検知回路124からの温度信号Tにしたがって、前記マッチングを維持するように内部ストローブ信号IDQS、IDQSBの時間変動を抑制する可変遅延回路122を含む。

(もっと読む)

メモリインタフェース回路及びタイミング調整方法

【課題】ストローブ信号のHi−Z状態の取り込みを防止しつつ、内部ストローブゲート信号のタイミング調整を高精度に行うことができるメモリインタフェース回路を提供する。

【解決手段】メモリインタフェース回路では、ストローブ信号DQSをマスクする内部ストローブゲート信号DQSGに対して0.5tCK分遅延した相対関係を有する内部ストローブゲート調整信号DQSGAが生成される。また、内部ストローブゲート調整信号DQSGAの活性化タイミングを時間的後方から前方にシフトさせる毎にストローブ信号DQSの電位を取り込み、第2期間T2以上連続してL電位であることを検出したときに検出信号が出力される。そして、メモリインタフェース回路では、検出信号に応じて内部ストローブゲート調整信号DQSGAの活性化タイミングを調整することで、内部ストローブゲート信号DQSGの活性化タイミングを調整する。

(もっと読む)

ダイナミックデータストローブ検出

【課題】データストローブ信号がデータの捕獲について有効であるときを決定するための技術を提供する。

【解決手段】一実施形態において、データストローブ信号に基づきメモリからデータを捕獲するための初期時間値を決定するように構成されたメモリインターフェイス回路を備えた装置が開示される。ある実施形態では、メモリインターフェイス回路は、メモリから既知の値を読み取ることによりこの初期時間値を決定する。一実施形態では、メモリインターフェイス回路は、更に、データを捕獲するための調整された時間値を決定するように構成され、ここで、メモリインターフェイス回路は、初期時間値を使用してデータストローブ信号をサンプリングすることによりその調整された時間値を決定するように構成される。

(もっと読む)

タイミング調整動作制御装置、情報処理装置、及びプログラム

【課題】温度センサを実装する必要がなく、予め定められた時間間隔でタイミング調整を行うよりも過不足なくタイミング調整を行うことができる。

【解決手段】複数のメモリが設けられた装置が起動したとき、又は該装置が節電モードから解除されたときにレベリング動作を実行し、該実行されたレベリング動作のレベリング結果に基づいて、複数のメモリの温度を推定し、該推定した温度と、複数のメモリが設けられた装置で実行される処理の内容に応じて予め定められた複数のメモリの単位時間あたりの上昇温度とに基づいて、処理の実行が開始されてから処理が終了又は停止するまでの期間に、複数のメモリの温度が予め定められた複数の温度区間の境界の温度に到達する時刻を推定し、処理の実行が開始されてから処理が終了又は停止するまで、上記推定された時刻が到来したときに、レベリング動作を実行する。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードからの復帰時間を高速化する。

【解決手段】例えば、コントローラ50は、半導体装置10がセルフリフレッシュモードにエントリしているか否かにかかわらず外部クロック信号CKを連続的に発行する。半導体装置10は、セルフリフレッシュモードにエントリしている期間に外部クロック信号CKの入力バッファ回路71とDLL回路200を間欠的に活性化させる。これにより、セルフリフレッシュモード中においてもDLL回路200の状態が間欠的に更新され、正しく位相制御された内部クロック信号ICLK1が得られる状態に保たれる。したがって、セルフリフレッシュモード中における入力バッファ回路71の消費電力を削減しつつ、セルフリフレッシュモードからイグジットした後、位相制御された内部クロック信号ICLK1を必要とするコマンドを短期間で投入することが可能となる。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードからの復帰時間を高速化する。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREとセルフリフレッシュイグジットコマンドSRXを交互に周期的に発行する。半導体装置10は、セルフリフレッシュコマンドSREに同期してリフレッシュ動作を例えば1回だけ実行し、セルフリフレッシュイグジットコマンドSRXに応答してDLL回路200の状態更新を実行する。これにより、セルフリフレッシュイグジットコマンドSRXを発行した後、ロウ系のコマンドや位相制御された内部クロック信号ICLK1を必要とするコマンドを短時間で発行することが可能となる。

(もっと読む)

メモリ回路システム及び方法

【課題】メモリ回路システムを提供する。

【解決手段】インタフェース回路104が複数のメモリ回路102及びシステム106と通信できる。使用時、インタフェース回路は、メモリ回路の命令スケジューリングにおける制約を減少させるため、メモリ回路及びシステムをインターフェースするように動作する。別の実施形態では、インタフェース回路が、複数のメモリ回路、及びシステムと通信することができる。使用時、インタフェース回路は、システムとメモリ回路との間で伝達される命令に関連付けられているアドレスを変換するように動作する。更に別の実施形態では、少なくとも1つのメモリ積層体が、複数のDRAM集積回路を備えている。DRAM集積回路とホストシステムの間で1つ以上の物理パラメータを変換する目的で、ホストシステムに結合されたバッファ回路を使用して、ホストシステムにメモリ積層体をインターフェースする。

(もっと読む)

メモリコントローラおよび遅延調整方法

【課題】必要なタイミングで、メモリに対する情報の入出力タイミングに関る遅延量を調整することのできるメモリコントローラを提供すること。

【解決手段】メモリコントローラ1であって、メモリ2への入力データおよびデータストローブ信号、並びに、メモリ2に対するコマンドおよびクロック信号を生成し出力するコントローラ部3と、入力データ、データストローブ信号、コマンド、およびクロック信号のうちの少なくとも一つの遅延量を制御する遅延調整回路5と、遅延量を検出し、検出した遅延量と、基準遅延量との差分を算出する遅延検出部4とを備え、コントローラ部3は、算出された差分が閾値を超えた場合、メモリ2のバースト長(BL)を第1BLから、第1BLよりも長い第2BLに切り替えるためのコマンドを発行し、遅延調整回路5は、第1BLと第2BLとの差に対応する期間に、少なくとも一つの遅延量を基準遅延量に近づくように制御する。

(もっと読む)

メモリコントローラ及び制御方法

【課題】ライトレベリング時のサイクルずれを補正する。

【解決手段】第1ダミーパターンを試験対象メモリの第1のアドレスに書き込む第1ライト部11と、第1ダミーパターンの書き込みに後続して、テストパターンを第2のアドレスに書き込む第2ライト部11と、テストパターンの書き込みに後続して第2ダミーパターンを第3のアドレスに書き込む第3ライト部11と、第2のアドレスからテストパターンを読み出すリード部14と、テストパターンの読み出し結果に基づいて、データの書き込みタイミングを調整するタイミング調整部14とをそなえる。

(もっと読む)

多様に配置されたメモリ・コンポーネントからメモリ・オペレーションを調整する方法と装置

【課題】 さまざまな位置に配置されたメモリ・コンポーネントの間でメモリ動作を調整する方法および装置を提供すること。

【解決手段】 本発明の実施形態によれば、複数のメモリ・コンポーネントに結合されたアドレス・バスについて、ウェーブパイプライン化が実施される。複数のメモリ・コンポーネントが、アドレス・バス伝搬遅延およびデータ・バス伝搬遅延に関係する調整に従って構成される。アドレス信号および/または制御信号に関連する、これらの信号の伝搬遅延を複製するタイミング信号が、メモリ動作の調整に使用される。

(もっと読む)

受信回路、システム装置、及びタイミング調整方法

【課題】データを取り込むタイミングを調整すること。

【解決手段】メモリインタフェース回路12のマスク生成部37は、データ列DQと同期したストローブ信号DQS(内部ストローブ信号IRS)に基づいて、データ列DQを受け取る期間に応じた内部マスク信号CKMを生成する。DLL回路41は、レジスタ41aの設定値に応じて内部クロック信号CK2を遅延した内部クロック信号CKSを生成する。フリップフロップ回路33,34は、アンド回路38により内部マスク信号CKMと内部クロック信号CKSを合成した内部ストローブ信号CSTに応じて受信データ列RDQをラッチする。調整回路50は、DLL回路51,52の出力信号に基づいて、内部マスク信号CKMと内部ストローブ信号CSTの位相関係を検出し、レジスタ41aの設定値を更新して内部ストローブ信号CSTの位相を調整する。

(もっと読む)

メモリシステム

【課題】複数のメモリデバイスがメモリコントローラに共通接続されるタイプのメモリシステムにおいて、データ読み出し時に大きなノイズが発生するリスクを低減する。

【解決手段】メモリシステムは、メモリコントローラ32と複数のメモリデバイス12a〜12dを備える。メモリデバイス12a〜12dの各データ端子20dは、メモリコントローラ32に共通接続される。メモリデバイス12は、メモリセルアレイ14とメモリセルアレイ14から読み出されたデータを出力するデータ出力回路18を含む。メモリデバイス12a〜12dがデータを出力するタイミングは、互いに異なるように調整されている。

(もっと読む)

メモリ制御装置、メモリ制御方法、プログラム

【課題】メーカなどに応じて最良の性能が得られる条件が異なるメモリカードごとに対応して、最良の性能が的確に引き出されるようにする。

【解決手段】データ書込制御部121は、単位書込データサイズ設定部122が順次設定する単位書込データサイズごとに所定回数の単位書込データのランダムライトを実行する。タイマ値保持部125は、この所定回数のランダムライトごとに応じてタイマ部124が計測したタイマ値を保持する。最適条件決定部126は、タイマ値保持部125が保持するタイマ値に基づいて転送速度が最も高くなる単位書込データサイズを決定する。

(もっと読む)

記憶制御装置、記憶制御方法及び記憶制御プログラム

【課題】記憶部の特性に変化が生じた場合でも記憶部に対して正常なアクセス制御を確保する。

【解決手段】記憶部4をアクセス制御するFPGA3に関わる、記憶部4のアクセス制御の特性に対応した、複数の構成情報を記憶するメモリ20と、構成情報をFPGA3に設定するコンフィグレーション制御部40とを有する。コンフィグレーション制御部40は、メモリ20に記憶中の一の構成情報をFPGA3に設定した後、記憶部4のHレベルのメモリNG信号を検出すると、メモリ20に記憶中の異なる構成情報に切替える。そして、コンフィグレーション制御部40は、切替えられた構成情報をFPGA3に設定する。

(もっと読む)

メモリインターフェイス制御回路及び半導体集積回路

【課題】回路規模を増大させず、ノイズ等の影響により不正規な波形となったデータストローブ信号DQSを排除し、正常なデータアクセスを可能とするメモリインターフェイス制御回路の提供が望まれる。

【解決手段】メモリインターフェイス制御回路は、DDR SDRAMがデータを転送するタイミングを通知するデータストローブ信号を受け付け、データストローブ信号に異常波形が検出された場合にはデータ初期化信号を出力するデータストローブ信号検証回路と、データストローブ信号が活性化した際に、DDR SDRAMから出力されるデータ信号を保持し、データ初期化信号を受け付けた場合には保持したデータの初期化を行なう保持回路と、保持回路が出力するデータを一時的に取り込み、取り込んだデータを外部に出力するFIFO回路と、を備える。

(もっと読む)

1 - 20 / 250

[ Back to top ]