Fターム[5B060CC05]の内容

メモリシステム (7,345) | アクセスタイミング制御 (460) | アクセス同期/非同期制御 (24) | 装置間の同期/非同期制御 (6)

Fターム[5B060CC05]に分類される特許

1 - 6 / 6

記憶装置、通信システムおよび記憶装置の制御方法

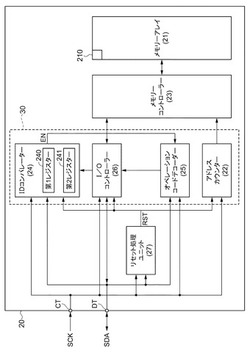

【課題】リセット信号線を接続するための端子や配線等の回路構成がなく、簡易な構成をもつ記憶装置、カートリッジ、通信システムおよび記憶装置の制御方法を提供すること。

【解決手段】記憶装置20は、クロック信号SCKおよびデータ信号SDAが入力され、リセットにより初期化された後にクロック信号SCKに同期したデータ通信を開始するよう構成されている。この記憶装置20は、クロック信号SCKがハイのレベルを維持する期間において、データ信号SDAに複数回のレベル変化を生じたか否かを判定し、複数回のレベル変化を生じていた場合に、記憶装置20のリセットを実行するリセット処理ユニット27を備えている。

(もっと読む)

リフレッシュ制御装置、無線受信機および半導体集積回路

【課題】メモリのリフレッシュ動作を要求するためのトリガの周期に起因するノイズのレベルを低減する。

【解決手段】リフレッシュ制御装置400は、DRAM200へのメモリアクセス要求と、リフレッシュ動作の実行を要求するためのリフレッシュトリガとを調停する調停機能部700と、リフレッシュレート規定を満たすように、前記リフレッシュトリガを一定でない周期で発生するトリガ発生部600とを備える。

(もっと読む)

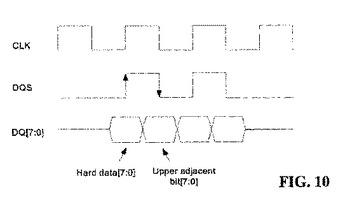

フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間でインタフェースをとるための方法および装置

フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間でインタフェースをとるための方法および装置が提供される。このインタフェースは、フラッシュ・メモリ・コントローラとフラッシュ・メモリ・アレイの間の通信チャネルを備え、この通信チャネルは、クロック信号の第1のエッジでフラッシュ・メモリ・アレイにおけるターゲット・セルに関するデータを伝送し、さらにこの通信チャネルは、クロック信号の第2のエッジで、そのターゲット・セルに関するさらなる情報を伝送する。例示的な書き込みアクセスの場合、さらなる情報は、例えば、ターゲット・セルに関連する1つまたは複数のアグレッサ・セルについての情報を備える。例示的な読み取りアクセスの場合、さらなる情報は、例えば、第1のエッジで伝送されるターゲット・セルに関するデータに関するソフト情報を備える。  (もっと読む)

(もっと読む)

情報処理装置およびインターフェイス回路

【課題】バスマスタがレジスタ等の周辺モジュールをアクセスする際のレイテンシを有効に低減する情報処理装置及びインターフェイス回路を提供すること。

【解決手段】第1クロック信号に同期して動作するバスマスタ(1100)と、第2クロック信号に同期して動作する周辺モジュール(1200)と、前記第1クロック信号に同期して前記バスマスタとの間でデータ転送するための第1アクセスポートと前記第2クロック信号に同期して前記周辺モジュールとの間でデータ転送するための第2アクセスポートとを有する記憶手段としてデュアルポートRAM(1210)を有し、該デュアルポートRAMを介してバスマスタ(1100)と周辺モジュール(1200)との間のデータ転送を遂行する。

(もっと読む)

高速メモリシステムにおいて読出しタイミングを同期させる方法

【課題】モリコントローラの複雑さを低減する目的でメモリデバイスのシステム読出し待ち時間を均一化する。

【解決手段】制御回路2000は、制御回路が前記フラグ信号を受け取ってから所定数の読出しクロックサイクル後に、前に受け入れたコマンドに関連するデータをメモリデバイスがメモリアレイから少なくとも1つのデータ信号線上に出力開始し、メモリデバイスの読み出し待ち時間と等しくするために、前記読み出しクロックサイクルの数は信号伝播の特徴にしたがって予め定められる。

(もっと読む)

タイミング調整方法及び装置

【課題】外部ストローブ信号及びこの信号に同期した外部データをシステムクロックでラッチするタイミングを調整する。

【解決手段】メモリ100からのストローブ信号s100aはストローブ遅延選択部103の遅延回路1031〜103nで遅延されて複数の遅延ストローブ信号となる。ストローブラッチ部106は、前記各遅延ストローブ信号の受信タイミングでチェック用データを生成し、システムラッチ部107は、ストローブラッチ部106でラッチされたチェック用データをシステムクロックs200でラッチする。期待値比較部108及び遅延判定部109での比較、判定に基づいて、ストローブ遅延選択部103での最適遅延の最適ストローブ信号が選択される。その後、メモリ100からのデータs100bをデータ遅延選択部104の遅延回路1041〜104nで遅延させて複数の遅延データとして、その中から、前記期待値比較部108及び遅延判定部109での比較判定に基づいて、最適遅延の最適データが選択される。

(もっと読む)

1 - 6 / 6

[ Back to top ]