Fターム[5B060MB00]の内容

メモリシステム (7,345) | メモリバス技術 (414)

Fターム[5B060MB00]の下位に属するFターム

複数のバスの切替、接続制御 (155)

複数系システム(バス)間の接続制御 (30)

バス使用モード制御 (34)

データ幅とバス幅が異なるもの (43)

バスのライン数の削減技術 (52)

共通バスの他にメモリ専用バスを有するもの (16)

Fターム[5B060MB00]に分類される特許

1 - 20 / 84

メモリモジュール

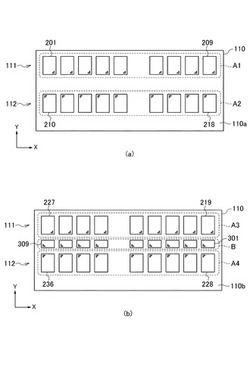

【課題】Load Reduced型のメモリモジュールにおいてメモリデバイスの搭載位置によるデータのスキューを低減する。

【解決手段】データコネクタを有するモジュール基板110と、複数のメモリデバイス201〜236と、データコネクタとメモリデバイスとの間に接続されたデータレジスタバッファ301〜309とを備える。モジュール基板110は、メモリデバイスが搭載されたメモリ搭載領域A1,A2と、平面視でメモリ搭載領域A1,A2に挟まれた位置に定義され、データレジスタバッファが搭載されたレジスタ搭載領域Bとを有する。各メモリデバイスとデータレジスタバッファとの配線距離がほぼ均一になるため、メモリデバイスの搭載位置によるデータのスキューが低減される。

(もっと読む)

メモリモジュール及びメモリシステム

【課題】メモリデバイスにおける信号の反射を抑制するメモリモジュール及びこのメモリモジュールを複数備えてジッタを低減できるメモリシステムを提供する。

【解決手段】メモリモジュール1は、外部からアドレス/コマンド信号の入力を受ける外部入力端子3と、外部入力端子3からのアドレス/コマンド信号を受信する複数のメモリデバイス4a〜4hと、を備えている。また、メモリモジュール1は、外部入力端子3から複数のメモリデバイス4a〜4hに向かって2分岐を繰り返して形成された信号線路6を備えている。更に、メモリモジュール1は、信号線路6における2段目以降の分岐点7b〜7g、及び複数のメモリデバイスの入力端子5a〜5hのうち、いずれか一点に接続された終端抵抗9を備えている。

(もっと読む)

半導体モジュール及びこれを搭載したマザーボード

【課題】リセット信号配線上における共振現象を防止する。

【解決手段】リセット信号RSTが供給されるリセット端子30R及びリセット信号RSTの活性化に応答してリセットされる内部回路31,32をそれぞれ含む複数の半導体チップ12と、複数の半導体チップ12が搭載されたモジュール基板11とを備える。モジュール基板11は、複数の半導体チップ12にそれぞれ設けられたリセット端子30Rに共通接続されたリセット信号配線14Rと、リセット信号配線14Rに接続された共振防止素子15とを備える。本発明によれば、通常動作時において論理レベルが固定されるリセット信号RSTが共振現象によって活性化されることがなくなる。

(もっと読む)

様々な書き込みコマンド・スケジューリングを含むメモリシステム

【課題】様々な書き込みコマンド・スケジューリングを含むメモリシステムを提供する。

【解決手段】システム100は、ホストデバイス50を含み、ホストデバイス50は、システム・メモリにメモリ・リクエストを始めるように構成される。システム100はメモリコントローラ25を含み、メモリコントローラ25は、メモリ・リクエストを受け取るように、そして、メモリインタフェースを介してメモリデバイス20に運ばれるメモリ・トランザクション33にメモリ・リクエストをフォーマット化するように構成される。メモリ・トランザクション33は、複数のメモリ書き込みコマンド・タイプを含む。各メモリ書き込みコマンド・タイプは、対応するデータ・ペイロードを運ぶために異なるそれぞれのスケジュールに対応する。

(もっと読む)

データ出力装置、データ入出力装置、記憶装置、データ処理システム、および、データ出力装置の制御方法

【課題】複数のメモリを接続するデータバスにおいて、汎用性を確保しつつ、データの衝突を防止する。

【解決手段】

制御回路110は、データ出力期間の開始時点から前記データ出力期間より短いドライブ期間を経過するまでの間だけ前記出力ドライバ170に前記データを入力するとともに、前記データ出力期間を経過したときにラッチ回路180に電流の供給を停止させる。出力ドライバ170は、入力された前記データの値に応じた電位を前記出力端子190に印加することにより絶対値が所定値となるドライバ電流を出力端子190に供給する。ラッチ回路180は、前記出力端子190に印加された電位を保持するとともに、保持している前記電位を前記出力端子190に印加することにより絶対値が前記所定値より小さいラッチ電流を前記出力端子に供給する。

(もっと読む)

半導体装置

【課題】複数のランクに分類された積層型の半導体装置において、異なるランクに対して連続アクセスされた場合のデータの衝突を防止する。

【解決手段】ライトデータを伝送する貫通電極TSVWとリードデータを伝送する貫通電極TSVRとをそれぞれ有する互いに積層された複数のコアチップCC0〜CC7と、これらコアチップCC0〜CC7に共通接続されたインターフェースチップIFとを備える。インターフェースチップIFは、データ入出力端子16と、データ入出力端子と貫通電極TSVWとの間に設けられた52入力バッファと、データ入出力端子16と貫通電極TSVRの間に設けられた出力バッファ51とを有する。本発明によれば、ライトデータとリードデータを互いに異なる貫通電極を介して伝送していることから、異なるランクに対して連続アクセスされた場合であってもデータの衝突が生じない。

(もっと読む)

メモリモジュール及び半導体記憶装置

【課題】アドレス信号と制御信号のタイミングの不一致に起因する誤動作が防止できるメモリモジュールを提供する。

【解決手段】メモリモジュールに、データを入出力する単位である複数のランクに区分けされた複数の半導体記憶装置と、全ランクの半導体記憶装置が縦列接続される、外部から入力されたアドレス信号を該半導体記憶装置に供給するための配線であるアドレス信号配線と、ランク単位で半導体記憶装置が縦列接続される、外部から入力された制御信号を該半導体記憶装置に供給するための配線である制御信号配線と、制御信号配線と接続された各半導体記憶装置に対応して設けられた、半導体記憶装置の入力容量と(ランク数−1)との積に等しい容量を持つ容量部とを備える。

(もっと読む)

データバス反転信号伝達を用いる同時スイッチング出力の低減

数値制御装置の初期化方法及び数値制御装置

【課題】CPUの初期化時間を短縮可能な数値制御装置の初期化方法及び数値制御装置を提供する。

【解決手段】数値制御装置1は、第1動作周波数よりも速い第2動作周波数とに切り換えて動作可能なCPU2Aと、初期化するためのブートプログラムが格納されたROM3と、このROM3とCPU2A,2Bとを接続するバス5と、このバス5に介装され複数のCPU2A,2BとROM3との信号伝達を調停可能なバス調停回路6とを有し、CPU2Aの起動時に、CPU2Aとバス調停回路6を第1動作周波数で起動させ、次に、バス5とバス調停回路6を介してROM3からブートプログラムを読み込んでCPU2Aのキャッシュメモリ10に格納し、CPU2Aの動作周波数を第1動作周波数から第2動作周波数に切り換え、CPU2Aの動作周波数の切り換えに応じて、バス調停回路6の動作周波数を第1動作周波数から前記第2動作周波数に切り換える。

(もっと読む)

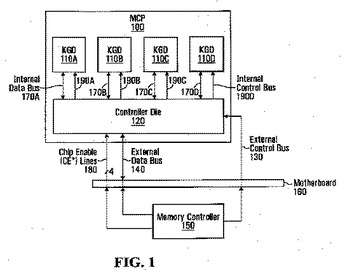

複数のメモリダイとコントローラダイとを有する半導体記憶装置

半導体記憶装置は、複数のメモリダイと、コントローラダイとを含む。コントローラダイは内部制御バスに接続される。コントローラダイは、外部リードコマンドに応答して、前記メモリダイのうちの選択された1つに内部リードコマンドを提供するように構成される。選択されたメモリダイは、内部リードコマンドに応答して、コントローラダイに読み出しデータを提供するように構成される。選択されたメモリダイとして選択されたときの、コントローラダイによる外部リードコマンドの受信とコントローラダイによる該選択されたメモリダイからの読み出しデータの受信との間のレイテンシが、前記メモリダイのうちの少なくとも2つに関して相異なる。  (もっと読む)

(もっと読む)

メモリインターフェース回路

【課題】メモリチップの出力バッファにかかる負荷容量が大きい場合においても、出力バッファのサイズを大きくすることなく、読み出し波形の劣化を低減する。

【解決手段】半導体記憶素子から読み出された読み出し信号Diと基準電圧vrefが差動入力として与えられる差動回路21と、差動回路21から出力された過去の差動信号の状態から遠ざかるように、差動回路21から出力される現在の差動信号の電位を制御するイコライズ回路28と、イコライズ回路28にて制御された差動信号の状態を検出するラッチ型センスアンプ25と、ラッチ型センスアンプ25にて検出された差動信号の過去の状態を保持し、イコライズ回路28に供給する状態保持回路29とをコントローラに設ける。

(もっと読む)

メモリシステム及びそれに用いられるメモリコントローラ

【課題】メモリデバイス内の終端抵抗をONさせて、データバスと各メモリデバイスとの間における反射波を有効に防止し、それが不要であるときには積極的にOFFしてできるだけ消費電力を抑えて、かつ信号振幅レベルを最大にする。

【解決手段】メモリコントローラと複数のメモリデバイスが1本のデータバス1を介して接続されている。各メモリデバイスはON/OFF可能なアクティブな終端抵抗5を有し、メモリコントローラは各メモリデバイスのアクティブな終端抵抗5のON/OFFを制御する終端抵抗制御信号を出力するユニットを有し、各メモリデバイスはデータバス1ごとにデータ信号の変化点を検出する回路13を有し、検出された変化点からの一定時間の区間に対してメモリコントローラからの終端抵抗制御信号のアクティブ制御を有効とし、一定時間以外の区間はアクティブ制御を無効に各メモリデバイス内で切り替える。

(もっと読む)

DIMMにおける相変化メモリ

【課題】相変化メモリ(PCM)モジュールを有するデュアルインラインメモリモジュール(DIMM)メモリデバイスの管理を提供する。

【解決手段】BIOSは、PCMモジュール識別(ID)を読み出して、PCMモジュール構成に応答するための、実行可能コードを有することができる。PCMモジュールは、DIMMが行アドレスを受信した直後に、メモリコントローラによって生成される列アドレスをDIMMへ供給することを可能にするアディティブレイテンシと関連することができる。DRAMキャッシュメモリのようなメモリデバイスを用いて、PCMDIMMの特定のアドレスに対応する書き込みデータをキャッシュに格納することができる。

(もっと読む)

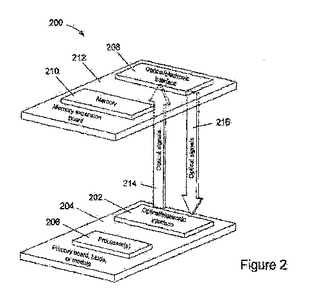

光学メモリ拡張

本発明の様々な実施形態は、コンピュータシステムのメモリを分離するための光学ベースの方法と拡張メモリシステムに向けられたものである。一態様において、拡張メモリシステム(200)は、プロセッサと電気的に連通している第1の光学/電気インターフェース(202)と、メモリと共に構成されたメモリ拡張ボード(204)と、前記メモリ拡張ボードに取り付けられた第2の光学/電気インターフェース(208)とを備える。前記第1のインターフェースは、光学信号を、前記プロセッサに送られる電気信号へと変換し、及び、前記プロセッサにより生成された電気信号を、光学信号へと変換する。前記第2のインターフェースは、光学信号を、前記メモリに送られる電気信号へと変換し、及び、前記メモリにより生成された電気信号を、光学信号へと変換する。前記光学信号は、前記第1のインターフェースと第2のインターフェースとの間において交換される。実施形態はまた、データを送って拡張メモリシステム内において受け取るための方法も含む。  (もっと読む)

(もっと読む)

データ記憶装置、及びデータ記憶装置の制御方法

【課題】データ記憶装置において、電力消費の低下を実現すること。

【解決手段】DRAMコントローラ208の省電力制御回路213は、DRAM101がリフレッシュモードに移行させるべき条件が成立したと判定した場合、DRAMコントローラ208がDRAMバス115を構成する各データ信号線へ出力する信号の状態をLowレベルに固定するとともに、TV電源106によるDRAMバス115を構成する各データ信号線への基準電圧の供給を停止するように制御する構成を特徴とする。

(もっと読む)

メモリモジュール

【課題】メモリバッファを用いることなく、各チャネルにかかる負荷が低減されたメモリモジュールを提供する。

【解決手段】モジュール基板180と、モジュール基板180に搭載されたメモリチップMC101〜MC172と、メモリチップMC101〜MC172にそれぞれ個別に接続され、リードデータ又はライトデータが伝送されるデータ入出力配線DQL1〜DQL72とを備える。メモリチップMC101〜MC172の数は、データ入出力配線DQL1〜DQL72を介して同時に伝送されるリードデータ又はライトデータのビット数と等しい。このように、複数のデータ入出力配線がそれぞれ個別のメモリチップに接続されていることから、メモリバッファを用いることなく、各チャネルにかかる負荷を低減することが可能となる。

(もっと読む)

メモリシステム、半導体記憶装置、及び配線基板

【課題】ODT端子による内蔵終端抵抗の制御とリードデータの出力タイミングのずれによるバス転送時間の遅れをなくす。

【解決手段】終端抵抗制御信号により外部からオンオフが制御可能な終端抵抗回路を備えた複数の半導体記憶装置と、複数の半導体記憶装置のうちいずれかの半導体記憶装置にリードコマンド又はライトコマンドを実行させるときに複数の半導体記憶装置の終端抵抗値がいずれもオンし、いずれの半導体記憶装置もリードコマンド又はライトコマンドを実行しないときに複数の半導体記憶装置の終端抵抗値がいずれもオフするように終端抵抗制御信号を出力する終端抵抗制御部を有するメモリコントローラと、を備え、半導体記憶装置の終端抵抗回路が、リードコマンドに応答してデータを出力するときに終端抵抗制御信号のレベルによらず、オフする。

(もっと読む)

トランザクションを開始することが可能な不揮発性メモリ

【課題】 マスタ/スレーブ設定ではなく、ピアツーピア設定で動作することができる不揮発性メモリが提供される。

【解決手段】 実施形態によっては、本メモリは、メモリの外のデバイスとのトランザクションを開始することができる。従って、本メモリは、従来はメモリコントローラと他の外部デバイスとで実行されるタスクを、主体的に実行することができる。

(もっと読む)

メモリアクセス制御装置

【課題】複数のリクエスタからのメモリアクセス要求の一を処理するものであって、アクセス効率を低下させずに同時スイッチング出力本数を低減するメモリアクセス制御装置を提供する。

【解決手段】メモリアクセス制御装置1は、メモリアクセス要求(以下、要求)を処理するもので、未処理の要求を順次記憶する記憶部と直前に処理した要求を保持するレジスタ14と未処理の要求から処理対象を選択するメモリアクセス選択処理部13と、を備え、メモリアクセス選択処理部13が、レジスタ14に保持されている要求が読み込み要求のとき、未処理の要求から任意に処理対象を選択し、レジスタ14に保持されている要求が書き込み要求のとき、未処理の要求から読み込み要求である要求を任意に選択し、未処理の要求が全て書き込み要求であれば、その書込みデータがレジスタ14の要求の書き込みデータに最も近い要求を選択する。

(もっと読む)

メモリコントローラ、不揮発性記憶装置、アクセス装置、及び不揮発性記憶システム

【課題】コマンドの先行発行が可能な不揮発性記憶システムにおいて、アクセス装置が電源遮断時のファイルの整合性を保ちつつ、ユーザーデータおよび管理情報データの制御を実施するのは困難であった。

【解決手段】コマンドスケジューラ162は、ユーザーデータおよび管理情報データにSeq番号を付与し、同一Seq番号をもつユーザーデータの書き込み完了後に、同一Seq番号を有する管理情報データの書き込みを実行するように制御する。これにより、書き込み中に電源遮断が発生してもファイルの整合性を保つことができる。

(もっと読む)

1 - 20 / 84

[ Back to top ]