Fターム[5B061BB06]の内容

バス制御 (3,799) | 調停のための制御方式(アービトレーション) (517) | 集中型調停 (434) | 調停制御装置の回路構成 (150) | 要求保持回路を有するもの (24)

Fターム[5B061BB06]に分類される特許

1 - 20 / 24

信号転送回路

【課題】プロトコルに従ってアクセスを行うアービタとバスマスタとの間の入出力信号のタイミングの制約を改善することができる信号転送回路を提供する。

【解決手段】バスマスタから入力されたメモリへのアクセス要求をアービタに中継する際に、入力されるアクセス要求入力信号およびメモリアドレス入力信号のタイミングを整えたアクセス要求出力信号およびメモリアドレス出力信号を出力すると共に、アービタから入力されるアクセス許可入力信号に先行して、アクセス許可出力信号をバスマスタに出力する制御信号転送部と、データをバスマスタまたはアービタに中継する際に、入力されるそれぞれのデータ入力信号のタイミングを整えたそれぞれのデータ出力信号を、バスマスタまたはアービタに出力すると共に、アービタから入力されるデータ有効期間入力信号のタイミングを整えたデータ有効期間出力信号をバスマスタに出力するデータ信号転送部と、を備える。

(もっと読む)

電子機器

【課題】 シリアルバスシステムにおけるリードレイテンシーの異なる複数の宛先に対する複数のリードリクエストが混在しても、各宛先に対するリードリクエストが円滑に処理されていくようにする。

【解決手段】 リクエストバッファー43は、所定の数のリクエストをキューイング可能であって、リクエストの宛先ごとに未処理リードリクエストの数の上限値を設定されている。調停部42は、新たなリードリクエストが受け付けられると、受け付けられたリードリクエストの宛先を特定し、特定した宛先についてのリクエストバッファー内の未処理リードリクエストの数が、特定した宛先についての上限値に到達している場合には、特定した宛先より優先度の低い宛先についての上限値を低くした上で、特定した宛先についての上限値を高くする。

(もっと読む)

送信権調停装置、送信権調停制御方法、及びそのためのプログラム

【課題】 リクエスト待ちによる空き時間の発生が、特定のスレーブに偏る確率が高くなる。

【解決手段】 複数のリクエスト発行元からリクエストを受信し、それらのリクエストを順次送信するリクエスト送信制御手段と、各リクエストを識別するリクエスト情報に基づいて、リクエスト毎のリクエスト発行元におけるリトライ処理時間を計時し、送信待ち状態のリクエストの内、リトライ処理時間の計時値が最大のリクエストを特定する、選出リクエスト情報を生成し、出力するリクエスト選出手段と、を含み、リクエスト送信制御手段は、選出リクエスト情報で特定されるリクエストを送信する。

(もっと読む)

DMA制御装置

【課題】DMAを行う複数のパイプラインを、簡単な設定により任意に接続できるようにし、またデータ交換の単位も、点・線・面・立体など柔軟に対応でき、さらに時分割制御により見かけ上同時実行可能なDMA装置を提供すること。

【解決手段】複数のDMA設定に対し、設定単位ごとに時分割スケジューリングを行う。自らのDMAの指標と接続するDMAの指標との比較結果を用いた起動制御を行い、さらに処理の順序関係を保証する。

(もっと読む)

割込み制御装置、割込み制御方法及び集積回路

【課題】プロセッサが省電力状態になってすぐに割込み要求が入力されることを防ぎ、プロセッサの通常状態から省電力状態への復帰回数を抑制する割込み制御装置を提供する。

【解決手段】プロセッサが省電力状態に遷移するときに、カウントを開始するカウンタタイマと、デバイス毎に設定されている割込み要求の保留許容時間を予め記憶している許容時間記憶手段と、前記プロセッサが省電力状態のときに発生した割込み要求の要求元のデバイスに対応して設定されている前記保留許容時間の中で、最も短い保留許容時間と前記カウンタタイマの値とを比較し、前記カウンタタイマの値が前記最も短い保留許容時間より小さい場合は、割込み要求の出力を保留し、前記カウンタタイマの値が前記最も短い保留許容時間以上の場合は、前記プロセッサに対して割込み要求を出力する出力手段とを備えることを特徴とする割込み制御装置。

(もっと読む)

半導体集積回路、及びリクエスト制御方法

【課題】論理規模を増大させることなく、複数のバスマスタからのリクエスト発行数を増加させる。

【解決手段】本発明による半導体集積回路100は、複数のキュー330と、複数のバスマスタ1、2から発行されたリクエストのアクセス先のアドレスに基づいて、リクエストを複数のキュー330のいずれかに振り分けるリクエスト振り分け部301と、複数のキュー330から選択したキュー内のリクエストを、外部デバイス5に発行するリクエストセレクタ302とを具備する。

(もっと読む)

データ転送制御装置およびデータ転送制御方法

【課題】共有バスに接続する複数のDMAチャネルがあって、SDRAM等のメモリにアクセスする際に、あらかじめ決められた優先順位を守りながら、高効率にメモリアクセスする調停手段を提供する。

【解決手段】マスターデバイスからのデータ転送要求を一定量保持する要求保持部と、保持されたデータ転送要求を優先順位及び予め定められた回数だけ連続するように並び替える要求並び替え部とを備え、前記データ転送要求を前記要求並び替え部が並び替えた順で発行することで、優先順位に応じて複数チャネルを並び替えるとともに同格の優先順位を持つ複数チャネルを平均的に連続させることができる。

(もっと読む)

調停優位性の切り替え方法、調停装置、及びプロセッサ

【課題】リクエストの種別に応じて、流動的かつ動的に調停の優先度を細かく切替え可能な調停優位性の切り替え方法、調停装置、及びプロセッサを提供する。

【解決手段】本発明に係る調停優位性の切り替え方法は、入力されるリクエストの種別と、同一の種別のリクエストが連続した連続回数と、連続回数が規定連続回数を超えた発生回数と、を監視する。発生回数が規定発生回数を超えた場合に、リクエスト調停において優先して選択させるリクエストの種別を指示する。リクエスト緩衝バッファから読み出すリクエストが、指示されたリクエストの種別と一致した場合には、重み付けテーブルを索引して、該当リクエストの種別毎に定めた重み付け値を決定する。リクエスト調停において勝利させるリクエストを示す調停優位性ポインタと、決定した重み付けの値と、に応じて、入力されるリクエスト間の調停を行う。

(もっと読む)

モジュール、割り込みコントローラ、動作方法、画像処理装置、画像形成装置、プログラム及び記録媒体

【課題】複数の割り込み要因を持つモジュールからの割り込みが発生した後と、複数の割り込み要因を持つモジュールからの1割り込み要因クリア処理が終了した後の、割り込み処理を高速化するモジュール及び割り込みコントローラを提供する。

【解決手段】複数の割り込み要因を持ち、割り込み要因毎に割り込み通知マスクを設定する割り込み通知マスク手段を有したモジュールであって、割り込み通知マスク手段により割り込み通知マスク設定が解除された複数の割り込み要因のなかで、少なくとも1以上の割り込み要因が発生した場合にパルス信号を出力し、当該モジュールでの割り込み要因発生を割り込みコントローラに通知する割り込み通知手段と、通知した割り込み要因がクリアされる前に他の割り込み要因が発生した場合には、割り込み通知手段が割り込みコントローラに対して割り込み要因発生を通知することを遮断する通知遮断手段と、を有する。

(もっと読む)

データ通信装置

【課題】要求コマンドと、それに対する応答とが分離されていて、要求コマンドに対する応答を待つことなく、次々と要求コマンドを発行可能なバスにおいて、転送レートの最悪値を保証する必要のある要求源に対し、高い保証値を達成するデータ通信装置を提供する。

【解決手段】スピリット・トランザクションのプロトコルを用いるインタフェースを介してデータ転送を行うデータ通信装置において、DMACの設定情報から先行してメモリアクセス要求を発行し、対象DMACの正常及び異常終了により先行リードアクセスしていたデータを無効化する。

(もっと読む)

バス制御方法

【課題】効率的にバスを使用すること。

【解決手段】バスにアクセスする優先度がそれぞれ異なる複数のバスマスターのうちの一つの注目バスマスターの保証転送帯域に対応するリクエスト許可数を記憶することと、前記バスにアクセス要求している前記注目バスマスター以外のバスマスターの数を、前記注目バスマスターのリクエスト許可数以内でリクエスト数として記憶することと、前記リクエスト数と同数の前記注目バスマスター以外のアクセス要求が処理された後に、前記注目バスマスターのアクセス要求を処理することと、を含む、バス制御方法。

(もっと読む)

バス装置

【課題】データの並べ替えによるバス転送の効率向上を実現することのできるバス装置を得る。

【解決手段】インオーダ対応バスマスタ2−1からの転送データにIDを付加し、IDをIDキュー部7で保持する。転送制御部8は、IDキュー部7のIDとバススレーブ3−1、3−2からの転送データのIDが一致した場合はあて先のバスマスタに転送する。一致しない場合は後で転送するとしてトランザクションキュー部9に蓄積する。トランザクションキュー部9の転送データのIDとIDキュー部7のIDが一致した場合、転送制御部8はその転送データをあて先のバスマスタに転送する。

(もっと読む)

バス制御装置

【課題】データ転送効率を高めることのできるバス制御装置を得る。

【解決手段】キュー判定部5は、キュー部4にデータ転送要求が蓄積されているかを確認する。要求判定部6は、バスマスタ2−1〜2−nからのデータ転送要求の有無を確認する。要求調停部7は、キュー部4に蓄積されたデータ転送要求が一つのみ存在し、かつ、データ転送要求が一つしかない場合は、予め定めた調停手順をスキップして、データ転送を要求しているバスマスタにバス使用許可を与える。

(もっと読む)

コンピュータシステム

【課題】 マスタ間のアクセス要求競合に伴うシステム性能劣化の回避策の検討を容易にする。

【解決手段】 複数のマスタ部に対応する複数の情報取得部の各々において、フラグ部は、対応マスタ部における所望の処理の実行開始/実行終了に伴ってセット状態/リセット状態に遷移する。時刻取得部は、フラグ部のセット状態/リセット状態への遷移に伴ってタイマ部の時刻を処理開始時刻/処理終了時刻として取得する。時間取得部は、フラグ部がセット状態である期間にて対応マスタ部のアクセス要求が調停部に対して発行され且つ調停部がメインメモリ部へのアクセスを対応マスタ部に許可していない場合にカウント動作を実施し、フラグ部のリセット状態への遷移時のカウント値を処理中断時間として取得する。情報保存部は、処理開始時刻および処理終了時刻と処理中断時間とを対応マスタ部に関連付けて保存する。

(もっと読む)

共有経路調停方法及びマルチシステム

【課題】マルチシステム全体でみた平均許可待ち時間を短くできる新しいバス調停方法の実現。

【解決手段】複数の処理装置11-0,1,2,3と、複数の処理装置によりアクセスされる共有資源14と、共有経路13と、共有経路の数の処理装置への割当てを制御する共有経路調停回路12と、を備えるマルチシステムであって、各処理装置は、実行予定の処理において共有資源14へのアクセスを要求する回数をカウントしてアクセス要求回数信号Niを出力するアクセス要求先読みユニット29を備え、共有経路調停回路12は、複数の処理装置から共有経路への割当てを要求された時には、アクセス要求回数の少ない処理装置に共有経路を割当てる。

(もっと読む)

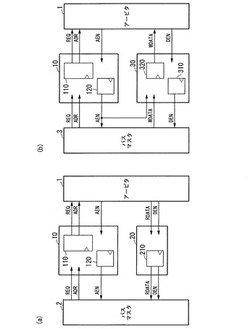

バス装置、バスシステムおよび情報転送方法

【課題】システムの周波数を向上させることのできるバス装置を提供する。

【解決手段】バスマスターとバススレーブの間で情報を転送するバス装置であって、複数のパイプラインレジスタ10A〜10H,20,30と、各パイプラインレジスタ10A〜10H,20,30を管理する複数の管理装置10A〜10H,20,30とを備え、各管理装置は、自段パイプラインレジスタが情報を保持するか否かを示す情報である保持状態を保持する保持状態保持手段と、前段パイプラインレジスタの保持状態と、後段パイプラインレジスタの保持状態を特定する隣段保持状態特定手段と、自段パイプラインレジスタの保持状態と、前段パイプラインレジスタの保持状態および後段パイプラインレジスタの保持状態とに基づいて、対応するパイプラインレジスタが保持する情報を転送するか否かを決定する転送制御手段とを有する。

(もっと読む)

バス調停回路及びバス調停方法

【課題】スレーブデバイスを追加する際に、マスタデバイス・スレーブデバイス間のデータ転送を調停する調停回路を少ない変更とすることができるバス調停回路を提供すること。

【解決手段】 バス調停回路30は、複数のマスタデバイス10と、これらにバスを介して接続されるスレーブデバイス20との間のデータ転送の調停をするものであって、複数のマスタデバイス10からデータ転送リクエストを受け取り、当該リクエストを出力したマスタデバイスの識別情報を要求順又は優先順に出力するID生成回路31と、ID生成部から受け取ったマスタデバイス識別情報に基づき、リクエストを処理させるリクエスト処理部32とを有する。調停回路30のうち少なくともリクエスト処理部32は、スレーブデバイス20毎に設けられている。

(もっと読む)

データ処理装置

【課題】 LSIの内部バスに接続されたデータ処理部がバスを使用する使用権優先度の変更を、バスアービタの設計変更を行わず、かつ汎用的なバスアービタを用いずに簡単な方法で実現する。

【解決手段】 LSIの内部バスに接続されたバスマスタのリードデータを保持するFIFOの有効段数を変更することでバス使用権の要求頻度を変更する。

(もっと読む)

シリアル割込み復帰回路

【課題】 外部からのシリアルデータにより周辺機器を停止状態から復帰させるシステムにおいて、無駄な電力の消費を削減するとともにCPUのパフォーマンスに関係なく高速受信を行えるシリアル割込み復帰回路を提供する。

【解決手段】 受信シフトレジスタ102と、受信制御回路101と、復帰要求設定レジスタ107と、比較回路109と、割込み発生回路114と、受信割込み復帰制御回路106と、クロック制御回路105とを備えることにより、受信待受け、受信動作、復帰要求データ比較動作の際にCPU116を停止することができ、無駄なCPU動作を削減し、無駄な電力の消費を低減させることができる。また、CPU動作と関係なく受信動作を行うことができるので、CPUのパフォーマンスに関係なく高速受信を安定して行える。

(もっと読む)

データ処理装置

【課題】 簡素な構成で、複数のコントローラ間での排他処理によるバス効率の低下を抑制することができるデータ処理装置を提供する。

【解決手段】 複合装置10において、コントローラ100は、割込要求元および割込要求先毎に割当てられた複数の割込要求領域を含むレジスタ110と、信号線156a〜156dを介して各割込要求先と接続される出力端子122a〜122dと、割込要求領域への割込信号発生要求のバス150を介した書き込みに伴って、対応する割込要求先に出力端子を介して割込信号を出力する割込信号出力部120と、を有し、各コントローラ300〜500は、割込情報を記憶するメモリ310〜510と、割込処理を行う場合、割込要求先のメモリ310〜510に割込情報を、およびレジスタ110における割込要求先に対応する割込要求領域に割込信号発生要求を、バス150を介して書き込むPCIC306〜506と、を備える。

(もっと読む)

1 - 20 / 24

[ Back to top ]