Fターム[5B061BC02]の内容

Fターム[5B061BC02]の下位に属するFターム

ラウンドロビン (25)

アクセス要求の不受理回数によるもの (11)

バッファ内のデータ量によるもの (20)

待ち時間によるもの (33)

相手装置の状況によるもの (27)

緊急処理要求によるもの (18)

RAM、ROMによるもの (5)

プライオリティレジスタによるもの (22)

Fターム[5B061BC02]に分類される特許

1 - 20 / 59

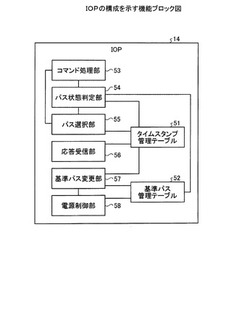

通信制御装置、情報処理装置及びパス選択方法

【課題】パスを効率的に使用すること。

【解決手段】IOP14は、パス状態判定部54とパス選択部55とを有する。パス状態判定部54は、自装置と通信先装置とを接続する複数のパスのうちデータの送信処理中ではなく、かつ、データ送信を終了した後にデータ送信を所定時間禁止する禁止期間内でもないパスが存在するか否かを判定する。パス選択部55は、パス状態判定部54によって、データの送信処理中ではなく、かつ、禁止期間内でもないパスが存在しないと判定された場合、データの送信処理を終了したが禁止期間を経過していないパスをデータ送信用に選択する。

(もっと読む)

データ転送制御装置及び方法並びにデータ処理装置

【課題】転送されるデータに転送が完了されるべき時間である締切時間が設定される場合、例えば、優先度が低いデータであって、比較的締切時間が近いデータの場合でも、データ転送の締切時間に応じた転送スケジュールでデータの転送を行い、締切時間内に転送が行われるようにする。

【解決手段】データ転送制御装置は、データを入力する複数の入力ポートと、データを出力する出力ポートと、データに設定される締切時間に基づいて、データを複数の入力ポートから出力ポートに転送する転送制御部とを備える。

(もっと読む)

バス調停回路及びバス調停方法

【課題】複数のデバイスによるデータ転送を同時に行うことができるとともに、特定のデバイスが故障した場合でも、他のデバイスによるデータ転送を可能とする。

【解決手段】バス調停回路1は、複数の領域からなり、データを所定領域に格納する複数のキューイングバッファ12a〜12cと、デバイス3a〜3cから送信されたデータを各々受信し、受信データのキューイングバッファ12a〜12cへの書き込みを制御する複数の受信制御部11a〜11cと、複数の領域からなり、デバイス3a〜3cからの受信データが格納されたキューイングバッファ12a〜12cを示す情報を、複数の受信制御部によるデータの受信順序に従って所定領域に格納するコヒーレンシバッファ13と、コヒーレンシバッファ13に格納された情報に基づき、データの受信順序通りにキューイングバッファ12a〜12cからデータを読み出し、バス2に送信する送信制御部14とを備える。

(もっと読む)

マルチプロセッサシステム及び割り込み制御方法

【課題】割り込み処理に必要な機能の使用許可を待つ間、マスクされている他の割り込み要求の有無を検出する割り込み制御回路を提供する。

【解決手段】プロセッサ110で実行される割り込み処理に関して複数の割り込み要求を制御する割り込み制御回路であって、割り込み処理の実行中に、該割り込み処理によりマスクされている割り込み要求の有無を検出する検出手段である割り込み制御モジュールユニット150と、前記割り込み要求の有無を示す優先度マスクフラグ140を備えた割り込み制御回路120である。このような構成により、マスクされている他の割り込み要求の有無を簡便に検出することができる。

(もっと読む)

データ転送システム、スイッチ及びデータ転送方法プロセッサ間ネットワーク

【課題】プロセッサ間で転送するパケットの転送時間の偏りを低減することができるデータ転送システム、スイッチ及びデータ転送方法を提供すること。

【解決手段】本発明にかかるデータ転送システムは、複数のプロセッサと、複数のプロセッサに含まれる一のプロセッサから他のプロセッサに対するデータ転送を複数の入力及び出力ポートを介して実行する複数のデータ転送部20を備える。データ転送部20は、次の転送先が同じ競合データについて調停を実行する調停手段259と、調停を行った競合データの競合数を示す強度情報を次の転送先に送信する強度情報通知手段260を有する。調停手段259は、調停を実行する場合には、複数の入力ポートの中でそれぞれの入力ポートを選択し、その入力ポートから競合データを入力する割合を示す選択割合を、各入力ポートから受信した強度情報が示す競合数の多さに関する入力ポート間の割合に応じて決定する。

(もっと読む)

情報処理装置

【課題】プロセス単位で優先度を制御することによって情報処理装置全体の処理能力を向上させる。

【解決手段】データ転送のためのバス(25)と、それぞれプロセスを処理単位とする処理機能を有し、上記バスに対してデータ転送要求を発行可能な複数の機能モジュール(10,11,12,20,22,23)とを設ける。また、上記プロセス毎に設定されたプロセス識別情報を、当該プロセスを処理する上記機能モジュールに対応付けて保持可能なプロセス識別情報保持部(101,111,121,201,221,231)を設ける。さらに上記機能モジュールからのデータ送要求毎に、対応する上記プロセス識別情報毎の処理の優先順位を決定し、その優先順位に従って上記バスに対するデータ転送要求の競合を調停するバスアービター(26)を設ける。プロセス単位での優先順位制御を行うことで処理能力を向上させる。

(もっと読む)

プロセッサーシステム

【課題】各デバイス間の通信を効率よく中継する。

【解決手段】マスターデバイス40とそれに対するスレーブデバイスとしての第1のスレーブデバイス50とを接続してデバイス間の通信を中継するクロスバースイッチ45と、マスターデバイス40および第1のスレーブデバイス50に対するスレーブデバイスとしての第2のスレーブデバイス60と第1のスレーブデバイス50とを接続してデバイス間の通信を中継する多段ブリッジ55とを備えて、クロスバースイッチ45と多段ブリッジ55との接続を介してマスターデバイス40と第2のスレーブデバイス60とを接続してデバイス間の通信を中継するから(経路(3))、各デバイス間の通信において通信対象となるデバイス以外のデバイスを経由する必要がなく、各デバイス間の通信を効率よく中継することができる。

(もっと読む)

半導体集積回路装置

【課題】システムのリアルタイム性能を向上させる。

【解決手段】CPU(103)と、上記CPUに結合されたバス(106)と、それぞれ上記バスを使用してデータ通信を行い得る複数の通信モジュール(108A,108B,108C)と、上記各通信モジュールからの要求に応じた処理を上記通信モジュール毎の優先度に従って実行する回路(104,105)とが設けられる。そして上記通信モジュール毎の通信待ち時間に応じて上記優先度を調整するための通信モニタ(111A)が設けられる。最も通信待ち時間が長い通信チャネルから順に処理を実行させることにより、システムのリアルタイム性能を向上させる。

(もっと読む)

バスアクセスアービトレーションスキーム

【課題】処理システムにおけるバスアービトレーションスキーム。

【解決手段】処理システムは、バス、バスに接続された複数のプロセッサ、及びバスアービタを含む。バスアービタは、第1の層内のプロセッサの各々に対して第1の層の重みを割り当て、第2の層内のプロセッサの各々に対して第2の層の重みを割り当てる。バスアービタは、割り当てられた第2の層の重みに基づいて、バス間隔の初期部分の間、1又は複数のプロセッサへバスアクセスを連続的に許可し、第1の層の重みを有するプロセッサのうちの何れか1つからの要求に応じて、バス間隔の初期部分の間、前記プロセッサのうちの何れか1つへのバスアクセスを許可する。複数のプロセッサがバスへのアクセスを要求する場合、バスアービタは、バスアクセスを要求するプロセッサのうち、最高次の層内の最も大きな重みを有するプロセッサへのバスアクセスを許可する。

(もっと読む)

データ転送装置、データ転送方法、データ転送プログラム及び記録媒体

【課題】優先順位の異なる複数のDMACからのメモリへのアクセス要求を優先順を変更して適切に調停するデータ転送装置、データ転送方法、データ転送プログラム及び記録媒体を提供する。

【解決手段】ライン同期信号LSYNCと画像先端同期信号FSYNCに基づいて1ライン分の画像データをメモリから読み取って転送するRDMAC134を含む複数のDMAC123、124からのメモリへのリクエストを予め設定されている優先順位に基づいてリクエスト調停部112が調停する場合、画像処理部11の転送データ量監視部136が2つのラインバッファ132がフル状態か否か監視して、該監視結果に基づいて必要転送量計算部105が、上記優先順位の変更の要否を判定し、優先順位制御部111が該判定結果に基づいてリクエスト調停部112の優先順位を制御する。

(もっと読む)

情報処理装置、画像処理装置及びバスアクセス制御方法

【課題】デバイスの数の変更への対応を容易化することができる情報処理装置、画像処理装置及びバスアクセス制御方法を提供する。

【解決手段】アクセス制御部100は、バッファ11との間で情報の送出、受理を行うインタフェース部101、いずれのバッファにバスへのアクセスを許可するか選択を行うアクセス許可部102、バッファ情報103aを記憶する記憶部103などを備える。バッファ11は、バッファのID、優先度などを記憶する記憶部111、アクセス制御部100との間で情報の送出、受理を行うインタフェース部112、アクセス許可されたバッファを判定部113、低い優先度又は高い優先度に更新する優先度更新部114などを備えている。

(もっと読む)

調停装置、画像処理装置、及び画像形成システム

【課題】書込要求信号が連続して調停手段に入力される場合に比べて、読み出しに必要な伝送路の帯域に応じて書込みに必要な伝送路の帯域を確保する、調停装置、画像処理装置、及び画像形成システムを提供する。

【解決手段】キューカウンタ62及び抑制装置64を備え、キューカウンタ62が書込要求信号wrreqが入力されたときに、読出データの読み出しが行われていない読出要求信号rdreqの数をカウントしてカウント値として抑制装置64に出力し、抑制装置64は、入力されたカウント値に応じて、チャネルCH1からのアクセス要求信号CH1_REQが調停回路52に入力される時間を遅延させることにより、チャネルCH1のアクセスを抑制する。

(もっと読む)

バスアクセスを調停する制御装置

【課題】 バスマスタのバス使用頻度に合わせてバス使用権を与え、かつ、バスの使用効率を向上させたバス使用権の調停を行う。

【解決手段】 ライトまたはリードリクエストがある(WreqまたはRreq=‘1’)場合、ライトまたはリードバッファのデータ蓄積数(PwまたはPr)が閾値以上、または、直前にリクエストキューに格納したリクエストがライトまたはリードリクエスト(ID1=IDwまたはIDr)か否かを判定し(S201、S202)、そうであればライトまたはリードリクエストをリクエストキューに蓄積する(S205、S206)ことで、バッファの空き状態、直前のアクセス、連続アクセス数に応じて優先順位を変更する。

(もっと読む)

調停装置、調停方法及びプログラム

【課題】調停処理の1サイクルあたりの実行処理内容を増加させず、かつ効率的なリクエストパケットの選択を行う。

【解決手段】予測回路35は、調停回路36による調停の実行の前に、調停回路36によって選択されるリクエストパケットの予測を行い、クロスバ4に当該リクエストパケットを出力させる接続命令を出力する。

(もっと読む)

トランザクションの優先レベルを設定するデータ処理装置および方法

【課題】トランザクションの優先レベルを設定するデータ処理装置および方法を提供する。

【解決手段】該データ処理装置は、トランザクションを処理する共有リソースと、該共有リソースへ該トランザクションを発行する少なくとも1つのマスタデバイスとを有する。該少なくとも1つのマスタデバイスは、該トランザクションの複数のソースを提供し、該トランザクションのそれぞれは、これに関連付けられた優先レベルを有する。アービトレーション回路は、該共有リソースへ発行された複数のトランザクションの中からあるトランザクションを選択するように、アービトレーションポリシーを適用するために使用され、該アービトレーションポリシーは、該選択を実行する際に、該複数のトランザクションのそれぞれに関連付けられた該優先レベルを使用する。

(もっと読む)

半導体装置

【課題】オンチップバスにおけるイニシエータによる実際の転送開始タイミングを把握することなくイニシエータのアクセス競合に対して的確な優先制御を行う。

【解決手段】イニシエータ(101_0〜101_2)、ターゲット(102)及び調停回路(103)を有する半導体装置(10)であって、調停のための処理単位の時間と前記処理単位の時間に許容される最大転送量とをレジスタ(109、110)に格納し、当該格納した値に基づき、前記処理単位の時間毎に、夫々のイニシエータの残り時間(202)と残りデータ量(302)を演算し、当該演算結果から優先度(113_0〜113_2)を繰り返し生成する。ターゲットに対するイニシエータのアクセス要求が競合した場合には、夫々のイニシエータの前記優先度を比較し、いずれかのイニシエータに対してアクセスの許可を発行する。

(もっと読む)

バス調停装置

【課題】バスマスタ側にバス優先使用要求用の回路を設けなくても、バス使用権の優先度を変更することのできるバス調停装置を提供する。

【解決手段】バスアービタ1は、バスインタフェース部11が、データバスへ送出された、ディスクリプタテーブルに記載のベースアドレスの値およびデータサイズの値のベースアドレスレジスタ12およびデータサイズレジスタ13への書き込みと、アドレスバスの観測を行い、転送開始アドレス検出部14が、ベースアドレスレジスタ12に格納の値に一致する値のアドレスデータを検出して転送開始検出信号を出力し、転送終了アドレス検出部15が、ベースアドレスレジスタ12に格納の値から増分が、データサイズレジスタ13に格納の値に一致するアドレスデータを検出し、バス使用権制御部16が、転送開始検出信号の出力開始から転送終了検出信号の出力終了までの間、転送実行中のバスマスタのバス使用権の優先度を上げる。

(もっと読む)

データ転送システム及びターゲット装置

【課題】ラウンドロビン方式等のバス調停における上記不具合を解消でき、かつ簡易な構成で実現することができるデータ転送システム及びこれに用いるターゲット装置を提供する。

【解決手段】ターゲットデバイス3が、所定のリトライ応答回数をカウントするリトライカウンタ17を有し、複数のイニシエータA,Bの各々との間でデータ転送を逐次実行するにあたり、データ転送が完了してビジー状態が解除された時点からリトライカウンタ17が所定のリトライ応答回数をカウントするまで、リトライ応答させるための制御信号を出力し、この制御信号に従ってリトライ応答する。

(もっと読む)

情報通信システムの処理要求調停方法及びそのシステム並びにそのための制御プログラム

【課題】情報処理システムの性能向上を図る。

【解決手段】プロセッサ11,12からHDD16へのアクセスを第1のアドレス空間又は第2のアドレス空間を介して行い得るように情報処理システム10を構築する。プロセッサ11,12がHDD16へアクセスするとき、そのアクセスが第1のアドレス空間を介して行われたものであるか、第2のアドレス空間を介して行われたものであるかをアクセス判定回路14によって判定する。書込みアクセスを伴う読込みアクセスが、遅れて、第2のアドレス空間を介して行われたものであるとき、遅れて発せられたアクセスを先行して実行されているアクセスが完了するまで待機させる。

(もっと読む)

バス調停装置

【課題】リアルタイム性の要求される処理を所定時間以下で実施できると共に、リアルタイム性の要求される処理を行う場合の共通メモリへのデータアクセス量を必要以上に大きくすることなく、データ通信性能を確保することができるバス調停装置を得る。

【解決手段】リアルタイム性を要求される処理を実施する場合、CPU11の共通メモリ15へのアクセスの際の優先順位を、リアルタイム性の要求されない処理を実施する際の処理と比較して高く設定すると共に、CPU11の優先度が高く設定されている場合は、共通メモリ15へアクセスする際の最大バースト長を通常と比較して短くするよう、バス調停を実施する。

(もっと読む)

1 - 20 / 59

[ Back to top ]