Fターム[5B061DD11]の内容

Fターム[5B061DD11]に分類される特許

1 - 20 / 165

データ転送装置、データ転送方法およびプログラム

【課題】 チェーンリストによるDMA転送において転送データの任意の位置に挿入、削除を行いながら転送すること。

【解決手段】 データ転送装置は、転送元のデータの配置情報を示す第1のリスト、転送先のデータの配置情報を示す第2のリスト、挿入するデータの配置情報を示す第3のリスト、および削除開始の位置を示す削除オフセットアドレスと削除するデータのデータサイズとを有する第4のリストを取得する取得部と、受信した転送要求に従って、取得部により取得された第1のリスト乃至第4のリストから必要なリストを選択して、転送元から転送先に転送するためのデータを生成する制御部と、制御部により生成されたデータを転送先に転送する転送部と、を備える。

(もっと読む)

データ転送システム、データ転送方法及びデータ転送プログラム

【課題】メモリ上にて作成されたパケット・データの転送効率を向上させる。

【解決手段】本発明に係るデータ転送システムは、パケット・データを生成する作業領域であるメモリと、パケット・データを通信装置へ転送するDMA転送装置と、パケット・データをネットワークへ送信する通信装置とがバスで接続され、バスの最大転送データ単位でデータ転送されるデータ転送システムであって、DMA転送装置は、メモリで生成され他装置に転送するためのパケット・データを取得し、最大転送データ単位に基づき、該パケット・データのヘッダ情報を解析することにより、ヘッダ/データ間及びデータ/フッタ間における無効データの有無を解析するパケット解析手段と、パケット・データ内の無効データを削除するとともに、ヘッダ及び該無効データに後続するデータの連結と、データ及び該無効データに後続するフッタの連結とを行う無効データ削除手段とを有する。

(もっと読む)

オーディオ再生装置及びオーディオ再生方法

【課題】DMA転送を用いるオーディオ再生装置に対して、消費電力を抑制すると共に、通常再生と特殊再生の切換えを効率良く行う。

【解決手段】プロセッサAにより電源のオン・オフが制御されるプロセッサBは、圧縮された音声データをデコードして、デコード後データをメモリ102に格納する。DMA転送部110は、通常再生時においてメモリ102に格納されたデコード後データを格納順に転送する。通常再生時のDMA転送中に、通常再生と異なる特殊再生が要求されたときに、DMA転送部110は、特殊再生の種類に応じた方向と連続フレーム数とスキップフレーム数で、メモリ102に格納されたデコード後データに対して、スキップフレーム数の分のフレームのデコード後データのスキップと、連続フレーム数の分のフレームのデコード後データの連続転送とを交互にする特殊再生転送を行う。

(もっと読む)

DMA制御装置及びこれを含む画像形成装置

【課題】時間管理などを必要とせず、蓄えられた複数の要求のなかからいずれの要求を実行するか判断する調停処理を簡易化しつつ、所望の順序でモジュールを動作させる。

【解決手段】DMA制御装置は、データを記憶する主記憶部と、主記憶部のデータを読み込み、処理を実行し、処理実行後のデータを主記憶部に書き込む複数のモジュールと、モジュールに対する処理要求を発する要求発行部と、要求発行部が発した処理要求を複数蓄える要求記憶部を有し、処理要求を調停し、各モジュールの主記憶部へのアクセスを制御するDMA制御部と、を含み、要求発行部は、DMA制御部に対し、ソフトウェアで予め定められた優先度情報を送信し、DMA制御部は、優先度情報に基づき、優先度が低い処理要求よりも優先度が高い処理要求を選択し、選択した処理要求に対応するモジュールに処理を行わせる。

(もっと読む)

データ転送制御装置、データ転送制御方法、およびコンピュータシステム

【課題】トランザクションの連続性を考慮してPCIトランザクションを効率的にマージし、システム性能を向上させる。

【解決手段】データ転送制御装置は、予め設定される連続トランザクション数を格納する連続トランザクション数格納部と、PCIトランザクションを格納するトランザクションバッファと、PCIトランザクションが連続する回数を計数し、その計数値を記憶するトランザクション連続受信回数カウンタと、計数値が連続トランザクション数に達するまで、PCIトランザクションに対応するメモリトランザクションをマージして1つのメモリトランザクションとして保留するPCIトランザクションマージ部と、計数値が連続トランザクション数に達したときに、その時点で保留されているメモリトランザクションをメモリに送り出すメモリトランザクション発行部とを有する。

(もっと読む)

オーディオ再生装置及びオーディオ再生方法

【課題】DMA転送を用いるオーディオ再生装置に対して、消費電力を抑制すると共に、通常再生と特殊再生の切り替え時に誤再生を回避する。

【解決手段】DMA転送部104は、DMA転送フレーム番号レジスタ115、DMA転送フレームサイズレジスタ114、DMA転送中アドレスレジスタ111、DMA転送停止アドレスレジスタ112を備える。プロセッサAにより電源のオン/オフが制御されるプロセッサBは、DMA転送中に、通常再生とは異なる特殊再生が要求されたときに、メモリ101に格納されたフレームのうちの、該フレームの転送が完了すると、メモリ101に格納されたデコード後データの転送を停止する停止フレームの終端アドレスをDMA転送停止アドレスレジスタ112に設定する。

(もっと読む)

インターフェース回路および画像形成装置

【課題】外部記憶メディアの状態にかかわらず暗号器の正当性の確認を行うことができるようにする。

【解決手段】暗号器153に対するテストモードを設定するモード選択部171と、テストモード中のDMAコントローラ152の動作を制御するDMAコントローラ制御部174と、テストモード中の暗号器153の動作を制御する暗号器制御部173とを有し、テストモード時に暗号器153を通してメモリとSRAM151との間でテストデータの読み取り、書き込みを往復で行うようにDMAコントローラ152の転送方向を切り替え制御して暗号器153の暗号化、復号に関するテストを行わせるテスト回路170を備える。

(もっと読む)

データ転送システム及びデータ転送方法

【課題】演算装置から周辺装置へのアクセス時間及びアクセス回数を削減し、消費電力を低減できるデータ転送システムを提供する。

【解決手段】周辺装置4は、演算装置1に割込要求信号を送信する前に、周辺装置4のレジスタセット4r内のデータを主記憶装置2にDMA(Direct Memory Access)転送する。演算装置1は、割込要求信号に応答して、周辺装置4にアクセスすることなく、主記憶装置2にDMA転送されたレジスタセット4r内のデータを読み出す。

(もっと読む)

拡張メモリ付きハイブリッドドライブ、及び拡張メモリ付きハイブリッドドライブを備えた記録再生装置

【課題】光ディスクドライブと不揮発性メモリを組み合わせた拡張メモリ付きハイブリッドドライブにおいて、不揮発性メモリへのデータ転送上の制限を緩和して、拡張メモリ付きハイブリッドドライブの利便性を高めること。

【解決手段】光ディスクドライブと不揮発性メモリを組み合わせた拡張メモリ付きハイブリッドドライブ100において、光ディスク制御部10に拡張バスI/F30を設けて拡張バス35により不揮発性メモリ装置40を接続すると共に、ホストI/F13との間を拡張バス35で接続する。ホスト機器50側からのデータを拡張バスI/F30経由で不揮発性メモリ42に転送可能として、バッファメモリ14側のデータ転送要件に左右されない利便性の高い拡張メモリ付きハイブリッドドライブを提供する。

(もっと読む)

システムLSI

【課題】外部通信速度を向上できるとともに、インタフェース回路のFIFO領域の面積をも大幅に削減できるシステムLSIを提供する。

【解決手段】データ送信時にはワークRAM1から送信データをCPUを介さずに直接読み出してFIFO領域8に書き込み、データ受信時にはFIFO領域8から受信データをCPUを介さずに直接読み出してワークRAM1に直接書き込むメモリアクセス回路2と、データ送信時にはFIFO領域8に書き込まれた送信データを外部に送信し、データ受信時には外部から受信した受信データをFIFO領域8に書き込むインタフェースコントローラ3とを有するインタフェース回路9とを備え、インタフェースコントローラ3が外部と送受信中であっても、メモリアクセス回路2は、ワークRAM1とFIFO領域8との間のデータ転送を並行して実行する。

(もっと読む)

半導体装置

【課題】通信用のデータバッファに記憶容量の無駄を生じ難く、通信データのバストラフィックを低減可能とする。

【解決手段】、複数の通信チャネルを有する通信回路を内部バスにインタフェースするのに通信用ブリッジ回路を採用し、通信用ブリッジ回路には通信チャネルに一対一対応する通信チャネルバッファ領域が割り当てられるバッファメモリを採用し、バッファメモリは一方においてバスインタフェース回路を介して内部バスにインタフェースされ、他方において通信チャネルインタフェース回路を介して通信回路にインタフェースされる。通信チャネルインタフェース回路は、内部バス経由でレジスタ回路に設定された通信チャネルバッファ領域の定義情報に基づいて、通信チャネルバッファ領域から対応する通信チャネルに与える送信データを読み出し且つ通信チャネルから与えられる受信データを対応する通信チャネルバッファ領域に書き込む制御を行う。

(もっと読む)

通信制御装置及び方法

【課題】効率的なプロトコル処理を実現する通信制御装置を提供することにより、所定の通信プロトコルにしたがって外部装置からデータを受信する際の、通信処理の効率を向上する。

【解決手段】他機器との間で無線または有線による通信を行う通信制御装置は、他機器から受信した信号から受信データを生成する通信部と、通信部から主記憶部と主記憶部とは異なるバスに接続された補助記憶部とへDMAによるデータ転送を行う転送部とを有する。通信制御部は、転送部を用いて主記憶部へ受信データを転送する第1転送処理を実行し、この第1転送処理の実行中に、当該受信データのうちのヘッダを含む一部のデータを転送部を用いて補助記憶部へ転送する第2転送処理を実行する。そして、第2転送処理による補助記憶部へのデータの転送が終了すると、補助記憶部に記憶されたデータを用いてヘッダ解析が行われる。

(もっと読む)

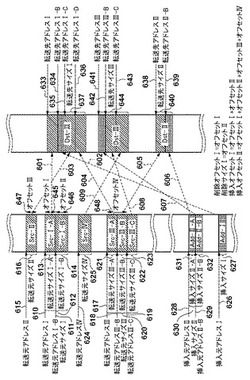

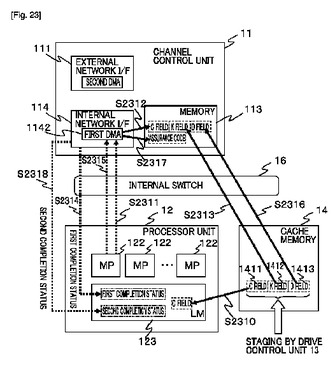

データ転送システム及びデータ転送方法

複数のデータ部からなるデータを効率よく転送する。チャネル制御部11の第1DMA1142と、第1DMA1142に転送パラメータを設定するプロセッサ部12のMP122とを備えるデータ転送システムにおいて、MP122が、CKD形式データ1400をキャッシュメモリ14からチャネル制御部11のメモリ113に転送するに際し、キャッシュメモリ14からC部1411を取得し、取得したC部1411に基づき、C部1411を付帯させた、K部1412をキャッシュメモリ14からメモリ113に転送するための転送パラメータを第1DMA1142に設定し、第1DMA1142が、転送パラメータに付帯するC部1411を取り出してメモリ113に格納し、転送パラメータに従いK部をキャッシュメモリ14からメモリ113に転送するようにする。  (もっと読む)

(もっと読む)

データ再生装置およびデータ再生方法

【課題】基本周期ごとに複数回繰返してシリアルデータ信号を転送することができない。

【解決手段】一実施形態によれば、データ再生装置4は、記録データを保持する不揮発性記憶部16と、CPU19、揮発性記憶部23、入出力バス20を有するパソコン本体4aと、それぞれ揮発性記憶部23より転送される再生データから複数のシリアルデータ信号を生成し各シリアルデータ信号を基本周期ごとに伝送路3を介して信号処理装置2へ送信するシリアル送信カード15とを備え、シリアル送信カード15は、基本周期に予め設定された送信回数を乗じて得られるCPU19の応答処理可能な時間よりも長い期間内に各シリアルデータ信号を生成し、この期間の経過後、この時間よりも長い次の期間内に各シリアルデータ信号を処理周期ごとに一定間隔でシリアル送信する。

(もっと読む)

データ転送装置及びデータ転送方法

複数のデータ転送装置を用いて行われるデータ転送を効率よく行なう。第1DMA1142、第2DMA1112、及びメモリ113を備えるチャネル制御部11と、プロセッサ部12と、記憶装置17と通信するディスク制御部13とを備えるストレージ装置10において、チャネル制御部11が、キャッシュメモリ14に格納されているデータをホスト装置3に転送する際、第1DMA1142が、プロセッサ部12から第2DMA1112の第2転送パラメータ152が付帯する第1DMA1142の第1転送パラメータ151の設定を受け付け、第1転送パラメータ151に従いキャッシュメモリ14からメモリ113への第1データ転送を行うとともに、第2転送パラメータを第2DMA1112に設定してメモリ113からホスト装置3にデータ転送するようにする。 (もっと読む)

データ転送制御装置、画像処理装置、データ転送制御方法、データ転送制御プログラム及び記録媒体

【課題】本発明は、メモリから読み出したデータを可変長圧縮して転送先メモリに転送する際のデータ転送効率の向上を図る。

【解決手段】画像処理装置1は、不揮発性メモリコントローラ2のDMAC11によってメモリ4から転送対象データを読み出して、圧縮伸長器12で可変長圧縮した後、ATAコマンド発行器13によってアドレスとデータ転送サイズを指定したATAコマンドを発行して、ATA I/F5aを介して不揮発性メモリ5の指定アドレスに指定データ転送サイズずつ転送するとともに、発行したATAコマンドのアドレスに連続する次アドレスを、ATAコマンド自動発行器14がATAコマンド発行器13に付与する。

(もっと読む)

処理要求送信回路、及び情報処理装置

【課題】データ処理部において輻輳が発生するおそれを低減しつつ、システムの性能を引き出すことが容易な処理要求送信回路、及び情報処理装置を提供する。

【解決手段】被処理データ列を受け付ける要求受付部31と、受け付けられた被処理データ列をデータ処理部5へ送信する処理要求送信部32と、被処理データ列のデータ長を計数するデータ長計数部33と、計数されたデータ長のデータをデータ処理部5が処理するのにかかる処理時間を算出する処理時間算出部34とを備え、処理要求送信部32は、一の被処理データ列をデータ処理部5へ送信した後、次に被処理データ列をデータ処理部5へ送信するまでに、一の被処理データ列についてデータ長計数部33により計数されたデータ長に基づき処理時間算出部34によって算出された処理時間以上の間隔を空けるようにした。

(もっと読む)

リモート・ダイレクト・ストレージ・アクセス

【課題】半導体ストレージのリモート・ダイレクト・アクセスに関するシステム、装置、及び方法を提供する。

【解決手段】サーバのネットワーク・インターフェース・コンポーネント(NIC)は、サーバの中央処理ユニット(CPU)及びメインメモリを迂回するネットワーク・ストレージ・アクセス・リンクによって、半導体ストレージモジュールにアクセスする。NSAリンクは、半導体ストレージのリニアな「メモリビュー」にリモート・エンティティーを提供するために、リモート・ダイレクト・メモリ・アクセス(RDMA)をサポートする。NSAリンクは、NIC及びストレージ・コントローラと直接接続するアービターを含んでもよい。

(もっと読む)

独立論理アドレス空間とそれぞれに対するアクセス管理を提供する方法および装置

【課題】I/Oアクセスを制御するための技術、特に外部装置からのアクセス要求を制御するための方法および装置を提供する。

【解決手段】コマンド受信部は、外部のアクセス要求主体から、アクセス対象となるアドレスとアクセス要求主体を識別するためのIOIDと共に、データにアクセスするためのコマンドを受信する。IOIDにより、アクセス判定部は、アクセス要求主体が目的のアクセス先にアクセスする権限があるかを判定する。アクセス判定部は、プロセッサの空間における論理アドレスの基本管理単位としてのページごとに、アクセス要求主体のアクセス可否を判定する。

(もっと読む)

DMAセキュリティチェック回路及びDMAセキュリティチェック方法

【課題】IO TLB(I/O Translation Look aside Buffer)でキャッシュミスした場合にDMAが待たされることを防止する。

【解決手段】IOV(I/O Virtualization) HBA(Host Bus Adapter)に対応したDMA(Direct Memory Access)セキュリティチェック回路が、HBAからのDMAリード要求に対しディスクリプタフェッチを検知した場合に、当該DMAリード要求のリプライデータの中から抽出した論理アドレスと、当該リプライデータに含まれるリクエストIDとが同じゲスト空間のものであるかを判定し、同じゲスト空間のものである場合に当該リプライデータに含まれるアドレスが適切であると判断する。

(もっと読む)

1 - 20 / 165

[ Back to top ]