Fターム[5B061RR01]の内容

Fターム[5B061RR01]の下位に属するFターム

Fターム[5B061RR01]に分類される特許

1 - 11 / 11

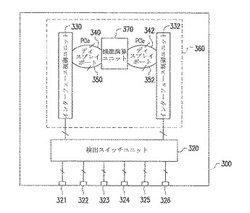

複数のデータ接続ポートを備えた電気装置

【課題】複数のデータ接続ポートを備えた電気装置を提供する。

【解決手段】電気装置は、本体、処理ユニット、及び検出スイッチユニットを備える。本体には、M個の面と面上に配置されるN個のデータ接続ポートを備える。処理ユニットは、第1のインターフェース制御ユニットと第2のインターフェース制御ユニットを備える。検出スイッチユニットは、データ接続ポートが接続されているかどうかを検出する。 i番目とj番目のデータ接続ポートの接続を検出しているとき、検出スイッチユニットはi番目とj番目のデータ接続ポートをそれぞれ第1のインターフェース制御ユニットと第2のインターフェース制御ユニットによって制御されるように割り当て、i番目とj番目のデータ接続ポート以外のデータ接続ポートを無効にする。したがって、電気装置はデータ接続ポートの柔軟性の形式により他の電気装置に接続することができる。

(もっと読む)

半導体集積回路

【課題】内部プロセッサ、メインメモリ用のメモリI/F、外部プロセッサを有するデバイス用の外部I/F、及びレジスタを備えた半導体集積回路において、内部プロセッサからレジスタ制御を行った場合と外部プロセッサからレジスタ制御を行った場合との応答性能差異を少なくすると共に、外部プロセッサからメインメモリへのアクセス制御を行う場合の応答性能を向上させる。

【解決手段】半導体集積回路(SoC1cで例示)は、プロセッサ11及びメモリコントローラ15がバス接続された第1の内部バス(バス10で例示)とレジスタ31がバス接続された第2の内部バス(バス30で例示)とを含む複数の内部バスを備える。外部I/F16は、第1の内部バスと第2の内部バスとの間に多重バス接続され、メインメモリにメモリコントローラ15を介してアクセスする場合とレジスタ31にアクセスする場合とで、利用する内部バスを切り替える。

(もっと読む)

データ転送方法

【課題】複数のUSBインターフェースを用いて、USB規格以上のデータ転送速度を実現する。データ転送中における、USBケーブル接続等によるUSBインターフェースの追加と削除を可能とする。

【解決手段】複数のUSBインターフェースを用いてデータを並列転送する。並列転送するためのデータ振り分け機能と、データ復元のためのデータ並べ替え機能を備える。データ転送を止めることなく、USBインターフェースの追加と削除を可能とするUSBコンフィグレーション手段を備える。

(もっと読む)

バスシステムおよびそのデッドロック回避回路

【課題】スプリットトランザクションにより複数のスレーブへの同時アクセスを許容したシステムにおいて、デッドロックの発生を防止する。

【解決手段】先行トランザクション情報管理部410は、対応するマスタから複数のスレーブの何れかに先に発行された先行トランザクション情報を管理する。発行停止判定部420は、先行トランザクション情報に基づいて、対応するマスタから新たに発行されたトランザクションがデッドロックの要因になるか否かを判定する。レスポンス出力制御部430は、先行トランザクション情報に基づいて、対応するマスタへ返送すべきレスポンスを制御する。退避バッファ470は、先行トランザクションに対する複数のスレーブからのレスポンスが予め期待された順序とは異なる順序で戻ってきた場合に、そのレスポンスを退避する。

(もっと読む)

回路構成におけるデータ交換を制御するための回路構成、および方法

本発明は、回路構成における、データシンクの少なくとも1つの集合と、データソースの少なくとも1つの集合との間のデータ交換を制御する方法、および回路構成に関し、当該回路構成は、少なくとも1つの調停ユニットを有する。さらに、調停ユニットは、所定の順番にしたがって、第1のデータソースのアドレス、および、要求信号を出力する第1のデータシンク(データシンク調停)を選択し、または、第1のデータシンクのアドレス、および、有効信号を出力する第1のデータソース(データソース調停)を選択する。第1のデータソースのデータは、第1のデータシンクに格納される。 (もっと読む)

情報処理装置、データ伝送装置及びデータ伝送方法

【課題】伝送路の縮退をおこなっても、データ伝送のスループットの低下を抑制する。

【解決手段】送信側マルチプレクサ103は、セレクタ102dをバイパスして、特殊パケットを送信できる経路が接続される。受信側のデータ伝送装置200aには、受信器202a〜202dによって受信された伝送データを、受信側第1マルチプレクサ204をバイパスしてパケットを受信できる経路が接続される。当該経路の途中には受信データのデータ幅を変換する受信側第2マルチプレクサ206が設けられる。

(もっと読む)

データ転送システム

【課題】PCI Express スイッチを含むシステムにおいて、用途に最適な経路を提供することを可能にしたデータ転送システムを得る。

【解決手段】(a)に示すように、メインボード100におけるルートコンプレックス110からスロット140a及びスロット140bまでの経路が、スイッチ130を経由するように設定が施された構成と、(b)に示すように、メインボード100におけるルートコンプレックス110からスロット140a及びスロット140bまでの経路が、スイッチ130を迂回するように設定が施された構成とを、マルチプレクサ120a〜120cにより切り替えて、用途に応じて使用することを可能にしている。

(もっと読む)

PCIエクスプレス・パケット・ダイジェストの変更のデバイス、システムおよび方法

【課題】PCIエクスプレス・パケット・ダイジェストの変更のデバイス、システムおよび方法を提供する。

【解決手段】例えば、装置は、ダイジェスト部の1つ以上のビットが非ECRCデータを搬送するクレジット・ベース・フロー制御相互接続トランザクション層パケットを生成する、クレジット・ベース・フロー制御相互接続デバイスを含む。

(もっと読む)

画素データ転送制御装置及び画素データ転送制御方法

【課題】出力データセレクタを構成する論理回路の回路規模を小さくすることを可能にする画素データ転送制御装置及び画素データ転送制御方法を提供する。

【解決手段】

本願発明の画素データ転送制御装置100は、m色の色要素の画素データにより構成されるカラー画素データが格納されるメモリからnバイト幅を有する入力バス160を介して読み出して、該色要素に対応づけた出力バス(170〜172)を介して画像処理回路に転送する制御を行う装置であり、カラー画素データを構成する1の色要素の画素データを格納する記憶容量を備えるバッファであって、mとnとの公倍数に相当する個数のバッファ(101〜112)と、カラー画素データをバッファ列(101〜112)のバッファに順次格納させる入力データセレクタ120と、同一色要素の画素データを格納する複数のバッファから、画素データを各色要素に対応づけられた出力バス(170〜172)に出力する出力データセレクタ(130〜132)と、を備える。

(もっと読む)

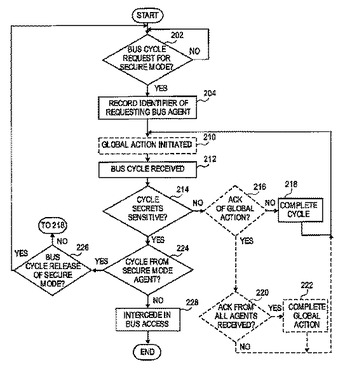

セキュアな実行中のリソースのデッドロックなしのバス保護のシステム及び方法

セキュアな実行中のメモリ・リソース及びI/Oリソースのデッドロックのないバス保護の方法及びシステム。バス・サイクルによって、セキュア実行モードへバス・エージェントが入ることが起動される。チップセットは、セキュア・モード・プロセッサの識別子を記録する。その後、チップセットは、セキュア・モード・プロセッサがセキュア・モードを出る前に別のバス・エージェントが、セキュリティ面で配慮を要するバス・サイクルを試行する場合、仲裁する。  (もっと読む)

(もっと読む)

バス調停回路、情報処理装置、並びに、そのプログラムおよび記録媒体

【課題】 帯域保証が必要な同期データを構成するデータ列を繰り返し伝送可能な同期デバイスが、より確実に同期データを伝送できるようにバスを調停可能なバス調停回路を実現する。

【解決手段】 バス調停回路16は、外部バスI/F20による同期データの伝送を検出した場合、レジスタ33に格納された予測用情報に基づいて、次の同期データのデータ列のデータ伝送開始時点の予測結果よりも前の調停開始時点を決定すると共に、外部バスI/F20によって使用権が要求されていなくても、当該調停開始時点から、前記外部バスI/F20へ使用権を与えるための前記バスの調停処理を開始する。これにより、外部バスI/F20がバス使用権を要求してから調停処理を開始するよりも、早い時点で、遅滞なく、外部バスI/F20にバス使用権を与えることができる。

(もっと読む)

1 - 11 / 11

[ Back to top ]