Fターム[5B062EE09]の内容

マイクロコンピュータ (2,258) | チップ外部との入出力 (243) | チップ内機能部と外部との直接接続 (66) | チップ内メモリとの直接接続 (38)

Fターム[5B062EE09]に分類される特許

1 - 20 / 38

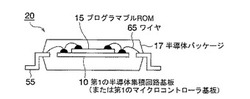

シングル・チップ半導体集積回路装置の製造方法、プログラムデバッグ方法、マイクロコントローラの製造方法

【課題】短時間で、マスクROMを備えたシングル・チップの半導体集積回路装置を製造すること。

【解決手段】第1の集積回路(12)および第1のマスクROM(11)を有する第1の半導体集積回路基板(10)とプログラマブルROM(15)とが搭載された第1の半導体集積回路装置(20)の状態において、第1のマスクROM(11)が第1の内部バス(13)から電気的に切り離された状態で、その第1の集積回路(12)とプログラマブルROM(15)とを使用して決定された最終的なプログラムを、第1の半導体集積回路基板(10)と実質的に同一構成の第2の半導体集積回路基板(100)の第2のマスクROM(110)に記憶することにより、最終製品としての第2の半導体集積回路装置(200)を製造する。

(もっと読む)

半導体装置及びマルチプロセッサシステム

【課題】符号データ用バスを使用してイニシャルプログラムの書き込みを可能にすることで、IPL用バスに対応する外部端子を省略する。

【解決手段】プログラムを格納可能なメモリ(102)と、上記メモリに格納されているプログラムを実行可能なCPU(101)と、データストリームを伝達可能な符号データ用バスに結合される第1外部端子(EX_D、EX_CS、EX_WE、EX_OE)とを含んで半導体装置(210)を形成する。上記半導体装置(210)には、上記第1外部端子を介して上記メモリにイニシャルプログラムを書き込むための動作を制御可能な制御回路(103)を設ける。この制御回路は、上記イニシャルプログラムを上記メモリに書き込むための書き込み用アドレス信号を生成する回路を含む。これにより、符号データ用バスを使用したイニシャルプログラムの書き込みが可能になるので、IPL用バスが不要とされる。

(もっと読む)

電子装置

【課題】マイクロコンピュータとメモリを接続する信号ラインの数を抑えることができる電子装置を提供する。

【解決手段】モータ制御装置1は、マイクロコンピュータ11と、メモリ17とを備えている。マイクロコンピュータ11の駆動信号を伝達するための信号ライン190a〜190fを備えている。マイクロコンピュータ11が動作状態であり、かつ、信号ライン190a〜190fがハイインピーダンス状態のとき、マイクロコンピュータ11とメモリ17の間で、信号ライン190a〜190dを利用してチップセレクト信号等を伝達する。そのため、マイクロコンピュータ11とメモリ17の間に、これらの信号を伝達するための専用の信号ラインを別途設ける必要がない。従って、信号ラインの数を抑えることができる。

(もっと読む)

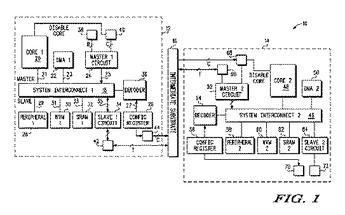

集積回路を相互接続するための技術

処理コア(20,48)及びオンボードメモリ(30,32,60,62)をそれぞれ有する2つの集積回路ダイ(12,14)は、相互接続されて一体にパッケージ化されて、多チップモジュール(10)を形成する。第1のダイ(12)はプライマリであると考えられ、第2のダイ(14)はセカンダリであると考えられ、インターポーザー(16)を介して接続されている。第1及び第2のダイは同じ設計であってよいため、周辺装置(28,56)及びメモリなど同じリソースを有してよく、好適には共通のシステム相互接続プロトコルを有する。第2のダイのコアは使用不能とされるか、少なくとも低電力モードとされる。第1のダイは、第2のダイに対し相互接続を行うための最小の回路(34,26)を備える。第2のダイはいくつかの必要なインタフェース回路(52)と、1つのアドレス変換器(50)とを有する。その結果、第1のダイのコアは、第2の集積回路のメモリ及び他のリソースを用いるトランザクションを、そのメモリ及びリソースが第1のダイ上に存在する場合のように、実行することができる。  (もっと読む)

(もっと読む)

マルチチッププロセッサ

【課題】

プロセッサコア数を可変とすることによるスケーラブルな演算性能、および自由度が高く再構成可能なプロセッサコア間結合トポロジを特徴とする、組み込み向け低コストマルチプロセッサを実現する。

【解決手段】

少なくともプロセッサコアとメモリとを有するユニットチップを複数積層して構成されるマルチプロセッサであって、前記ユニットチップは、複数のプロセッサコアと、複数のメモリと、前記プロセッサコアと前記メモリとチップ外部との接続関係を設定する構成制御部と、前記プロセッサあるいは前記メモリあるいは前記構成制御部と、積層接続される他のユニットチップとのトランザクションを伝送するチップ接続部とを有する構成とし、前記チップ接続部は当該ユニットチップの辺部に回転対称に配設され、積層構成される前記ユニットチップのいずれかのユニットチップが回転接続されるようにした。

(もっと読む)

集積回路及び電子機器

【課題】インターフェースとしての周辺デバイスが接続される多機能な電子機器に適した集積回路を提供すること。

【解決手段】主処理部と周辺デバイスを接続する周辺接続ポートとが内部バスで接続された集積回路は、周辺接続ポートを制御し、周辺接続ポートに接続された周辺デバイスからの割り込み及びデータ転送の制御を主処理部の代わりに行う補助処理部を備え、主処理部は、当該主処理部の内部メモリ空間の一部として、補助処理部が有するメモリリソースを利用する。

(もっと読む)

マイクロコンピュータ

【課題】セキュリティの向上を実現可能なマイクロコンピュータを提供する。

【解決手段】例えば、マイクロコンピュータに含まれる不揮発性メモリNVMEMにおいて、そのメモリアレイNVARY内にデータ保持寿命が10年以上となる第1メモリセル領域ARY1と、データ保持寿命が1〜365日となる第2メモリセル領域ARY2を設ける。このデータ保持寿命の違いを実現するため、ARY1に消去・書き込みを行う際には、基準電圧生成回路VRFGEN1に基づく消去・書き込み電圧を用い、ARY2に消去・書き込みを行う際には、基準電圧生成回路VRFGEN2に基づき、ARY1よりも絶対値が小さい消去・書き込み電圧を用いる。

(もっと読む)

マイクロコンピュータの識別情報管理システム及び方法

【課題】フラッシュメモリを備えるマイクロコンピュータにおいて、識別情報の管理を容易にする。

【解決手段】本発明に係るシステム1は、フラッシュメモリ21にユーザプログラムを含む情報を書き込むフラッシュプログラミング手段2と、ユーザプログラムを通信ネットワーク15を介してユーザ側からホスト側に送信する第1のユーザプログラム送信手段3と、ユーザプログラムを受信するユーザプログラム受信手段4と、ユーザプログラムの識別を可能にするカスタムコードを採番するカスタムコード採番手段5と、カスタムコードを前記フラッシュプログラミング手段2に送信する第1のカスタムコード送信手段6と、カスタムコードを前記マイクロコンピュータ11内において記憶するカスタムコード記憶手段7とを備える。

(もっと読む)

マイクロコンピュータ及びその検査方法

【課題】ROM内の配線不良に伴うデータ読出遅延を、より確実に検査することが可能なマイクロコンピュータ及びその検査方法を提供する。

【解決手段】マイクロコンピュータ1内のCPU10は、外部のテスタ2から供給されるクロックCLKに同期してROM20からデータDnを順次読み出し、テスタ2にデータDnの正常性と読出速度とを検査させる。また、CPU10は、データDnをデコードして分岐命令が得られた場合、次にデータを読み出すべきアドレスに代えて、前記分岐命令による分岐先アドレスAbからデータを読み出してテスタ2に検査させる。

(もっと読む)

制御装置

【課題】制御装置内に設けられた複数のマイコン間の通信において、データの授受時間の制限を軽減することが出来る制御装置を提供する。

【解決手段】信号出力部17から出力される切替信号の出力値が第1の値の場合は、マイコン11とEEPROM31との間でデータの授受を行い、信号出力部17から出力される切替信号の出力値が第2の値の場合は、マイコン21とEEPROM31との間でデータの授受を行う。マイコン11とマイコン21との間におけるデータの授受に際して、クロックの出入力作業は、EEPROM31との間においてデータを授受する一方のマイコンのみが行えば良く、また、これにより、ACK,NACKの確認作業が不要となるため、制御装置100内に設けられたマイコン11とマイコン12との間の通信において、データの授受時間の制限を軽減することが出来る。

(もっと読む)

制御装置

【課題】制御装置内に設けられた複数のマイコン間の通信において、データの授受時間の制限および一度に授受出来るデータ量の制限を軽減するとともに、一方のマイコンから出力されたデータを、上書き等がなされることなく、他方のマイコンに順次入力することが出来る制御装置を提供する。

【解決手段】信号出力部17から出力される切替信号の出力値に応じて、マイコン11またはマイコン21とEEPROM31との間にて行うデータの授受動作を切り替える。そして、EEPROM31にデータを記憶する場合は、記憶部32におけるデータが記憶されていないアドレスを検出し、検出したアドレスの中から最も上段にあるアドレスの領域にデータの入力を行い、EEPROM31からデータを読み出す場合は、データが記憶されたアドレスを検出し、検出したアドレスの中から最も上段にあるアドレスの領域からデータの出力を行う。

(もっと読む)

電気機器

【課題】電気的に書き換え可能な不揮発性メモリを内蔵した不揮発性メモリ内蔵マイクロコンピュータを備える電気機器であって、不揮発性メモリの書き込みが容易であり、尚かつ、不揮発性メモリ内蔵マイクロコンピュータの破損を防止することができる電気機器を提供する。

【解決手段】フラッシュマイコン12と、フラッシュマイコン12が実装されているプリント基板と、前記プリント基板外に設けられるフラッシュマイコン書き込み用コネクタ17と、フラッシュマイコン12とフラッシュマイコン書き込み用コネクタ17との電気的接続/遮断を切り替えるスイッチ16とを備え、フラッシュマイコン12が、書き込みモードのときにスイッチ16をオンにし、前記書き込みモード以外のときにスイッチ16をオフにする空気調和機。

(もっと読む)

マイクロコンピュータ

【課題】マイクロコンピュータに内蔵されたフラッシュメモリの使い勝手を向上させる。

【解決手段】本発明のマイクロコンピュータは、CPUとI/Oポートとフラッシュメモリとランダムアクセスメモリとを単一の半導体チップに構成される。フラッシュメモリは、複数の一括消去可能な記憶領域に分割され、書換え制御プログラムと転送制御プログラムとを格納し、消去・書込み等の動作状態を設定するコントロールレジスタを有する。コントロールレジスタは、消去動作を指示するビット、書込み動作を指示するビット、ベリファイ動作を指示するビット、および消去対象となる記憶領域を指定するビットとを有し、CPUによって制御される。CPUは、転送制御プログラムを実行して、書換え制御プログラムを前記ランダムアクセスメモリへ転送し、さらに、転送された前記書換え制御プログラムを実行して、用意されたデータをフラッシュメモリへ書き込む。

(もっと読む)

制御プログラム及びマイクロコンピュータ

【課題】EEPROMライタを有効に活用する。

【解決手段】マイコン1は、EEPROMライタ2からEEPROM通信のプロトコルを介して、情報を書き込む旨の信号である書込指令信号を受け付けて、この書込指令信号が受け付けられた場合に、EEPROMライタ2からEEPROM通信のプロトコルを介して書き込み対象の情報を受信する情報受信部12と、情報受信部12によって受信された書き込み対象の情報を、フラッシュメモリ11に書き込む書込実行部13と、を備えている。

(もっと読む)

データ処理装置

【課題】フラッシュメモリの書き込み、消去、ベリファイ時に生成される電源の測定は、テスタでの測定が不可のため、電源線にプローブを当てて測定するため、測定に手間を要するとともに正確な測定が困難であった。

【解決手段】第1の電圧伝達手段を介して入力されたアナログ信号をデジタル信号に変換するA/D変換器と、フラッシュメモリに書き換え電圧を供給するフラッシュ電源発生回路とを備え、第2の電圧伝達手段はその書き換え電圧を前記A/D変換器の入力端子側に伝達するものである。

(もっと読む)

セキュリティ保護機能付きマイクロコンピュータ

【課題】内蔵の書き換え可能な不揮発性メモリおよび他のリソースへのセキュリティ管理情報に対する保護を強化したセキュリティ保護機能付きマイクロコンピュータを提供する。

【解決手段】セキュリティ保護機能付きマイクロコンピュータ1は、セキュリティフラグを書き込む領域を有する1回だけ書き換え可能な不揮発性メモリであるPROM11と、PROM11に書き込まれたセキュリティフラグの設定に従って、セキュリティ保護機能付きマイクロコンピュータ1が内蔵する各種リソースに対するCPU13からのアクセスを制御するアクセス制御部12と、を有する。

(もっと読む)

マイクロコンピュータ

【課題】本発明は、自己の動作を確実に自己検証できるマイクロコンピュータチップを得ることを目的とする。

【解決手段】本発明によるマイクロコンピュータは、チップ(1)外部との信号授受のための複数のパッド(8、15、19)と、同一のパッド(8、15)に接続された出力バッファ(7、14)および入力バッファ(9、16)と、入力バッファ(9、16)の後段に設けられ、対応する出力バッファ(7、14)から出力される信号を入力バッファ(9、16)を介して受ける第1のラッチ(11、18)とを備え、第1のラッチ(11、18)は、複数のパッド(8、15、19)のうちの一のパッド(19)を介して外部より付与される書き込み信号に応答して、入力バッファ(9、16)を介して受ける信号をラッチし、第1のラッチ(11、18)にラッチされた信号を検証する検証機能を装備されたCPU(3)をさらに備える。

(もっと読む)

マイクロコンピュータおよびマイクロコンピュータ識別方法

【課題】マイクロコンピュータにおいて、セルフプログラミング動作が可能か否かを効率的かつ確実に識別可能にする。

【解決手段】セルフプログラミング動作が可能なマイクロコンピュータ1において、内蔵するROM4の所定の領域に、セルフプログラミング動作が可能であることを示す情報4aを予め記録することで、該情報4aを読み出せば短時間で容易かつ確実にセルフプログラミング動作が可能なマイクロコンピュータであることが識別できる。

(もっと読む)

不揮発性メモリ内蔵マイクロコンピュータチップ、及びその検査方法

【課題】ロジックテスターによるマイコン部の検査の工程を省略し検査コストを削減できるような不揮発性メモリ内蔵マイコンを提供する。

【解決手段】不揮発性メモリ内蔵マイコン110の不揮発性メモリ141に、検査データと期待値データとをメモリテスター100から与えて記録しておく。不揮発性メモリ141にアドレス信号を与えると、検査データに基づく検査信号S141aと期待値データに基づく期待値信号S141bとが逐次出力され、検査信号S141aに基づく検査信号S142aが伝えられマイコン部の各回路ブロックは駆動され、駆動結果である検査結果信号S135aが得られ、検査結果信号S135aに基づく検査結果信号S142bと、期待値信号S141bとがメモリI/Fを介して外部に出力される。メモリテスター100はその外部に出力された各信号を比較し、マイコン部が正常に動作したかを判定する。

(もっと読む)

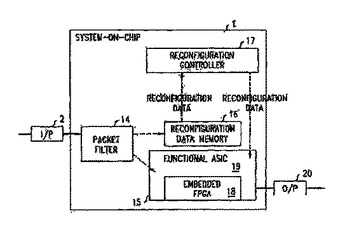

ICアーキテクチャを再構成するための方法および装置

再構成可能なハードウェア・アーキテクチャが、ICアーキテクチャ15の静的な部分および再構成可能な部分をそれぞれ定義するASIC 19および埋め込みFPGA 18をシステム・オン・チップ1の形で備えている。着信するイーサネットまたは他の形式のパケットがパケット・フィルタ14に渡され、パケット・フィルタ14が、これらのパケットに再構成データが含まれていることを検出する。この再構成データを用いてFPGA 18が更新される。  (もっと読む)

(もっと読む)

1 - 20 / 38

[ Back to top ]