Fターム[5B077GG11]の内容

Fターム[5B077GG11]の下位に属するFターム

非同期信号サンプリングの制御手段 (104)

ウェイト(レディ)信号を用いるもの (13)

クロック周波数の切り替え (56)

クロック位相の切り替え (13)

クロックの一時停止/禁止 (12)

Fターム[5B077GG11]に分類される特許

1 - 20 / 32

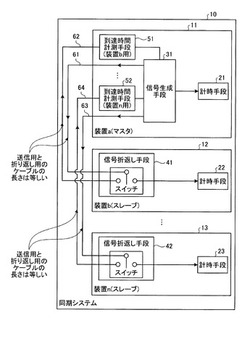

同期制御システム

【課題】マスタとスレーブを有し時計により同期する同期システムを得る。

【解決手段】生成部と送受信時間の計測部を有するマスタ11、第1折返し部を含みリセットを受信すると第1時刻に動作する第1スレーブ12、第2折返し部を含みリセットを受信すると第2時刻に動作する第2スレーブ13、第1信号を第1スレーブへ送信する第1ケーブル、それと等長で第1信号をマスタへ送信する第2ケーブル、第2信号を第2スレーブへ送信する第3ケーブル、それと等長で第2信号をマスタへ送信する第4ケーブルを備え、計測部は第1信号が第1信号折返し部を経て受信される時間の半分の第1時間と第2信号が第2信号折返し部を経て受信される時間の半分の第2時間を算出し、生成部は到達時間の中で第2時間が最長の場合は第2時刻を0に第2時間と第1時間の差を第1時刻に設定し、第1時間が最長の場合は第1時刻を0に第1時間と第2時間の差を第2時刻に設定する。

(もっと読む)

ユニバーサルシリアルバス(USB)システムのオンライン較正方法及びその装置

【課題】USBホストとデバイスの終端抵抗特性を同時に参考することができ、USB装置同士の適応性を向上させる。

【解決手段】USBシステムに適用するオンライン較正方法は、複数の対のチャープ信号を提供するステップと、前記チャープ信号を検出し、所定数量の前記チャープ信号を発信する前に、前記デバイスの終端抵抗とそれに接続されるホストの終端抵抗に電源を加えて、前記チャープ信号の準位を変更するステップと、前記変更後のチャープ信号のノード上での準位変化を検出するステップと、前記準位変化に基づきオンライン較正を行い前記変更後のチャープ信号の準位を所定範囲内に維持するステップと、を有する。

(もっと読む)

シリアル通信システム

【課題】通信効率を向上できるシリアル通信システムを提供する。

【解決手段】送信部21は、データパケットに所定のSKIPOS送信間隔でSKIPオーダード・セット(SKIPOS)80を挿入して受信部60に送信する。各受信回路64−1〜64−Nのエラスティックバッファは、PLL回路22とPLL回路65の各クロックの周波数差を吸収するように、SKIPOS80にSKPキャラクタを挿入又は削除する。SKIPOS受信制御部53は、SKIPOS80の正常受信時の受信間隔を検出してルートコンプレックスデバイス1に送信し、SKIPOS送信制御部11は、上記送信されたSKIPOS80の正常受信時の受信間隔に基づいて、エンドポイントデバイス2がデータパケットを正常に受信できるように、SKIPOS送信間隔を変更する。

(もっと読む)

通信ユニット及び情報処理装置

【課題】第1の装置及び第2の装置間との間に設けられる通信ユニットにおいて、第2の装置と前記第1の装置とを接続させるためのデバイスが動作可能な状態であることを保証可能な通信ユニットを提供する。

【解決手段】PCI Express/光ケーブル変換ボードは、電気式カードエッジ50と、PCI Expressスイッチ51と、2つの光ケーブルコネクタ52a,52bと、電源遅延回路53とを有する。電気式カードエッジ50にはPCI Expressスイッチ51が配線接続される。光ケーブルコネクタ52には、光トランシーバ600を介して光アクティブケーブル500が接続される。電源遅延回路53は、PCI Expressスイッチ51及び光アクティブケーブル500に接続される光トランシーバ600の起動タイミングを制御する。

(もっと読む)

通信ユニット、通信システムおよび通信ユニットの制御方法

【課題】クロックの周波数が異なる機器間であっても通信を適切に行えるようにする通信ユニット、通信システムおよび通信ユニットの制御方法を提供する。

【解決手段】クロックアイソレーション機能によりPCI Expressブリッジチップ13のカードエッジ側ポートと光ケーブル側ポートとを別々のクロックで動作する領域として分離し、光ケーブル側ポートで用いるクロック(第1のクロック)を、PCI Express/光ケーブル変換ボード10上のクロック源14から供給する。そして、通信の接続先となるプリンタ400のクロック(第2のクロック)を取得し、クロック源14が発生する第1のクロックの周波数が第2のクロックの周波数と異なる場合に、周波数調整部15が、第1のクロックの周波数を第2のクロックの周波数と一致するように調整する。

(もっと読む)

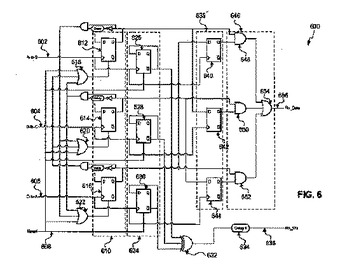

データ同期化回路、通信インタフェース回路及び通信装置

【課題】データを同期化させるクロック信号の許容される周波数の範囲を広げる。

【解決手段】実施形態によれば、データ同期化回路SYNC0は、データホールド回路BLC0と、受信タイミング生成回路BLB0と、更新タイミング調整回路BLE0とを備えている。データホールド回路BLC0は、クロック信号CLK_A0に同期したデータDOUT0を受信して、当該データDOUT0がクロック信号CLK_Bに同期化されたデータSYNC_DATA0を出力する。更新タイミング調整回路BLE0は、受信タイミング生成回路BLB0内のDフリップフロップ230_0,230_1及び230_2の値の更新のタイミングを、クロック信号CLK_Bに同期した更新イネーブル信号UE0に基づいて制限する。

(もっと読む)

情報処理装置又は情報処理方法

【課題】 外部デバイスコントローラの外部デバイスから受信するデータが、外部デバイスコントローラの出力クロックに対して1サイクル以上遅延する場合、従来の構成では遅延の有無を検出できないことがある。

【解決手段】 外部デバイスコントローラのデータ取り込みタイミングを調節する際に、所定のゲーティング情報に基づいて外部デバイスコントローラの出力クロックをゲーティング又はゲーティング解除することで、データ取り込みタイミングを調節するためのキャリブレーションの精度を向上させる。

(もっと読む)

非同期統合アップサイジング回路

【課題】システムオンチップに採用するのに適する非同期統合アップサイジング回路を提供する。

【解決手段】非同期統合アップサイジング回路は非同期パッカーと非同期アンパッカーを具備する。非同期パッカーは、非同期ブリッジ及びアップサイジングに共通で用いられ、ライトチャンネルデータをバッファリングするライトバッファと、バーストライト時に前記ライトバッファに入出力される前記ライトチャンネルデータに対するチャンネル圧縮を第1及び第2クロックによって各々制御する第1及び第2非同期パッキング制御器を含む。また、非同期アンパッカーは、前記非同期ブリッジ及びアップサイジングに共通で用いられ、リードチャンネルデータをバッファリングするリードバッファと、バーストリード時に前記リードバッファに入出力される前記リードチャンネルデータに対するチャンネル圧縮を前記第1及び第2クロックによって各々制御する第1及び2非同期アンパッキング制御器を含む。

(もっと読む)

データ転送装置、データ転送制御方法、データ転送制御プログラム及び記録媒体

【課題】本発明は、複数のデータ転送制御部から印刷部側に画像データを同期転送する複合装置、プリンタ装置等のデータ転送装置、データ転送制御方法、データ転送制御プログラム及び記録媒体に関する。

【解決手段】複合装置1は、同期をとって送信する必要のある画像データを複数の転送制御部7a、7bから印刷処理部8に送信する場合に、各転送制御部7a、7bが受信した基準信号Ksを相互に基準信号入力・転送回路30a、30b及び基準信号転送路11を通して比較基準信号Kshとして送受信し、該基準信号Ksと該比較基準信号Kshの時間差を検出して、該時間差であるスキュー値に基づいて印刷処理部8へのデータ送信タイミングを調整する。したがって、印刷処理部8と各転送制御部7a、7bとの間にスキューがある場合にも、該スキューを考慮した画像データの転送を行うことができる。

(もっと読む)

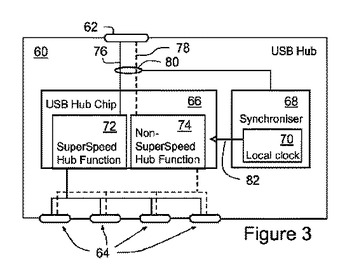

分散型の同期されたクロックアーキテクチャのためのジッタ低減方法およびジッタ低減装置

ローカルクロックと、リピータ回路とを有するUSBハブにアタッチされた、同期されたUSBデバイスのローカルクロックにおけるジッタを低減する方法であって、そのUSBハブを使用して、或るデータストリームビットレートを有するUSBデータストリームを観測すること、そのUSBハブがUSBデータストリームの中の周期信号構造を復号すること、そのUSBハブが、周期信号構造を復号したことに応答してイベント信号を生成すること、およびそのUSBハブが、そのUSBハブのローカルクロックの周波数を周期イベント信号にロックすることを備える方法。USBハブのローカルクロックは、データストリームビットレートの周波数の実質的に整数倍でUSBハブのリピータ回路のためのクロック制御源となるように適合される。  (もっと読む)

(もっと読む)

メモリデバイス、ホストデバイスおよびサンプリングクロックの調整方法

【課題】高速転送が可能なメモリカード1、高速転送が可能なホストデバイス2、および、高速転送が可能なサンプリングクロックの調整方法を提供する。

【解決手段】

メモリカード1は、コマンド信号、レスポンス信号、データ信号およびステータス信号を、クロック信号と同期して送受信するための制御を行うメモリコントローラ11と、クロック信号をサンプリングクロック信号として位相を調整するためにホストデバイス2が使用するチューニングパターン信号を送信するためのチューニングパターン信号を記憶するメモリ側パターン信号記憶部15とを有し、第1のチューニングパターン信号をコマンドライン32を介して、第2のチューニングパターン信号をデータライン21を介して、同時に送信する。

(もっと読む)

第2のリンクを介した内部リンクの観察

【課題】シリコンコンポーネントに集積されるようハードウェアを実装することにより、例えば、他の相互接続を介し、既存の外部インターフェースを用いてMCPからの可視性を提供する。

【解決手段】第1のクロック信号の第1のクロック周期間において、パッケージ内リンクを介し、マルチチップパッケージ(MCP)の第1のダイで受信された当該MCPの第2のダイからの第1のデータをセレクタからの出力用に選択する段階と、第2のクロック周期間において、第2のダイから第1のダイに送信される第2のデータをセレクタからの出力用に選択する段階と、第1のデータおよび第2のデータを外部リンクを介してMCPから送信する段階と、を備える。

(もっと読む)

信号同期化方法及び信号同期化回路

【課題】デバイスがプロセッサからの前の要求と連続する次の要求とを区別可能にする。

【解決手段】プロセッサからデバイスに対する最初の要求を行うときには要求を表す信号である信号REQinは立ち上がりアクティブ状態になるが(時刻t3)、プロセッサが連続して次の要求を行うときには信号REQinはアクティブ状態を継続するだけである(時刻t14)場合において、マスク開始時刻t6までは信号REQinをそのまま信号REQoutとして要求先のデバイスに出力し、マスク開始時刻t6からマスク継続時間Tmが経過するまでの時間である時刻t6〜t14の間のみ信号REQoutをマスクして非アクティブ状態にして要求先のデバイスに出力する。これにより、マスク継続時間が経過したあとは信号REQoutが非アクティブ状態からアクティブ状態になるため、デバイスは前の要求と次の要求とを区別できる。

(もっと読む)

伝送制御回路及びそれを備えた半導体記憶装置

【課題】信号を伝送する際の遅延の変動に対し、適切な出力タイミングを自動的に制御し、高速な伝送速度と不良の低減が可能な伝送制御回路を提供する。

【解決手段】本発明の伝送制御回路は、制御信号SMに同期して入力された信号を信号バスDBに伝送させ、制御信号SBに同期して出力する信号伝送回路20と、信号伝送回路20に制御信号SBを供給し、信号バスDBの出力タイミングを制御する出力制御回路14と、制御信号SMに基づく信号の入力タイミングに連動してレベルが遷移するレプリカ信号を、信号バスDBと同一の伝送特性を有するレプリカ信号バスRBに伝送させて出力するレプリカ回路30と、レプリカ信号のレベルの遷移を検知し検知結果を示すフィードバック信号SFを出力制御回路14に供給する検知回路34を備え、出力制御回路14の出力タイミングは、フィードバック信号SFにおけるレプリカ信号の遷移タイミングに応じて制御される。

(もっと読む)

画像検査システム

【課題】検査結果データを外部に出力する際のデータ出力タイミングの同期、非同期を複数の出力ごとに設定する。

【解決手段】検査制御/処理部4によって、複数の出力I/F7、それぞれのデータ出力タイミングの同期/非同期設定をし、出力制御部6によって、設定されたデータ出力タイミングで、検査結果データを外部に出力するよう複数の出力I/F7の出力制御をすることで実現する。

(もっと読む)

PCIデータ転送装置

【課題】ハードウェアに最も負荷のかかる競合状態で転送処理の限界を検証し、リトライ時間の最適値を見極め、トータル処理時間を短縮することが可能なPCIデータ転送装置を実現する。

【解決手段】PCIバスを介して複数のPCIデバイス間でデータを送受信するPCIデータ転送装置において、複数のPCIデバイスのそれぞれの転送タイミングの競合状態を発生させ、リトライ時間の最適値を求めて転送タイミングを制御する同期制御部を備える。

(もっと読む)

3相及び極性符号化されたシリアルインタフェース

高速シリアルインタフェースが提供されている。一態様において、高速シリアルインタフェースは、データ及びクロック情報を連帯的に符号化するために、3相変調を使用する。したがって、インタフェースの受信エンドにおいて回路をデスキューする必要性は、削除され、減らされたリンクスタートアップ時間(reduced link start-up time)と、改善されたリンク効率及び電力消費(improved link efficiency and power consumption)と、を結果としてもたらす。一実施形態においては、高速シリアルインタフェースは、データ及びクロック情報についての別々のコンダクタを有している従来システムよりも、より少ない信号コンダクタを使用する。別の実施形態においては、シリアルインタフェースは、データが、送信データレートのプライア知識を有している受信エンドなしに、いずれの速度で送信されることを可能にする。別の態様においては、高速シリアルインタフェースは、データ及びクロック情報を連帯的に符号化するために、極性符号化された3相変調を使用する。このことは、1以上のビットがいずれの単一のボーインターバルにおいて送信されることを可能にすることによって、シリアルインタフェースのリンクキャパシティを増大させる。  (もっと読む)

(もっと読む)

多電源制御方法及び半導体集積回路

【課題】本発明は、多電源制御方法及び半導体集積回路に関し、複数の電源からの電源電圧を用いるドメイン間で高速なデータ転送を行うことを可能とすることを目的とする。

【解決手段】複数の電源からの電源電圧を用いる複数のドメインと、ドメイン間に設けられドメイン間のデータの受け渡しを行う非同期ブリッジ部を備え、負荷に応じて少なくとも各ドメインで用いる電源電圧を動的に変更可能な構成を有する半導体集積回路の多電源制御方法において、少なくとも2つのドメインで用いる電源電圧が同じ場合、1つの電源からの電源電圧を前記2つのドメインに対して供給するように電源パスを切り換え、前記2つのドメイン間のデータの受け渡しを非同期ブリッジ部をバイパスして行うようにデータパスを切り換えるように構成する。

(もっと読む)

データストリームのクロック同期化

【課題】クロックドリフトを補償するシステムを提供すること。

【解決手段】第一のデバイスと第二のデバイスとの間でのデータフローを同期化するシステムであって、該システムは、バスシステムを介してデータを送受信可能な2つ以上のデバイスを結合するデータリンクと、情報を感知し、該バスシステムを介して該情報を転送するように構成されたキャプチャデバイスと、該データリンクによって受信されたデータを一時的に格納するリングバッファと、該キャプチャデバイスによって受信されたデータの第一の長さと異なる第二の長さのデータをコピーまたは再構築する読み出しコントローラと、該リングバッファの中または外へのデータのアンダーフローまたはオーバーフローを検出し、クロックドリフトを補償するモニタとを備える、システム。

(もっと読む)

直列データ源からのデータを並列フォーマットで読取る方法および装置

【課題】

直列データ源からのデータを並列フォーマットで読取るための方法を提供する。

【解決手段】

複数の事前定義されたデータ単位を並列バス上に送出し、その複数の事前定義されたデータ単位の各々が並列バス上で有効であるときに非直列化クロックをアサートすることによって、直列データ源からのデータが非直列化される。非直列化クロックの各アサートから所定量の時間後に、遅延したクロック・パルスが発生される。各遅延したクロック・パルスは、それに対応する終了点反復済みクロック・パルスを発生するように反復される。なお、その所定量の時間は、各終了点反復済みクロック・パルスがアサートされるとき、並列バスにおける各事前定義されたデータ単位が有効であることを保証する量の時間である。

(もっと読む)

1 - 20 / 32

[ Back to top ]