Fターム[5B077GG12]の内容

情報転送方式 (3,847) | タイミング制御 (384) | タイミング制御の手段 (230) | 非同期信号サンプリングの制御手段 (104)

Fターム[5B077GG12]の下位に属するFターム

複数のフリップフロップ (12)

位相の異なる複数のクロック (11)

遅延回路 (29)

クロック(トリガ)信号の伝送 (43)

Fターム[5B077GG12]に分類される特許

1 - 9 / 9

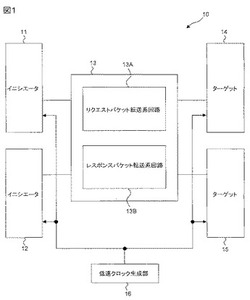

半導体装置

【課題】複数のマスタやスレーブを接続する場合のインターコネクトを低レイテンシ及び低コストで実現する。

【解決手段】データ転送に使用される第1インタフェース(201,301)と、データ転送の競合を調停するための信号の伝達に使用される第2インタフェース(202,302)とを含んで転送系回路(13)を形成する。上記第1インタフェースは、パラレル形式のデータをシリアル形式に変換するパラレル・シリアル変換回路(132,142)を含む。上記パラレル・シリアル変換回路の出力データの転送速度は、上記第2インタフェースにおける信号伝達速度に比べて高速に設定される。上記第2インタフェースは、上記複数の送信側回路からのデータ転送の競合を調停するアービタ(133,143)を含む。上記アービタによる調停後に、上記第1インタフェースを介して多量のデータを転送可能にする。

(もっと読む)

ブルーツースモジュールを使用して非ブルーツース信号を処理する方法

【課題】ブルーツースモジュールを使用して非ブルーツース信号を処理する方法を提供する。

【解決手段】第1セットのデータレートをもつ通信モジュールを有する電子装置は、その通信モジュールを使用して、第2セットのデータレートを使用するソースから受信した信号を処理できる。この装置は、第1セットのデータレートの1つ以上で信号をサンプリングすることで、リモートソースから受信した信号から、通信モジュールを使用して、第1セットのデータレートで、パケット、フレーム、等を発生する。次いで、この装置は、第1セットのデータレートで発生されたパケットから、第2セットのデータレートの信号において元々送信されたデータ又はペイロードを再構成する。従って、この装置は、信号を処理する付加的な受信器又は通信モジュールを必要とせずに、第1セットのデータレートを使用して、第2セットのデータレートの信号又は送信を処理できる。

(もっと読む)

クロックの異なるバス間におけるデータ転送

【課題】バスネットワークアーキテクチャにおける周辺機器にアクセスするレジスタの遅延を低減する。

【解決手段】低速バスから高速バスへデータを非同期に転送する方法は、上記高速バスのクロック周波数のサイクルにおける第1の所定時点でデータをラッチすることと、上記高速バスのクロック周波数の同一のサイクルにおける第2の所定時点でデータをラッチすることを備え、上記第2および第1の所定時点の間の時間周期は上記データの周期よりも短く、上記第1および第2の所定時点でラッチされたデータの値が等しい場合、上記ラッチされたデータが第3の所定時点で上記高速バスの上へ転送され、または上記第1および第2の所定時点でサンプリングされた値が異なる場合、現在存在するデータの値が上記第3の所定時点で上記高速バスへ転送される。

(もっと読む)

シンクロナイザ自動挿入方法、および挿入装置

【課題】膨大な数の非同期データ転送パスのうちで、シンクロナイザ挿入がメタステーブル問題の対策とならないパスを自動的に除外し、その他のパスにシンクロナイザを挿入する。

【解決手段】非同期データ転送パスのうちで非同期クロックが原因となるメタステーブル問題に対する対策が行われていない未対策パスを記憶し、記憶されている未対策パスにシンクロナイザを挿入してもメタステーブル問題の対策とならないパスを自動的に判定し、その他のパスにシンクロナイザを挿入する。

(もっと読む)

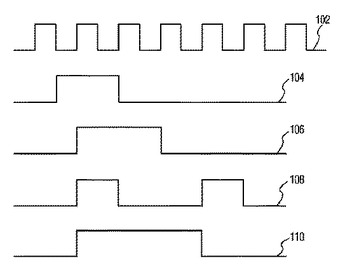

電力消費量を極めて少なくした疑似同期小型レジスタ設計及びその実施方法

電力消費量を低減させるとともに、クロックドメイン間でデータを転送する複雑性を低減させた1つ以上の疑似同期レジスタを構成及び動作させる方法及び装置を提供する。本発明の種々の実施例によれば、従来の連続的なクロックスキームの代わりに、1つ以上の疑似同期レジスタをもってデータ転送動作を実行する必要がある場合にのみ発生させるストローブ信号を用いる。ストローブ信号は、少なくとも1つの疑似同期レジスタが存在するクロックドメインを規定するクロック信号の1サイクル全体の持続時間を有するように発生させる。  (もっと読む)

(もっと読む)

データ転送回路

【課題】異なるクロックで動作するデータ転送回路を簡素化する。

【解決手段】周辺回路側の周辺クロックpclkで動作する本体レジスタ14の他、バスクロックbclkで動作し、読出データrdata と書込データwdata に共用するデータバッファ12と、周辺クロックpck で動作し、本体レジスタ14のレジスタデータregdata が更新されたときに、これをコピーして読出保持データとして出力する読出バッファ16を設け、これらの2つのバッファ12,16でクロック信号の相違を補償する。

(もっと読む)

共有資源の状態を決定する方法および装置

【課題】共有資源のアクセスにおいて、同期によるシステム遅延は最小限に抑えられ、回路設計および設計段階における正確さの証明が単純化される。

【解決手段】相互に非同期的なクロックドメイン内で作動する多数のサブシステム(802,804,806,808)により共有される資源(810)の状態を決定する方法および装置は、各サブシステムに1ビットカウンタ(814,818,822,826)を適用し、このような各ビットカウンタの値を全ての非同期クロックと同期させる。各サブシステムは各ビットカウンタ(814,818,822,826)の値を排他的ORすることにより共有資源(810)に対する可用性状態を発生する。同期によるシステム遅延は最小限に抑えられ、回路設計および設計段階における正確さの証明が単純化される。

(もっと読む)

伝送制御システム、および、伝送制御方法

【課題】共通同期信号に基づいて、各パルス計数装置から出力されるデータ信号を、同一時刻でのデータ群として1伝送周期内で高精度にかつ瞬時に一括して取得すること。複数のパルス計数装置から出力される各計数値群のサンプリングにおける時間精度を向上させること。

【解決手段】シリアル伝送信号の1伝送周期内の先頭の伝送フレームを共通同期信号とし、共通同期信号に基づいて該同一の1伝送周期内の先頭以外の残り伝送フレームを各パルス計数装置からのデータ信号に割り当てるか、該1伝送周期内の先頭の伝送フレームを全同期信号とし、全同期信号から所定のラッチタイミング調整期間後の全パルス計数器同時ラッチ信号に基づいて該同一の1伝送周期内の先頭以外の残り伝送フレームを各パルス計数装置からのデータ信号に割り当てるようにした。

(もっと読む)

スレーブ回路の動作周波数が変化するシステム

【課題】 スレーブ回路の動作周波数が変化するシステムにおいて、簡易な構成で、マスター回路がスレーブ回路とデータを交換することができるようにする技術を提供する。

【解決手段】 このシステム1は、可変の動作周波数faで動作するスレーブ回路30,40と、基準周波数f0で動作するマスター回路22と、基準クロック信号Sf0を生成してマスター回路に供給し、ローカルクロック信号Sfaを生成してスレーブ回路30,40に供給するクロック信号生成部10と、を備える。クロック信号生成部10は、マスター回路22からの指示に応じて動作周波数faを変えてローカルクロック信号Sfaを生成する。また、クロック信号生成部10は、動作周波数faの情報を含むスレーブ動作信号reqen1,acken1を生成して、マスター回路22に供給する。マスター回路22は、スレーブ動作信号に従って、スレーブ回路とデータの受け渡しを行う。

(もっと読む)

1 - 9 / 9

[ Back to top ]