Fターム[5B077GG16]の内容

情報転送方式 (3,847) | タイミング制御 (384) | タイミング制御の手段 (230) | 非同期信号サンプリングの制御手段 (104) | クロック(トリガ)信号の伝送 (43)

Fターム[5B077GG16]に分類される特許

1 - 20 / 43

オーディオインターフェイス用のゼロ遅延のスレーブモード送信

【課題】ゼロ遅延のスレーブ送信モードのための方法及び装置を提供する。

【解決手段】装置は、マスター・スレーブ構成で動作する第1及び第2の機能的ユニットを備えている。これら第1及び第2の機能的ユニットは、各々、マスター及びスレーブとして動作する。第1の機能的ユニットは、クロック及びフレーミング信号を第2の機能的ユニットへ搬送する。第2の機能的ユニットは、バッファ、及びバッファに結合された入力を有するマルチプレクサを含む。デジタルオーディオデータがバッファにプリフェッチされる。第2の機能的ユニットのコントローラは、フレーミング信号のアサーションを検出すると、マルチプレクサに与えられる選択信号の状態を変化させる。それに応答して、マルチプレクサは、送信されるべきデータの次のフレームをバッファから受け取るように結合された入力を選択する。

(もっと読む)

半導体装置及び地上波デジタル放送受信装置

【課題】CPUの負荷にかかわらず、レシーブデータレジスタ内のデータが上書きされて壊れてしまうのを回避する。

【解決手段】半導体装置はカードインタフェース(39)を含む。このカードインタフェースは、ボーレートジェネレータ(313)と、変換回路(302)と、レシーブデータレジスタ(303)とを含む。さらに上記半導体装置(3)は、レシーブデータレジスタにパラレルデータが存在しない場合には、ボーレートジェネレータからICカードへクロック信号を供給し、レシーブデータレジスタにパラレルデータが存在する場合には、ボーレートジェネレータからICカードへのクロック信号の供給を停止するためのクロック制御回路(310)を含む。上記ICカードへのクロック信号の供給を停止することで、新たなデータがICカード(7)からレシーブデータレジスタ(301)に伝達されるのを回避する。

(もっと読む)

クロック乗せ換え回路およびクロック乗せ換え方法

【課題】より安定してクロックの乗せ換えを行う。

【解決手段】2ポートRAMは、独立して書き込みと読み出しが可能であり、書き込みアドレス制御部は、2ポートRAMにおいて、入力データが書き込まれる書き込みアドレスを制御し、ブランクアドレス検出部は、書き込みアドレスにおいて、入力データが書き込まれないブランクアドレスを検出し、読み出しアドレス変換部は、2ポートRAMにおいて、ブランクアドレス以外の書き込みアドレスを、出力データが読み出される読み出しアドレスに変換する。本技術は、例えば、データ伝送システムに適用することができる。

(もっと読む)

伝送装置、伝送方法、画像形成装置、送信装置及び受信装置

【課題】併走クロックを使用する信号伝送において、併走クロックの周波数を落とすことなく、信号の長距離伝送を行うことを可能とする。

【解決手段】送信側の通信装置1と受信側の通信装置4との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置である。送信側の通信装置1は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置4送信する。受信側の通信装置は、受信したデータの少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信する。

(もっと読む)

集積回路及び集積回路の制御方法

【課題】回路若しくは装置が、仕様或いは規格に適用しない部分があったとしても、使用することに問題がない場合の対応方法のひとつを提供する。

【解決手段】集積回路が入出力回路とタイミング測定回路とを含み、前記入出力回路の第1の入力端子に入力される第1の信号と、前記入出力回路の第1の出力端子から出力される第2の信号とが前記タイミング測定回路に入力され、前記第2の信号は、前記入出力回路の第1の入出力端子における信号が前記第1の出力端子から出力されたものであり、前記タイミング測定回路において、前記第1の信号における第1の変化を検出し、前記第2の信号における前記第1の変化に対応する第2の変化を検出し、前記第1の変化を検出したときと前記第2の変化を検出したときとの間の時間間隔の計測を行うことを特徴とする。

(もっと読む)

通信システム及びそのデバイス

【課題】1本の信号線を用いて双方向のシリアル通信を行う通信システム及びそのデバイスを提供することを目的とする。

【解決手段】第1デバイス11と第2デバイス12間を1本の信号線で接続し、互いにレベルの異なる第1レベルと第2レベル、及び前記第1レベルと第2レベルの中間レベルを用いてシリアル通信を行う通信システムであって、第1デバイスは、第1レベルと中間レベルを繰り返すことで第2デバイスにクロックを送信し、第2デバイスは、受信したクロックの中間レベルの期間に第2レベルを出力するか否かで第1デバイスに情報を送信し、第1デバイスは、第2デバイスが情報を送信していない場合に、クロックの中間レベルの期間に第2レベルを出力するか否かで前記第2デバイス12に情報を送信する。

(もっと読む)

通信インタフェース装置及び通信方法

【課題】複雑な制御を要することなく2つの異なるインタフェース回路の一方のインタフェース回路での通信動作中に他方のインタフェース回路での通信動作が行われないようにする。

【解決手段】通信インタフェース装置は、第1の端子201に接続されたチップセレクト端子、第2の端子202に接続されたクロック端子、及び第3の端子203に接続されたデータ端子を有するSPIインタフェース回路101と、第1の端子201に接続されたクロック端子、及び第3の端子203に接続されたデータ端子を有するI2Cインタフェース回路102とを備え、SPIインタフェース回路101で通信する場合は、第1の端子201に固定信号を入力し、第2の端子202にクロック信号を入力し、第3の端子203にデータ信号を入力し、I2Cインタフェース回路102で通信する場合は、第1の端子201にクロック信号を入力し、第3の端子203にデータ信号を入力する。

(もっと読む)

インタフェース回路及び再構成可能集積回路装置

【課題】コンピュータとエミュレータとの間におけるデータ授受の速度と、I/F部と検査対象回路との間におけるデータ授受の速度とが異なる場合に、検査対象回路にデータを連続的に供給する。

【解決手段】インタフェース回路は、ハードウェアとソフトウェアの検証環境が実装されたコンピュータから受信したデータを保持するとともに、保持するデータをエミュレータ上に実現された検査対象回路へ出力するメモリと、メモリにデータが保持されているか否かを判定し、メモリにデータが保持されている場合には、検査対象回路にクロック信号を供給するとともに検査対象回路による前記メモリに対するメモリ読出し要求を許可し、メモリにデータが保持されていない場合には、検査対象回路へのクロック信号の供給を停止するとともに検査対象回路によるメモリに対するメモリ読出し要求を不可とするデータ供給制御回路と、を有する。

(もっと読む)

信号処理装置、及び信号伝送方法

【課題】バスシステムにおいて伝送遅延による受信不良を回避することが可能な信号処理装置を提供すること。

【解決手段】第1バスに接続された主機器から供給されるクロック、当該クロックに同期して主機器から送信されるデータを受信する主側受信部、主側受信部でデータが受信された場合に主機器の通信動作を一時停止させる主動作停止部、第2バスに接続された従機器に対し、主側受信部で受信されたクロック及びデータを送信する従側送信部、従側送信部で送信されたクロックに同期して従機器から送信されたデータを受信する従側受信部、従側受信部でデータが受信された場合に主機器の通信動作を再開させる主動作再開部、主動作再開部により通信動作が再開された主機器から供給されるクロックに同期して従側受信部で受信されたデータを主機器に送信する主側送信部を備える信号処理装置が提供される。

(もっと読む)

信号処理装置、及び信号伝送方法

【課題】バスシステムにおいて伝送遅延による受信不良を回避することが可能な信号処理装置を提供すること。

【解決手段】第1のバスに接続されたマスター機器から供給されるクロックと、当該クロックに同期して前記マスター機器から送信されるデータとを受信するマスター側受信部と、前記第1のバスとは異なる第2のバスに接続されたスレーブ機器に対し、前記マスター側受信部により受信されたクロック及びデータを送信するスレーブ側送信部と、前記スレーブ側送信部により送信されたクロックに同期して前記スレーブ機器から送信されたデータを受信してバッファに格納するスレーブ側受信部と、前記マスター側受信部によりクロック及びデータが受信されるタイミングで、当該クロックに同期して前記バッファに格納されているデータを前記マスター機器に送信するマスター側送信部と、を備える、信号処理装置が提供される。

(もっと読む)

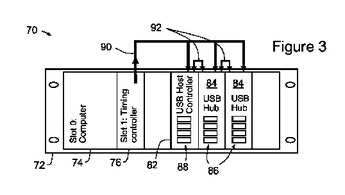

高密度、低ジッタの同期USB拡張

USBネットワークの高密度の拡張を提供する方法であって、PXI計測シャーシ内の隣接するスロットに複数のUSBハブをアタッチすること、それらのUSBハブの1つを一次USBハブとして構成すること、一次USBハブの上流ポートをUSBネットワークに接続すること、一次USBハブの第1の下流ポートを、一次USBハブ以外の複数のUSBハブの第1の隣接するUSBハブに第1のPXIローカルバスを介して通信するように構成し、第1の隣接するUSBハブは、一次USBハブに隣接すること、一次USBハブの複数の他の下流ポートを、一次USBハブの拡張を提供するように構成すること、第1の隣接するUSBハブの上流ポートを第1のPXIローカルバスに接続し、第1のPXIローカルバスは、一次USBハブの方向にあること、第1の隣接するUSBハブの第1の下流ポートを、一次USBハブ以外の複数のUSBハブの第2の隣接するUSBハブに第2のPXIローカルバスを介して通信するように構成し、第2の隣接するUSBハブは、第1の隣接するUSBハブに隣接すること、第1の隣接するUSBハブの複数の他の下流ポートを、第1の隣接するUSBハブの拡張を提供するように構成すること、およびそれらのUSBハブの他の任意のUSBハブ、および第1の隣接するUSBハブを同様に構成することを備える方法。  (もっと読む)

(もっと読む)

メモリデバイスおよびメモリデバイス制御装置

【課題】従来のインタフェースの機器との接続互換性を保ちつつ、データ転送速度を向上できるメモリデバイスおよびメモリデバイス制御装置を提供する。

【解決手段】メモリデバイス103とホスト装置101の間に介在するメモリデバイス制御装置102は、クロック信号に同期してメモリデバイスとの間でデータを転送するデータ転送手段123を備える。データ転送手段123は、クロック信号の立ち上がりエッジ及び立下りエッジの一方に同期してデータを転送するシングルエッジ同期モード、または、立ち上がりエッジと立下りエッジとの双方に同期してデータを転送するダブルエッジ同期モードに対応する。メモリデバイス103がバスマスタとして動作してデータ転送を行う際、データ転送手段123はメモリデバイスに対してダブルエッジ同期モードでデータ転送を行う。

(もっと読む)

シリアル通信装置

【課題】制御信号に適したシリアル伝送によって配線数を削減することが可能なシリアル通信装置の提供する。

【解決手段】複数の送信制御信号を送信シリアル信号に変換して外部に出力するP/S変換器と、外部から入力された受信シリアル信号を外部から入力された受信転送クロックを用いて複数の受信制御信号に変換するS/P変換器と、送信シリアル信号に同期した送信転送クロックを外部に出力するクロック出力回路と、受信シリアル信号に同期した受信転送クロックをS/P変換器に出力するクロック入力回路とを具備する。

(もっと読む)

高速データレートインタフェース装置及び方法

【課題】デジタル制御データとデジタルプレゼンテーションデータの事前に選択されたセットを通信するための通信プロトコルを形成するために、共にリンクされるパケット構造を使用して、通信経路上、ホストとクライアントの間でデジタルデータを転送するためのデータインタフェースを提供する。

【解決手段】信号プロトコルは、通信プロトコルを形成するパケットを生成、送信、及び受信し、デジタルデータを1つ又は複数のタイプのデータパケットに形成するように構成され、少なくとも1台が該ホストデバイスに常駐し、該通信経路を通して該クライアントに結合される、リンクコントローラによって使用される。インタフェースは、短距離「シリアル」タイプデータリンクでの、費用効果が高い、低電力の、双方向高速データ転送機構となる。

(もっと読む)

印刷装置、及びデータ通信方法

【課題】ノイズに対して耐性を強くして、データの変更を未然に防止する。

【解決手段】印刷処理を実行するエンジン部と、エンジン部の駆動を制御するメカコントローラと、メカコントローラと通信を行なうメインコントローラとを備える印刷装置であって、メカコントローラとメインコントローラとは、クロック線を流れるクロック信号の波形変化を用いて同期を取りつつ通信を行い、メインコントローラは、通信開始前に、クロック信号の波形変化の周期を示す周期データをメカコントローラに送信し、メカコントローラは、通信時に、クロック信号の波形変化を監視し、波形変化が送信された周期データにより指定された周期と異なる場合は、この波形変化を無効とみなし、同波形変化による通信を行なわない。

(もっと読む)

単線式通信プロトコルにおけるマスターデバイスにより受信されるデータの検出

【課題】本発明は、単線式の接続部を介した2つのデバイス間のデータ送信に関する方法及びシステムを提供し、単線式プロトコルにおける通信速度の増加を可能にする。

【解決手段】第2デバイスから単線式の接続部を介して第1デバイスに送信されるデータのバイナリ状態を、前記接続部を介して前記第2デバイスに2状態の信号を送信することが可能な第1デバイスによって決定する方法であって、前記バイナリ状態は、前記2状態の信号の立ち上がりエッジの傾斜に応じて決定される。

(もっと読む)

マルチチップシステムおよび半導体装置

【課題】転送遅延が小さいマルチチップシステムおよび該マルチチップシステムを構成する半導体装置を提供する。

【解決手段】宛先ID判定部3は受信データDAT_1のヘッダ部に含まれる宛先IDが受信された時点で直ちにデータの宛先を判定し、自分宛てでなければ、送信制御部4は受信データバッファ1による受信データDAT_1の受信と同時進行でその受信データDAT_1を転送する。

(もっと読む)

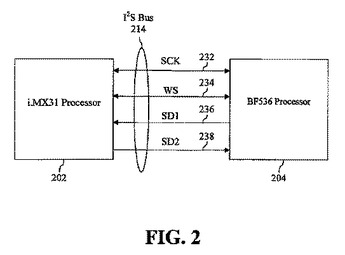

プロセッサ間通信のためのシステムおよび方法

マルチプロセッサシステム内の信頼性の高いプロセッサ間通信のための方法について記載される。一側面に従って、特殊構成シリアルバスが、第1のプロセッサと第2のプロセッサとの間の汎用データリンクとして使用される。シリアルバスは、IC間サウンド(I2S)バスであってもよい。別の側面に従って、第2のプロセッサ上に常駐するネットワークインターフェースは、I2Sバス上に構築されるデータリンクを介して、第1のプロセッサに利用可能となる。これによって、第2のプロセッサは、プロキシとして使用され、遠隔構成およびネットワークアドレストラバーサルをサポート可能となる。  (もっと読む)

(もっと読む)

携帯電子機器

【課題】ホスト側パラレルバスインターフェースとデバイス側シリアルバスインターフェースの間に論理回路部を設け、両者間に介在されるコントローラを省略して同期式シリアルバス接続を実現すること。

【解決手段】ホスト側回路が複数のデータ端子及びアドレス端子、リード(RD)端子、ライト(WR)端子、チップセレクト(CS)端子を有し、デバイス側回路がデータ(D0)端子、クロック(CLK)端子、チップセレクト(CS)端子を有する。ORゲートによる第1の論理回路部502は、RD端子及びWR端子の信号により出力状態が変化し、ANDゲートによる第2の論理回路部503は第1の論理回路部502及びCS端子の各出力信号により出力状態が変化する。第2の論理回路部503の出力信号をデバイスへのクロック信号として提供し、当該クロック信号に基づき、D0端子のみを用いてパラレル/シリアル変換されたデータ信号をデバイスに出力する。

(もっと読む)

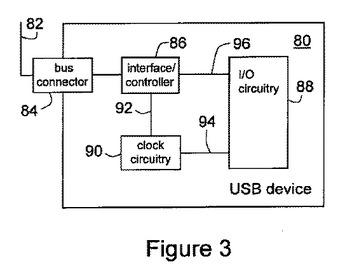

USBベースの同期およびタイミングシステム

USBマイクロコントローラ、USBトラフィックを監視する回路、および分散クロック周波数および位相に関する情報を含む周期的データ構造(クロック搬送波信号など)をUSBデータストリームからデコードし、デコードされた搬送波信号を出力する回路、を有するUSBデバイスと、デコードされた搬送波信号を受信し、ある所定のデータパケット(SOFパケットなど)の受信時にソフトウェア割り込みを発生させ、さらにソフトウェア割り込みをUSBマイクロコントローラに送出する回路と、を備える同期装置であって、USBマイクロコントローラは、同期化参照信号として使用されるように適合された出力信号を生成することによってソフトウェア割り込みに応答する(そこに備わる割り込みサービスルーチンなどによる)ように構成されている、同期装置。  (もっと読む)

(もっと読む)

1 - 20 / 43

[ Back to top ]