Fターム[5B079AA06]の内容

Fターム[5B079AA06]に分類される特許

1 - 20 / 82

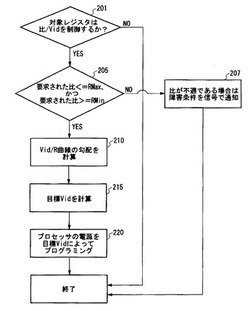

プロセッサ動作電圧の自動動的制御

【課題】プロセッサシステムは、動作電圧とコア/バス周波数との組み合わせによってはプロセッサの損傷あるいはプロセッサの動作の信頼性低下を引き起こすことを防止する。

【解決手段】1つのプロセッサの動作電圧を動的に調整する一方で、前記プロセッサが前記プロセッサの前記コア/バス周波数比との関係において有害である1つの動作電圧状態に1人のユーザによって置かれることを防止するための手法。より具体的には、プロセッサの動作電圧をプロセッサのバスおよび/あるいはコアクロック周波数の1つの関数として制御するための1つの手法に関する。

(もっと読む)

コンピュータシステムおよびコンピュータシステムの動作方法

【課題】 コンピュータシステムの冷却機構の設計を簡易にする。

【解決手段】 コンピュータシステムは、順次発生する複数のタスクをそれぞれ処理する複数のプロセッサと、タスクの内容を示すタスク情報を順に受け、各タスクを処理するためにプロセッサに掛かる負荷を求める算出部と、連続する所定数のタスクを含むタスクグループ毎に、負荷が相対的に大きいタスクをプロセッサの1つである第1プロセッサに割り当て、負荷が相対的に小さいタスクを残りのプロセッサに割り当てる割り当て部とを有している。

(もっと読む)

ディジタル・パワー・スロットルを備えたマイクロプロセッサ

【課題】 プロセッサ内の電力消費を調整するためのディジタルベースのメカニズムを提供する。

【解決手段】 本発明は、プロセッサ内の電力消費を調整するためのディジタルベースのメカニズムを提供する。このプロセッサは、1つまたは複数の機能ユニットと、プロセッサの機能ユニットの活動状態を監視して、プロセッサの電力消費を推定するディジタル・スロットルとを含む。このディジタル・スロットルの一実施形態は、1つまたは複数のゲート・ユニットと、1つの監視回路(320)と、1つのスロットル回路(330)とを含む。各ゲート・ユニットは、プロセッサの機能ユニットへの電力送付を制御し、その関連機能ユニットの活動状態を示す信号を出力する。監視回路は、信号から推定電力消費レベルを決定し、その推定電力消費としきい電力レベルを比較する。推定電力消費レベルがしきい電力レベルを超える場合、スロットル回路はプロセッサ内の命令フローを調整する。

(もっと読む)

マルチプロセッサ装置

【課題】OS間によるロック取得を行なう必要がなく、処理効率を向上させることが可能なマルチプロセッサ装置を提供すること。

【解決手段】タイマ#0〜#3(22〜25)には、電源電圧の変更動作の禁止期間が設定される。タイマ#0〜#3(22〜25)のいずれかが禁止期間を経過したときに、OS#A(14)またはOS#B(15)が、そのタイマに対応するCPUコアの動作周波数の変更の要否を判定する。そして、動作周波数の変更が必要と判定されたときに、CPUコア#0〜#3(10〜13)に供給する電源電圧の変更の要否を判定する。電源電圧の変更が必要と判定されたときに、電源電圧変更部20が、CPUコア#0〜#3(10〜13)に供給する電源電圧を変更する。したがって、OS間によるロック取得を行なう必要がなく、処理効率を向上させることが可能となる。

(もっと読む)

複数の回路における性能パラメータの整合

【課題】複数の回路の性能パラメータを整合するためのシステム及び方法を提供する。

【解決手段】複数のドメインにおいて性能パラメータを整合するシステム及び方法が開示される。方法は、第1ドメイン及び第2ドメインを含む電子回路の状態を切り換えるための要求を受け取り、第1ドメインに作用する第1回路の第1パラメータを、その要求に基づいて第1の変更パラメータへと変更させ、そして第2ドメインに作用する第2回路の第2パラメータを、その要求に基づいて第2の変更パラメータへと変更させることを含む。あるケースでは、パラメータは、クロック周波数を含む。他のケースでは、パラメータは、電圧を含む。ある実施形態では、システムは、ロジック回路及び/又はシステムオンチップ(SoC)として具現化される。

(もっと読む)

集積回路、クロックゲート回路、および方法

【課題】本発明は、集積回路に渡ってクロック信号を分配する時に消費される、電力の量を減少するための技術に関する。

【解決手段】集積回路2は、動作クロック周波数を有する動作クロック信号に応じて作動するように配設される、機能回路4、6を備える。電力を節約するために、クロック信号は、動作クロック周波数よりも低い分配クロック周波数で、集積回路2に渡って分配される。クロック変換器10は、機能回路4、6の動作を制御するために、分配クロック信号を動作クロック信号に変換するように提供される。

(もっと読む)

プロセッサ、半導体集積回路装置及びプロセッサシステム

【課題】複数の周辺回路を備えたプロセッサ、半導体集積回路装置及びプロセッサシステムの処理能力を低下させることなく、消費電流を低減するプロセッサ、半導体集積回路装置及びプロセッサシステムを提供する。

【解決手段】プロセッサコア2と、プロセッサコア2からの命令に応答して所定の処理を実行する周辺回路3−1,3−2とを備えるプロセッサ7において、各周辺回路3−1,3−2は、プロセッサコア2からの命令に基づいて第1の全処理サイクル数を算出する算出部100と、比較部300からの分周比に基づいて、クロック信号を分周して出力するクロック発生部400と、第1の全処理サイクル数を、他の周辺回路の算出部100によって算出される上記他の周辺回路の第2の全処理サイクル数と比較して、当該比較結果に基づいて、当該周辺回路の処理終了時刻が上記他の周辺回路の処理終了時刻に近づくように上記分周比を発生する比較部300とを備えて構成される。

(もっと読む)

マイクロプロセッサ、電子制御ユニット、電源制御方法

【課題】低消費電力と低コストの両立を図りながら、マルチプロセッサの消費電力を低減できるマイクロプロセッサ、電子制御ユニット及び電源制御方法を提供すること。

【解決手段】 N個のプロセッサ19と、複数のグループに分けられたN個のプロセッサに、グループ毎に共通の電源電圧を供給する電源回路17と、グループ毎に共通のクロック周波数のクロックを供給する、電源回路と対のクロック生成回路18と、プロセッサの負荷に基づき、グループ毎に電源電圧とクロック周波数を制御する制御回路14と、を有し、電源回路17の数の合計がN個より小さいM個であり、電源回路17の数の合計又はクロック生成回路18の数の合計が、N個より小さいM個である、ことを特徴とするマイクロプロセッサ100又はチップセット100を提供する。

(もっと読む)

プロセッサスリープ及びウェイクイベントに対するシステムのハードウェア自動性能状態移行

省電力マルチCPUシステム、画像形成装置

【課題】誤って全てのCPUの内部クロックを停止させることなく、一部のCPUの内部クロックのみを停止させて、消費電力を適切に抑制することができる、堅牢性のある省電力マルチCPUシステム及び画像形成装置を提供することを目的とする。

【解決手段】クロック信号を受け付けて動作する複数のCPU10,11と、各CPUにより制御され、当該CPU以外の他のCPUに対するクロック信号の供給及び当該供給の遮断を行う信号供給制御部12〜15と、各CPUに対するクロック信号の供給を監視して、各CPUに対するクロック信号の供給の全てが遮断されているか否かを判断する監視部16と、監視部16により、各CPUに対するクロック信号の供給の全てが遮断されていると判断されたときには、信号供給制御部12〜15により、各CPUのうちいずれかのCPUに対するクロック信号の供給を再開する遮断解除制御部17と、を備える。

(もっと読む)

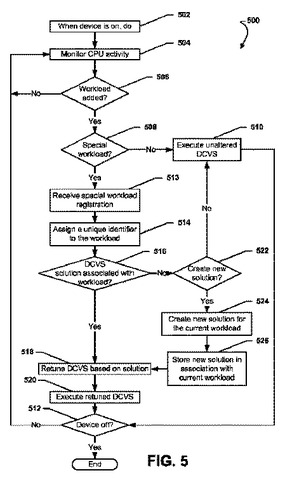

プロセッサを動的に制御するシステムおよび方法

中央処理装置(CPU)内で動的なクロックおよび電圧スケーリング(DCVS)アルゴリズムを実行する方法が開示されており、CPUのアクティビティを監視するステップと、ワークロードがCPUのアクティビティに追加されたとき、ワークロードが特殊なワークロードに指定されるかどうかを決定するステップとを含み得る。  (もっと読む)

(もっと読む)

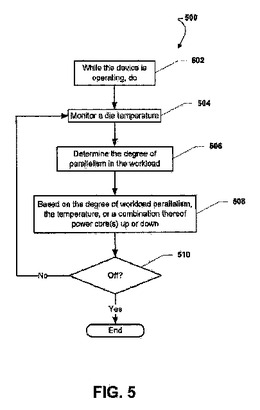

温度に基づいてマルチコア中央処理装置内の複数のコアを動的に制御するためのシステムおよび方法

マルチコア中央処理装置(CPU)内の電力を制御する方法が開示される。本方法は、ダイ温度を監視するステップと、CPUの作業負荷内の並列性の度合いを判定するステップと、並列性の度合い、ダイ温度、またはそれらの組合せに基づいて、前記CPUの1つまたは複数のコアの電源を上げるまたは落とすステップとを含みうる。  (もっと読む)

(もっと読む)

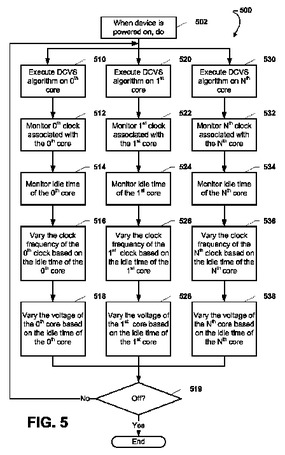

マルチコア中央処理装置内の複数のコアクロックを非同期で、独立に制御するためのシステムおよび方法

マルチコア中央処理装置内の複数のコアクロックを制御する方法が、開示され、さらに第0のコア上で第0のDCVS(動的クロックおよび電圧スケーリング)アルゴリズムを実行すること、および第1のコア上で第1のDCVSアルゴリズムを実行することを含むことが可能である。第0のDCVSアルゴリズムは、第0のコアに関連する第0のクロック周波数を独立に制御するように動作できることが可能であり、さらに第1のDCVSアルゴリズムは、第1のコアに関連する第1のクロック周波数を独立に制御するように動作できることが可能である。  (もっと読む)

(もっと読む)

ワークロードの要求に基づいて動的なクロックおよび電圧切替えアルゴリズムを調整するシステムおよび方法

動的なクロックおよび電圧切替えアルゴリズムを調整する方法が開示されており、デフォルトの応答度を設定するステップと、ワークロードが追加された後、ワークロードが登録しているかどうかを決定するステップと、ワークロードが登録している場合、一意の識別子をワークロードに割り当てるステップと、ワークロードから必要な応答度を受信するステップとを含み得る。  (もっと読む)

(もっと読む)

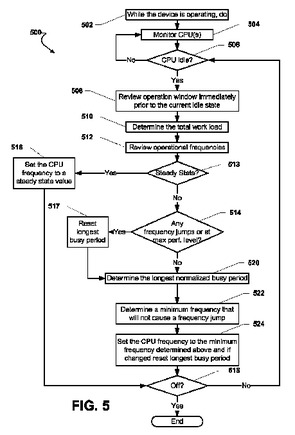

周波数変動を低減させて中央処理装置電力を制御するためのシステムおよび方法

中央処理装置内の電力を動的に制御する方法が開示され、アイドル状態に入ること、アイドル状態の直前のビジーサイクルを点検すること、および前のビジーサイクルに基づいて、次のビジーサイクルに関するCPU周波数を算出することを含むことが可能である。  (もっと読む)

(もっと読む)

保証された定常状態期限で中央処理装置電力を制御するためのシステムおよび方法

中央処理装置を動的に制御する方法が、開示される。この方法は、CPUがいつ定常状態に入るかを判定すること、CPUが定常状態に入ると、CPUに関する最適な周波数を計算すること、定常状態CPU利用率を保証すること、および定常状態CPU利用期限を保証することを含むことが可能である。 (もっと読む)

仮想CPUベースの、周波数、及び電圧制御

【課題】仮想環境の各々の仮想プロセッサのために実行される周波数、及び電圧制御を統合して、性能を犠牲にせずにパワーセービングを達成する。

【解決手段】各々の仮想プロセッサによって実行されるワークロードの特徴は、動的にプロファイルが作られ、かつ制御アルゴリズム140a〜140nは、前記プロファイルが作られた特徴の関数として、その仮想プロセッサのための制御ファクタを決定する。プロファイルが作られた特徴は、実行されている前記ワークロードに関連づけられた、仮想化イベントを含んでもよく、加えて、特定の制御アルゴリズム、及びプロファイリング技術は、どの仮想プロセッサが現在動作しているかに基づいて選択されてもよい。

(もっと読む)

高効率且つリアルタイムでプラットフォーム電力管理アーキテクチャを実行する装置

【解決手段】 一部の実施形態によると、本発明は、コンピューティングプラットフォーム用の高効率且つリアルタイムのプラットフォーム電力管理アーキテクチャを提供する。集積化された電圧レギュレータを用いて、一部の実施形態によると、直接電力管理インターフェース(DPMI)も利用して、より直接的な電力管理アーキテクチャを提供するとしてよい。集積化された電圧レギュレータ、例えば、シリコン内電圧レギュレータ(ISVR)は、より高速でより高い応答性で電力状態を遷移させるべく利用され得る。 (もっと読む)

プローブアクティビティレベルの追跡による性能状態の制御

【解決手段】

処理ノードは、その内部キャシング又はメモリシステムに関連するプローブアクティビティレベルを追跡する。プローブアクティビティレベルがスレッショルドプローブアクティビティレベルを超えると、処理ノードの性能状態がその当座の性能状態よりも高くされて、高められた性能能力をプローブ要求に応答して提供する。プローブアクティビティレベルがスレッショルドプローブアクティビティレベルを超えたことに応答してより高い性能状態にエンターした後に、処理ノードは、プローブアクティビティの低下に応答してより低い性能状態に戻る。多重スレッショルドプローブアクティビティレベル及び関連する性能状態があってよい。

(もっと読む)

マルチコアプロセッサ用の電力チャネルモニタ

マルチコアプロセッサ内での電力チャネル監視の技法を、全般的に説明する。電力管理システムを、マルチコアプロセッサ内の個々のコアに供給する電力チャネルを監視するように構成することができる。電力チャネルモニタは、各コアの電力消費の直接測定値を提供することができる。個々のコアの電力消費は、どのコアの使用が多いか、または少ないかを示すことができる。使用判定を、測定されるコアへまたはこれからのデータメッセージの送信を全く伴わずに行うことができる。各プロセッサコアによってサービスされる判定された使用負荷を使用して、そのコアに供給される電力および/またはクロック信号を調整することができる。  (もっと読む)

(もっと読む)

1 - 20 / 82

[ Back to top ]