Fターム[5B079BB10]の内容

Fターム[5B079BB10]に分類される特許

1 - 20 / 64

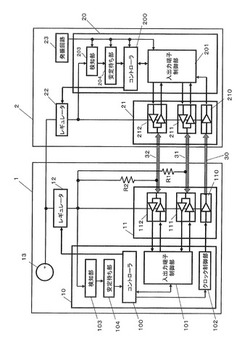

ホスト装置用インタフェース装置、スレーブ装置用インタフェース装置、ホスト装置、スレーブ装置、通信システム、及びインタフェース電圧切り替え方法

【課題】少ない信号線数でインタフェース電圧を切り替えることが可能な通信システムとする。

【解決手段】複数のインタフェース電圧から動作電圧を選択することができる通信システムにおいて、通信システムの動作中に、安定してインタフェース電圧の切り替え処理を行う。ホスト装置(1)およびスレーブ装置(2)は、インタフェース電圧の切り替えを行う場合に、バスの信号レベルを安定的に保って切り替えを行うように構成される。

(もっと読む)

記憶装置、通信システムおよび記憶装置の制御方法

【課題】リセット信号線を接続するための端子や配線等の回路構成がなく、簡易な構成をもつ記憶装置、カートリッジ、通信システムおよび記憶装置の制御方法を提供すること。

【解決手段】記憶装置20は、クロック信号SCKおよびデータ信号SDAが入力され、リセットにより初期化された後にクロック信号SCKに同期したデータ通信を開始するよう構成されている。この記憶装置20は、クロック信号SCKがハイのレベルを維持する期間において、データ信号SDAに複数回のレベル変化を生じたか否かを判定し、複数回のレベル変化を生じていた場合に、記憶装置20のリセットを実行するリセット処理ユニット27を備えている。

(もっと読む)

半導体集積回路、その制御方法、及び電子機器

【課題】動作周波数の変更を行う場合に当該半導体集積回路に供給されるべき供給電圧を低く抑えることのできる半導体集積回路を提供する。

【解決手段】電源回路13から供給される供給電圧により動作し、動作周波数を初期周波数から目標周波数に変更する半導体集積回路10であって、当該動作周波数を変更する際に、供給電圧を目標周波数に応じて決定される目標電圧に変更するよう電源回路13に要求し、初期周波数から前記目標周波数への変更を、複数回に分けて段階的に行う半導体集積回路10である。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

消費電力及びノイズを低減可能な制御装置

【課題】入力されたクロック信号に同期してデータ処理を実行するデータ処理回路に対して、高周波クロック信号の入力を制御することにより出力時以外の消費電力及びノイズ発生の増大を抑制する制御装置を提供する。

【解決手段】制御装置は、データ処理用のクロック信号を出力する第1のクロック出力手段1210と、データ処理用のクロック信号よりも周波数の低い待機用のクロック信号を出力する第2のクロック出力手段1220と、データ処理用のクロック信号と待機用のクロック信号とを切替て、データ処理回路へ出力する切替部1230とを備える。制御装置の制御部1110、1250または1290は、データ処理回路でデータ処理を実行する期間中にデータ処理用のクロック信号を出力するように切替部1230を制御すると共に、データ処理回路がデータ処理をしていない期間中に待機用のクロック信号を出力するように切替部1230を制御する。

(もっと読む)

省電力マルチCPUシステム、画像形成装置

【課題】誤って全てのCPUの内部クロックを停止させることなく、一部のCPUの内部クロックのみを停止させて、消費電力を適切に抑制することができる、堅牢性のある省電力マルチCPUシステム及び画像形成装置を提供することを目的とする。

【解決手段】クロック信号を受け付けて動作する複数のCPU10,11と、各CPUにより制御され、当該CPU以外の他のCPUに対するクロック信号の供給及び当該供給の遮断を行う信号供給制御部12〜15と、各CPUに対するクロック信号の供給を監視して、各CPUに対するクロック信号の供給の全てが遮断されているか否かを判断する監視部16と、監視部16により、各CPUに対するクロック信号の供給の全てが遮断されていると判断されたときには、信号供給制御部12〜15により、各CPUのうちいずれかのCPUに対するクロック信号の供給を再開する遮断解除制御部17と、を備える。

(もっと読む)

仮想CPUベースの、周波数、及び電圧制御

【課題】仮想環境の各々の仮想プロセッサのために実行される周波数、及び電圧制御を統合して、性能を犠牲にせずにパワーセービングを達成する。

【解決手段】各々の仮想プロセッサによって実行されるワークロードの特徴は、動的にプロファイルが作られ、かつ制御アルゴリズム140a〜140nは、前記プロファイルが作られた特徴の関数として、その仮想プロセッサのための制御ファクタを決定する。プロファイルが作られた特徴は、実行されている前記ワークロードに関連づけられた、仮想化イベントを含んでもよく、加えて、特定の制御アルゴリズム、及びプロファイリング技術は、どの仮想プロセッサが現在動作しているかに基づいて選択されてもよい。

(もっと読む)

集積回路装置、電子機器及び調整電圧の制御方法

【課題】 温度条件が変化しても停止電圧との適切な電位差を保ち低消費電力を実現する集積回路装置等を提供する。

【解決手段】 集積回路装置1であって、第1の振幅と比べて、入力された発振信号400の振幅の方が大きい場合に、第1の矩形波信号408を出力する第1の矩形波信号生成部11と、前記第1の振幅よりも大きな第2の振幅と比べて、前記発振信号400の振幅の方が大きい場合に、第2の矩形波信号402を出力する第2の矩形波信号生成部12を含む。

(もっと読む)

情報処理装置、情報処理装置の制御方法及びプログラム

【課題】 情報処理装置において、第1の演算手段の起動中で第2の演算手段の起動処理が完了している間に、第2の演算手段に対してクロックの供給を停止すること。

【解決手段】 DSP203は、DSP203の起動処理が完了したら、DSP203を割り込み待ち状態へ移行させる(S204)。

DSP203は、DSP203が割り込み待ち状態へ移行したら、クロック制御部310を用いて、DSP203に対するクロックの供給を停止させる(S205)。

DSP203は、CPU201から割り込み信号を受信したら、クロック制御部310を用いて、DSP203に対するクロックの供給を再開させる(S207)。

DSP203は、DSP203を割り込み待ち状態から復帰させる(S209)。

(もっと読む)

クロック分周回路

【課題】入力クロック信号の立ち下がりの際に、出力クロック信号の立ち上げを可能とし、入力クロック信号を任意の有理数で表わされる分周比にて分周した出力クロック信号を得ること。

【解決手段】本発明は、演算器11、演算器12a、比較器108とを少なくとも備える。分子設定値112を分母設定値111で除した値である分周比で入力クロック信号109を分周する。演算器11は、入力クロック信号109に同期して入力信号の値を記録する。そして、生成した演算器出力値120を入力クロック信号109に応じて出力する。演算器12aは、演算器出力値120を出力する。比較器108は、演算器出力値120が分子設定値112と比較してハイ信号またはロウ信号を出力クロック信号121として出力する。演算器出力値120は帰還して演算器11に入力される。

(もっと読む)

プロセッサ制御システム、方法、及びプログラム

【課題】本発明は、消費電力を低減しながらもプロセッサの処理能力の低下を防止可能なプロセッサ制御システムを提供する。

【解決手段】管理装置の管理側制御手段の一部11は、温度計測手段にて計測された温度が閾値をこえたら、プロセッサの動作周波数を下げる第1制御機能と、第1制御機能にて前記動作周波数を下げた状態において前記プロセッサの処理性能が低下したら、前記予備用プロセッサを含む前記予備セルを動的に追加する第2制御機能とを含む。

(もっと読む)

マイクロコンピュータ

【課題】リセット期間中の消費電力を削減する。

【解決手段】マイクロコンピュータは、プロセッサと、第1発振周波数の第1発振信号を出力する第1発振回路と、第1発振周波数より低い第2発振周波数の第2発振信号を出力する第2発振回路と、通常状態または初期化状態の何れか一方を指示するリセット信号に基づいて、通常状態の場合は第1発振信号をプロセッサの動作用の動作クロックとして出力し、初期化状態の場合は第2発振信号を初期化処理用の初期化クロックとして出力するクロック選択回路と、を備える。

(もっと読む)

信号処理装置および信号処理方法

【課題】 相互に異なる周期のクロック信号が与えられ、かつ相互に非同期で所定の処理を行う複数の処理部のリセットを、簡単な構成で、確実に行うことができる信号処理装置および信号処理方法を提供する。

【解決手段】 モジュール回路部14は、モジュールA,B,Cのうちのいずれかに対するリセット指令が与えられると、指令されたモジュールを指定する信号を含み、かつCPUCLKの1周期分の長さを有する1shotリセット信号を生成する。同期リセット生成回路部15は、1shotリセット信号が与えられ、この1shotリセット信号の長さを指令されたモジュールに対応する長さに引き延ばした伸長リセット信号を生成し、生成した伸長リセット信号を指令されたモジュールのクロックに同期させて同期リセット信号を生成し、指定されたモジュールでは、同期リセット信号が与えられた状態で、クロック信号が立上がりまたは立下ると、リセットされる。

(もっと読む)

情報処理装置

【課題】情報処理装置の使用状況にともなって半導体素子の温度が上昇する可能性が発生しても情報処理装置の動作を停止させない、あるいは情報処理装置の動作停止までの時間を遅らせる。

【解決手段】マイクロプロセッサ21を有する情報処理回路20と、情報処理回路20を冷却する冷却ファン33と、情報処理回路20の温度を検出する温度センサ31(1)〜31(7)と、温度センサ31(1)〜31(7)の検出温度に基づき冷却ファン33の回転数を制御するファン制御部32と、冷却ファン33による空気の流れの速度を検出する風速センサ35と、冷却ファン33の回転数と風速センサ35の検出速度とに基づき空気の流れの異常を検出する異常検出部34とを備え、異常検出部34が異常を検出した場合に情報処理回路20の消費電力を抑制する。

(もっと読む)

電源制御装置及びその電源制御装置を有するシステムLSI

【課題】電源電圧変動時に誤動作を発生することなく電源電圧変動シーケンスを実行できる電源制御装置を提供する。

【解決手段】第1,第2のCPUがそれぞれ属する第1,第2の電源ドメインの電源電圧を制御する電源制御装置において,第1,第2の電源ドメイン(9,8)に第1,第2の電源電圧(p2,p1)をそれぞれ供給する電源装置(3)と,第1,第2のクロック(s7,s6)を生成し第1,第2のCPUにそれぞれ供給するクロック生成部(16)とに接続された電源クロック制御部(4)を有する。電源クロック制御部は,第1のCPUからの第2の電源ドメインの電源電圧変更要求に応答して,電源装置に第2の電源電圧を変更させ,第2のCPUからの第2のクロック周波数変更要求に応答して,クロック生成部に第2のクロックの周波数を変更させ,さらに,第2の電源ドメインの電源電圧変更要求に応答して,第2の電源電圧が要求電圧に達するまでの期間,第2のクロック周波数変更要求を受け付けない。

(もっと読む)

マルチダイマイクロプロセッサにおける周波数及び性能を最適化する方法、装置、及びシステム

【課題】 マルチコアプロセッサ化が進んではいるが、各コアは、アイドル又はアクティブステータスに関して、他のダイのステータスを容易に確認することができない。

【解決手段】 マルチダイマイクロプロセッサにおける複数のコア間でコアステータスを伝送するインターフェイスを使用する提案を記載する。これは、各コアのステータスを使用して性能及び周波数の最適設定を可能にして熱管理を容易にする。

(もっと読む)

プログラム可能な遅延を有するシーケンスが独立のオーバーラップしないディジタル信号発生器

【課題】オーバーラップしないクロック発生回路を提供する。

【解決手段】複数の遅延された基準クロック信号を生成するプログラム可能な遅延基準クロック信号回路と、プログラム可能な遅延基準クロック信号回路と動作可能に接続され、オーバーラップしないクロック信号を発生する複数の遅延クロック信号発生器とを含む。各遅延クロック信号発生器は、クロック信号の立ち上がりの遅延を制御し第1の信号を出力するラッチまたはフリップフロップと、遅延されたクロック信号の立ち下がりエッジの遅延を制御し第2の信号を出力するもう一つのラッチまたはフリップフロップと、第1および第2の信号からクロック信号を発生する論理回路とを含む。ラッチまたはフリップフロップは、複数の遅延された基準クロック信号の1つに応答してクロック信号の立ち上がりエッジの遅延を独立して制御する。

(もっと読む)

パケット受信装置

【課題】休止状態にあるホストプロセッサを頻繁に起動しないことにより、休止状態から稼働状態に遷移する際の時間的オーバヘッドを軽減するとともに、オーバヘッド時間に浪費する電力を抑制し、通信性能の向上を図ること。

【解決手段】通信インタフェース回路101は、受信信号からパケットデータを抽出する。通信インタフェース制御回路102は、割り込み信号を生成して出力する。ネットワークプロセッサ103は、パケットデータを解析して、解析結果に基づいて、パケットデータをホストプロセッサ108に転送するか否かを判定する。割り込み制御回路105は、ネットワークプロセッサ103から割り込み信号を受け取った際に、ホストプロセッサ108を起動させる。ホストプロセッサ108は、電源及びクロックの供給を受けて起動し、割り込み信号を受けてパケットデータの受信処理を実行する。

(もっと読む)

半導体集積回路

【課題】回路の誤動作を防止しつつ、所望のデータ処理をすることが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、電源電圧がしきい値以下である場合にクロック停止信号を出力し、電源電圧がしきい値より大きい場合にクロック作動信号を出力する電源電圧監視回路2と、クロック停止信号に応じて、外部から入力されたクロック信号の出力を停止し、クロック作動信号に応じて、クロック信号を出力するクロックゲーティング回路3と、電源電圧が供給され、クロックゲーティング回路3から出力されたクロック信号に同期して動作するプロセッサ4と、電源電圧監視回路2の出力信号に応じて、外部から入力されたデータを一時的に格納するデータバッファ5と、を備える。

(もっと読む)

計算装置のための最大電力使用設定値

【課題】計算装置のための最大電力使用設定値を決定する手段を提供する。

【解決手段】計算装置のための最大電力使用設定値は、計算装置による電力使用を減らすためにどのくらいの頻度で計算装置のプロセッサの周波数を下げる必要がありそうかに対応するユーザ指定の設定値と、計算装置が動作させられた前の期間におけるプロセッサの平均周波数と、前の期間におけるプロセッサの最低周波数と、前の期間に計算装置が使用した最大電力と、プロセッサの公称周波数とのうちの1つ以上に基づく。計算装置が最大電力使用設定値より多い電力を使用し始める時、計算装置により使用される電力は、例えば、プロセッサが動作する周波数を下げることにより、該設定値を超えないように減らされる。

(もっと読む)

1 - 20 / 64

[ Back to top ]