Fターム[5B079CC01]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 調整手段 (364)

Fターム[5B079CC01]の下位に属するFターム

遅延回路を用いるもの (210)

静電容量の調整 (10)

線路長の調整 (7)

シフトレジスタ (28)

遅延量を計測するもの (50)

Fターム[5B079CC01]に分類される特許

1 - 20 / 59

クロック生成回路、及びクロック生成方法

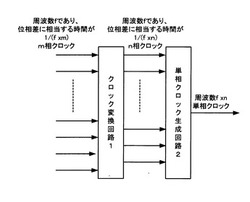

【課題】一種類の多相クロックより多くの周波数の種類の単相クロックを得ることができるクロック生成回路及びその方法を提供する。

【解決手段】少なくともn個の位相補間器を有し、周波数がfで位相差が1/(f×m)づつ異なるm相クロックを、周波数がfで位相差が1/(f×n)づつ異なるn相クロックに変換するクロック変換回路1と、前記n相クロック信号の一部又は全部を用いて、周波数(f×n)/Aの単相クロック信号を生成する単相クロック生成回路2と、前記位相補間器に設定する内分比を制御する制御回路とを有し、前記各位相補間器は、前記m相の内の異なる二つのクロックを入力し、それらのタイミング差を、制御回路により設定した内分比で分割した遅延時間のクロックを生成して出力し、前記制御回路は、基準クロックと、回路の末端で分配されたクロックとのタイミングとが一致するように内分比を制御する。

(もっと読む)

位相補間回路及びその設計方法

【課題】トランジスタのばらつきによる影響を抑制し、位相歪みを解消する位相補間回路を提供する。

【解決手段】位相補間回路は、位相の異なる入力波形を受け付ける複数の差動対を含み、複数の差動対のうち、第1の差動対及び第2の差動対の出力波形を合成する位相補間回路である。さらに、複数の差動対にバイアス電流を供給する電流源をn個含み、第1の差動対に供給するバイアス電流を、n個の電流源のうち、m個の電流源から供給可能であると共に、第2の差動対に供給するバイアス電流をn個の電流源のうち、n−m個の電流源から供給可能であって、n個の電流源が供給する電流は、予め定められた単位電流値を基準として、それぞれ重み付けがされている可変電流源と、出力波形の位相シフト量に基づいて、可変電流源のm個の電流源の数を変更する制御回路と、を備えている。

(もっと読む)

集積回路及び位相制御方法

【課題】分周クロック信号とクロック信号との位相関係を適応的に制御可能な集積回路を提供する。

【解決手段】集積回路は、第1のクロック信号を分周して第2のクロック信号を生成する分周回路と、第1のクロック信号が伝搬する第1の信号伝搬経路と、第2のクロック信号が伝搬する第2の信号伝搬経路と、第1の信号伝搬経路を伝搬後の第1のクロック信号に第2の信号伝搬経路を伝搬後の第2のクロック信号を少なくとも2回掛け合わせることにより出力信号を生成するミキサ回路と、ミキサ回路の出力信号の直流成分を検出する直流検出回路と、直流検出回路が検出した直流成分に応じて第1の信号伝搬経路及び第2の信号伝搬経路の少なくとも一方の伝搬遅延量を制御する制御回路とを含む。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

アダプタ、情報機器、情報システム及び通信方法

【課題】 高価格化及び実効転送速度の低下を招くことなく、機器間の情報通信において、要輻射(EMI)を低減することができるアダプタを提供する。

【解決手段】 カードアダプタは、ボード、該ボードの一端近傍に設けられたカードエッジコネクタ315、該ボード上に実装された2つのトランシーバソケット(312A、312B)、変換素子317、及び4つのコネクタなどを有している。そして、変換素子317は、カードエッジコネクタ315と2つのトランシーバソケット(312A、312B)との間を電気的に接続する複数の配線パターンの途中に設けられ、該複数の配線パターンのクロックドメインを、クロックがスペクトラム拡散クロックであるクロックドメインと、クロックが非スペクトラム拡散クロックであるクロックドメインとに分割している。

(もっと読む)

半導体集積回路及びそのタイミング調整方法

【課題】従来技術の半導体集積回路では、タイミング調整に工数がかかるという問題があった。

【解決手段】本発明にかかる半導体集積回路は、外部メモリと接続される複数の信号線に対応して個別に設けられ前記対応する信号線のタイミングを決定する回路ブロックをマクロ化した論理セル群11〜15と、論理セル群11〜15のそれぞれに対応して設けられたIOバッファ21〜26と、を有する。そして、論理セル群11〜15と対応するIOバッファ21〜26とを結合する配線のそれぞれが略同じ長さを有することを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の回路面積の増大を抑制し、かつクロックジッタを低減できるようにする。

【解決手段】基準クロック信号を動作クロックとして動作する回路ブロックと、基準クロック信号をn分周したクロック信号を動作クロックとして動作する回路ブロックとを有する半導体装置にて、遅延回路により基準クロック信号に所定の遅延を与えて、セレクタが制御信号に応じて基準クロック信号及び遅延が与えられたクロック信号の内から1つのクロック信号を選択して基準クロック信号を動作クロックとして動作する回路ブロックに出力するようにして、電源ノイズにより生じる位相変化を合わせた基準クロック信号の位相変化量を各周期で等しくしてクロックジッタを低減できるようにする。

(もっと読む)

レイアウト装置及びレイアウト方法

【課題】クロックツリー設計において、簡潔なスキュー調整をすることができるレイアウト装置及びレイアウト方法を提供すること。

【解決手段】本発明にかかるレイアウト装置1は、想定スキュー値記憶部141、遅延挿入部133、遅延調整部134を備える。想定スキュー値記憶部141は、クロックツリーの段数に応じて予め定められた想定スキュー値を格納する。遅延挿入部133は、想定スキュー値が要求スキュー値以下である場合、当該クロックツリーの最上位側に遅延調整バッファ206を挿入する。遅延調整部134は、クロックツリーのスキュー値が要求スキュー値以下となるように、クロックツリーの配線後に、遅延調整バッファ206の遅延を調整する。

(もっと読む)

電子機器

【課題】 デジタル回路間におけるクロックスキューを調整することができる電子機器を安価に提供することを目的とする。

【解決手段】 第1クロック信号CK1を遅延させて第2クロック信号を生成する位相調整回路12と、第1クロック信号CK1に同期して動作する制御回路15と、第2クロック信号CK2に同期して動作し、制御回路15との間でデータ入出力を行う制御回路25と、制御回路15,25間の同期を判定する同期判定部153と、この判定結果に基づいて第2クロック信号CK2の遅延量を決定する遅延量制御部141とを備えている。位相調整回路12は、第1クロック信号CK1を遅延させるゲート回路120と、上記遅延量に基づく電源電圧をゲート回路120に供給する電源供給回路121とを備え、ゲート回路120の電源電圧を変化させることにより、制御回路15,25間のクロックスキューを抑制する。

(もっと読む)

クロックのデューティ・サイクルの自動制御

【課題】クロック信号の立ち下がりを調節して望ましいデューティ・サイクルを達成するデューティ・サイクル補正(DCC)回路を提供する。

【解決手段】幾つかの例では、DCC回路は、入力クロック信号の立ち下がりに応答してパルスを発生し、そのパルスを制御電圧に基づいて遅延し、遅延したパルスに基づいて入力クロック信号の立ち下がりを調節して出力クロック信号を生成し、出力クロック信号のデューティ・サイクルと望ましいデューティ・サイクルとの間の差に基づいて制御電圧を調節する。DCC回路は、望ましいデューティ・サイクルを達成するためにクロック・サイクルの立ち下がりを調節するので、クロック信号の立ち上がりを調節する既存のPLL制御ループへ、その動作に干渉することなく組み込むことができる。

(もっと読む)

LSIシステム

【課題】入力された外部信号の波形で規定される論理をより確実に判定することが可能なLSIシステムを提供する。

【解決手段】LSIシステムは、第1の入力回路と、発振回路と、発振安定化回路と、システムクロック信号をカウントするフリーランカウンタと、第2の入力回路と、第1のキャプチャ信号が入力されたときのフリーランカウンタの第1のカウント値を保持するとともに、第2のキャプチャ信号が入力されたときのフリーランカウンタの第2のカウント値を保持するキャプチャ回路と、設定値を発振安定化回路に出力するとともに、設定値に対応した補正値を出力する補正回路と、キャプチャ回路に保持された第1のカウント値と第2のカウント値との差に補正値を加算した値に基づいて、第2の外部信号の波形のエッジの間隔で規定される論理を判定する判定回路と、を備える。

(もっと読む)

メモリアクセス制御回路とメモリアクセス制御方法

【課題】処理装置と同期式メモリの間のACタイミング条件を緩和することができるメモリアクセス制御回路等を提供する。

【解決手段】プロセッサ1の基準クロック信号CLKは位相調整部10,20に与えられ、それぞれ位相の遅れたクロック信号CKDと位相の進んだクロック信号CKLが生成される。クロック制御部30は、プロセッサ1からデータの読み出し要求が行われると、クロック信号CKLを選択してクロック信号CKを同期式SRAM2へ与えると共に、データ制御部40へ出力する。データ制御部40は、位相の進んだクロック信号CKに同期して同期式SRAM2から読み出されたデータ信号DT2を、このクロック信号CKに同期してデータ信号DT1としてプロセッサ1へ出力する。一方、同期式SRAM2へのデータ書き込み動作は、位相の遅れたクロック信号CKDに同期して行われる。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

半導体装置およびデータ伝送システム

【課題】メモリ側の多相クロックのずれを補正する。

【解決手段】複数のデータ入出力端子に接続されたデータ入力回路とデータ出力回路とを備えた半導体装置であって、データ入力回路あるいはデータ出力回路の少なくとも一方が、データを取り込むタイミング信号となる位相の異なる多相クロック信号によりデータを取り込み、データを取り込む有効範囲が多相クロック信号ごとにほぼ均一になるように調整する。本発明によれば、入力あるいは出力タイミング信号である多相クロック信号を個別に調整することにより、データのウィンドウ幅を均一にすることができるため、半導体装置の特性を改善することができる。

(もっと読む)

半導体集積回路並びにその設計方法及び設計プログラム

【課題】IRDropやEMIの低減等が可能な半導体集積回路の設計方法等を提供する。

【解決手段】この半導体集積回路の設計方法は、複数のリーフセルを複数のグループにグループ分けするステップと、複数のグループの各々に対して、クロック信号の入り口としての代表セルを設けるステップと、複数のグループの各々に対して、代表セルとリーフセルの各々との間のクロック信号の遅延が略同等になるように、代表セル及びリーフセルをグループ配置領域内に配置するステップと、複数のグループをレイアウト領域内に配置するステップと、複数のグループにクロック信号を供給するためのクロックルートセルと複数のグループ内の代表セルとの間にクロックツリーシンセシスを行うステップと、を含む。

(もっと読む)

クロック生成制御回路

【課題】 CPUの負荷を軽減することが可能なクロック生成制御回路を提供する。

【解決手段】 本願発明は、発振回路が出力するクロック信号のパルス数を所定期間カウントし、所定期間及び周波数に応じた設定値と等しくなったときにカウント制御信号の出力レベルを切り替えるカウンタと、所定期間を示すタイミング信号とカウント制御信号とのタイミングの誤差を検出し、誤差検出信号を出力する誤差検出回路と、を備え、周波数制御回路は、誤差検出信号に基づいて制御信号を生成することで、上記課題を解決することができる。

(もっと読む)

遅延クロック生成装置および遅延時間測定装置

【課題】遅延クロックを高精度に生成する遅延クロック生成装置を提供することを目的とする。

【解決手段】基準クロックが、後縁合わせ部および位相制御部に入力される。リング発振器は、基準クロックと同一周期のシフトクロックを発振する。後縁合わせ部は、シフトクロックの後縁を、基準クロックの後縁に合わせる。後縁を合わされたシフトクロックは、パルス挿入部に供給される。位相制御部は、基準クロックを受け取って、挿入パルスを、シフトクロックの複数サイクル中のどのサイクルに挿入するかを定める位相制御信号を生成する。パルス挿入部は、位相制御信号により定められたシフトクロックのサイクルに、挿入パルスを挿入する。遅延位相ロック部は、基準クロックと、挿入パルスを挿入されたシフトクロックとに基づいて、リング発振器において発振されるシフトクロックの位相を基準クロックの位相に対して遅らせて、遅延クロックを生成する。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

タイミング調整回路及びそれを備えた半導体装置

【課題】テスト装置のピン間スキューによる制限を受けること無く、高い精度でタイミングずれを除去することができるタイミング調整回路を提供する。

【解決手段】タイミング調整回路30に、データ入力回路66のレプリカ回路31を設ける。レプリカ回路は、初段回路32とラッチ回路33とを含む。初段回路は、外部クロック信号を受け参照クロック信号を出力する。クロックドライバ64からの内部クロック信号に同期して、参照クロック信号をラッチし、外部出力端子34へ位相進み遅れ信号として出力する。

(もっと読む)

位相調整機能の評価方法、情報処理装置、プログラム及びコンピュータ読取可能な情報記録媒体

【課題】データ受信回路における位相調整回路の動作検証を効果的に実施し得る構成を提供することを目的とする。:

【解決手段】受信された複数のデータ信号及びクロック信号との間の位相を自動的に調整する位相調整機能を有する位相調整手段と、各位相調整手段に入力される前記クロック信号へ所定の位相量を与える位相量付与手段と、位相量付与手段によって各位相調整手段に与えられる所定の位相量を所定の態様で変化させる付与位相量変化手段と、これに応じて前記各位相調整手段が実施する前記位相調整機能の動作結果を格納手段が記憶手段に格納する格納手段とを設けた。

(もっと読む)

1 - 20 / 59

[ Back to top ]