Fターム[5B079CC02]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 調整手段 (364) | 遅延回路を用いるもの (210)

Fターム[5B079CC02]に分類される特許

1 - 20 / 210

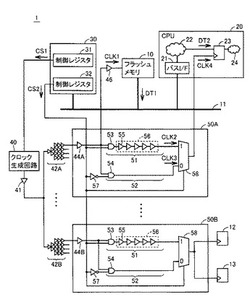

半導体装置

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

キャリブレーション処理制御装置及びキャリブレーション処理制御方法

【課題】この発明は、キャリブレーション処理後の再キャリブレーション処理要求に対して、前の処理結果を利用した簡易キャリブレーション処理を行なって処理時間の短縮を図り、実用に適するようにしたキャリブレーション処理制御装置及びキャリブレーション処理制御方法を提供することを目的としている。

【解決手段】再キャリブレーション要求で発行されたキャリブレーション要求コマンドに対するレスポンスデータについて、最後のキャリブレーション処理で検出されたサンプリングクロックの正当なサンプリングが可能な連続した位相設定範囲から、位相の異なる複数個のサンプリングクロックを選択し、その選択されたサンプリングクロックでサンプリングを行なった結果の正当性を確認することで簡易キャリブレーションを実行する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

半導体集積回路のクロック遅延調整回路およびその制御方法

【課題】回路規模が増大する問題があった。

【解決手段】複数の回路ブロックと、入力するクロック信号を遅延制御信号に基づいて遅延したクロック信号を対応する前記複数の回路ブロックに供給する複数のクロック遅延回路と、前記複数の回路ブロックの遅延試験を行う制御回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの情報を記憶する救済グループ記憶回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの遅延値情報を記憶する、所定数の遅延設定回路と、前記救済グループ記憶回路が記憶した回路ブロックの情報に対応したクロック遅延回路に対し、前記遅延設定回路が記憶した遅延値情報に応じた前記遅延制御信号を割り当てる遅延設定割当制御回路と、を有する半導体集積回路のクロック信号調整回路。

(もっと読む)

半導体装置及び遅延量調整方法

【課題】クロック信号の位相を遅延させる遅延回路とその遅延量を調整する回路とを備えた半導体装置において遅延量がクロック信号の周期的なジッタの影響を受けないようにする半導体装置及び遅延量調整方法を提供する。

【解決手段】第1のクロック信号を遅延させた第2のクロック信号を出力する可変遅延回路と、可変遅延回路における遅延量を制御する制御信号を出力する遅延量調整回路と、遅延量調整回路が制御信号を更新するタイミングを決定するタイミング信号を出力するタイミング信号発生回路と、を備えた半導体装置であって、タイミング信号発生回路は連続してタイミング信号を出力するものであって、互いに隣接するタイミング信号の間隔の内、少なくとも2つの間隔が互いに異なる。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

半導体集積回路装置、インタフェース回路

【課題】EMIを低減する半導体集積回路、インタフェース回路を提供する。

【解決手段】半導体集積回路装置(100)は、抵抗値を切り替え可能な可変抵抗部(10)と、可変遅延部(20)と、データ取り込み部(26)とを具備する。抵抗値を切り替え可能な可変抵抗部(10)は、入力されるデータ信号(DT)をダンピングする。可変遅延部(20)は、データ信号(DT)の入力タイミングを示すクロック信号(CLK)に変更可能な遅延を与える。データ取り込み部(26)は、可変抵抗部(10)によってダンピングされた信号から可変遅延部(20)によって遅延された遅延クロック信号によって示されるタイミングでデータを取り込む。

(もっと読む)

半導体装置

【課題】広い変動幅で入力信号を遅延させる一方、入力端に加えられるローディング及びその動作電流量を最小限に維持することができる遅延ラインを備える半導体装置を提供すること。

【解決手段】遅延制御コードONC_PUBに応じて、入力信号を遅延して第1の遅延入力信号及び第2の遅延入力信号を出力する共通遅延部200と、遅延制御コードCON_1に応じて、第1の遅延入力信号を遅延して第1の出力信号を出力する第1の遅延部220と、遅延制御コードCON_2に応じて、第2の遅延入力信号を遅延して第2の出力信号を出力する第2の遅延部240とを備え、共通遅延部から伝達される第1の遅延入力信号が第1の遅延部中を通過する長さである第1の遅延経路と、共通遅延部から伝達される第2の遅延入力信号が第2の遅延部中を通過する長さである第2の遅延経路とに、所定の長さの差があることを特徴とする。

(もっと読む)

マルチコアプロセッサ及びこれを用いる車載電子制御装置

【課題】各コアの動作周波数を時系列で適切に変動させることで、放射ノイズ等の問題点を少なくとも部分的に解決すること。

【解決手段】 本発明は、複数のコアを搭載したマルチコアプロセッサ1,2であって、複数のコアA,B,Cは、同一の周期Tで周期的に周波数が変動する動作クロックで動作するように構成され、コアの動作クロックの周波数の変動位相が、前記複数のコア間でずらされることを特徴とする。好ましくは、各コアの動作クロックの周波数の変動位相は、時間T/N(Nはコア数)に相当する位相ずつずらされる。好ましくは、コアの動作クロックの周波数の変動態様は、複数のコア間で、変動位相が異なる以外は同一である。

(もっと読む)

集積回路

【課題】内部クロック発生回路を備え、実動作試験が、安定して正確に行える集積回路の実現。

【解決手段】外部クロックEXCLKを逓倍して内部クロックPLLCLKを発生する内部クロック発生回路20と、PLLCLKで動作し、外部バスとは非同期でデータを入出力するインターフェースを含み、トランザクション信号CSに応じて、外部バスとの間でデータの入出力動作を行う内部回路11と、を備える集積回路であって、CSを所定時間遅延し、CSの変化から所定時間の間アクティブになる停止信号CSEDGEを発生する遅延回路22-24と、試験モード時に、内部回路への内部クロックの供給を停止信号がアクティブの間停止し、停止信号が非アクティブなった後、内部クロックに同期して内部回路への内部クロックの供給を再開するように制御するクロック制御回路21と、を備える。

(もっと読む)

集積回路のメモリインターフェースのためのデューティサイクル補正器回路

集積回路(IC)内のデューティサイクルの歪みを補正するための回路および方法が、開示される。ICは、クロック信号を受信するように連結されるスプリッタ回路を含む。クロック信号は、2つの異なるクロック信号に分割される。クロック信号のうちの1つは、他方の反転したバージョンである。遅延回路は、クロック信号の各々に連結される。遅延回路の各々は、対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方を受信するように連結される。補正器回路は、補正されたデューティサイクルを有するクロック出力信号を発生させる。  (もっと読む)

(もっと読む)

クロックツリー合成装置、クロックツリー合成方法及びプログラム

【課題】半導体集積回路のCTSにおいて、クロック遅延時間を削減すること。

【解決手段】CTS装置は、クロックドメインに接続された複数のフリップフロップの重心座標を求め、求めた重心座標と各フリップフロップとの距離を算出し、重心座標から遠いフリップフロップから順に、重心座標からのクロックラインにおける遅延時間をクロック遅延時間として算出し、前段のフリップフロップとの距離を求め、求めた距離からデータパスにおける遅延時間をデータ遅延時間として算出し、クロック遅延時間とデータ遅延時間との和がクロックドメインのクロックの1周期よりも長いフリップフロップを選択し、選択されたフリップフロップと前段のフリップフロップとのデータパスがフォルスであると判定された場合には、選択されたフリップフロップをスキュー調整の対象外としてクロックツリーを合成する。

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

半導体集積回路の設計方法、設計装置およびプログラム

【課題】製造バラつきの下で、クロックスキューの最小化しつつ、クロック信号部での消費電力を最小化する半導体集積回路の設計方法、設計装置および、コンピュータプログラムを提供する。

【解決手段】メッシュ配線構造を駆動するバッファツリーを生成するグローバルクロック構造生成部104と、クロック素子の配置分布とクロックゲーティング構造を考慮してクラスタを生成するクロック素子クラスタ生成部106と、そのクラスタに含まれるクロック素子が属するゲーティッド回路にクロック信号を分配するゲーティングセルを複製して、クラスタを駆動するゲーティングセルとして挿入するゲーティングセル複製・挿入部107と、ローカルクロック構造生成部109と、タイミング解析結果に基づき、クロック素子クラスタを駆動するゲーティングセルの駆動能力を調整するゲーティングセル駆動能力調整部111と、を備える。

(もっと読む)

半導体装置、および該半導体装置における遅延回路の遅延コード自動設定方法

【課題】入力されるデータ信号のセットアップ及びホールド時間を調整する遅延回路における最適な遅延時間(遅延コード)を、半導体装置の実際の動作条件下において自動的に設定する。

【解決手段】パッド11から、ターゲットとなるデータ信号ADD/CMDを遅延回路13に入力し、遅延回路13の遅延コードCODET<2:0>を変えて、遅延回路から出力される遅延信号の遅延時間を変化させる。そして、この遅延された信号をラッチ回路14によりラッチし、遅延された信号PA0DBとラッチされたデータ信号PA2Bとの一致または不一致を判定し、一致すると判定した場合に、この判定結果に基いて遅延コードCODET<2:0>を決定し、決定後の遅延コードにより遅延回路13を動作させる。

(もっと読む)

スキュー調整回路およびスキュー調整方法

【課題】遅延量の設定を高速に実行する。

【解決手段】入力されるデータ信号DATおよびクロック信号CLK間のスキューを調整するためのスキュー調整回路11は、データ信号DATを可変遅延量だけ遅延させた可変遅延信号DDATを生成して出力すると共に、データ信号DATを固定遅延量だけ遅延させた固定遅延信号を、複数の固定遅延量ごとに生成する可変遅延回路12と、可変遅延回路12が生成した複数の固定遅延信号の位相とクロック信号CLKの位相とを比較する位相比較器13と、位相比較器13の比較結果に対応する遅延量を可変遅延量として、第1の信号を遅延させる制御信号を可変遅延回路12に送信する遅延制御回路14とを備える。

(もっと読む)

クロック生成回路及びこれを備える半導体装置並びにデータ処理システム

【課題】クロック生成回路において、カウンタ回路のスタックやロック動作の遅延を防止する。

【解決手段】位相判定信号PD0を生成する位相判定回路120と、位相判定信号PD0をサンプリングしこれに基づいて位相判定信号PD2を生成するサンプリング回路130と、位相判定信号PD2に基づいて内部クロック信号LCLKを生成するクロック生成部110とを備える。サンプリング回路130は、サンプリング周期内に位相判定信号PD0の論理レベルが変化した場合に位相判定信号PD2を固定する連続判定回路132と、位相判定信号PD1がハイレベルを示すまで位相判定信号PD2をハイレベルに固定する初期動作回路133と、位相判定信号PD1がハイレベルを示した後、連続判定回路132の動作を無効化する無効化回路134とを備える。

(もっと読む)

1 - 20 / 210

[ Back to top ]