Fターム[5C006AF75]の内容

Fターム[5C006AF75]に分類される特許

1 - 20 / 88

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】非選択期間において、出力信号のノイズが小さく、且つトランジスタの特性劣化を抑制できる液晶表示装置の駆動回路を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを設け、第1のトランジスタにおいて、第1端子を第1の配線に接続し、第2端子を第2のトランジスタのゲート端子に接続し、ゲート端子を第5の配線に接続し、第2のトランジスタにおいて第1端子を第3の配線に接続し、第2端子を第6の配線に接続し、第3のトランジスタにおいて第1端子を第2の配線に接続し、第2端子を第2のトランジスタのゲート端子に接続し、ゲート端子を第4の配線に接続し、第4のトランジスタにおいて第1端子を第2の配線に接続し、第2端子を第6の配線に接続し、ゲート端子を第4の配線に接続する。

(もっと読む)

液晶装置の駆動回路、液晶装置、電子機器

【課題】従来の液晶装置では、劣化を軽減することが困難である。

【解決手段】画素電極93と共通電極97との間に液晶が挟持される液晶装置の駆動回路であって、共通電極97に供給する共通電位Vcomを発生する共通電位発生回路133と、共通電位発生回路133の出力部に電気的に接続されると共に、電源に電気的に接続され、電源電位VDDが共通電位Vcomを下回っている状態において、共通電極97とグランドGNDとの間を導通させるスイッチング回路133と、を備えることを特徴とする液晶装置の駆動回路。

(もっと読む)

半導体装置

【課題】トランジスタが仮にディプレッション型である場合でも、安定して動作することができる半導体装置を提供する。

【解決手段】開示する発明の一態様の半導体装置は、第1の電位を第1の配線に供給する機能を有する第1のトランジスタと、第2の電位を第1の配線に供給する機能を有する第2のトランジスタと、第1のトランジスタのゲートに第1のトランジスタがオンをオンにするための第3の電位を供給した後、第3の電位の供給を止める機能を有する第3のトランジスタと、第2の電位を第1のトランジスタのゲートに供給する機能を有する第4のトランジスタと、第1の信号にオフセットを施した第2の信号を生成する機能を有する第1の回路と、を有し、第4のトランジスタのゲートには、第2の信号が入力され、第2の信号の最小値は、第2の電位未満の値である。

(もっと読む)

表示装置

【課題】TFTの閾値電圧がシフトしても、駆動回路の高い信頼性を確保することができ

る表示装置を提供する。

【解決手段】出力回路が有するトランジスタのゲートに、順方向バイアスの電圧または逆

方向バイアスの電圧を与えることができる電源制御回路と、出力回路が有するトランジス

タの閾値電圧の変化量をモニターするためのモニター用トランジスタと、出力回路が有す

るトランジスタの閾値電圧を補正するべく、該トランジスタのゲートに逆方向バイアスの

電圧を与えるように電源制御回路を制御する閾値制御回路と、を有する。

(もっと読む)

温度測定装置、温度測定装置のセンサー制御方法、表示装置及び電子機器

【課題】温度を検出する温度センサーの信頼性を確保する。

【解決手段】温度測定装置20は、第1温度センサー21と、第2温度センサー22と、温度検出制御回路200とを有する。温度検出制御回路200は、第1温度センサー21によって検出された温度から所定の時間長における温度変化を求め、当該温度変化が閾値よりも大きいか否かを判別し、当該温度変化が前記閾値よりも大きいと判別した場合に、信号S2をHレベルにして、第2温度センサー22をアクティブ状態とさせる一方、当該温度変化が前記閾値以下である判別した場合に、信号S1をLレベルにして、第2温度センサー22をノン・アクティブ状態とさせる。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバI

Cの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化

を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジス

タを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電

位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック

信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力

することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給

する。

(もっと読む)

液晶表示装置

【課題】ソースフォロワ出力の線形領域を従来より拡大する。

【解決手段】画素10内のソースフォロワ用PMOSトランジスタTr13及びTr14は、ゲートが保持容量Cs1、Cs2に接続されて常にオン状態で使用されるため、ソースフォロワ用PMOSトランジスタTr13及びTr14の閾値電圧Vthのみが+0.5Vに設定され、ノーマリーオン状態とされる。ソースフォロワ用PMOSトランジスタTr13及びTr14の電流値は定電流負荷トランジスタTr7で制御し、オンオフは定電流負荷トランジスタTr7とスイッチング用NMOSトランジスタTr5、Tr6で制御する。また、トランジスタTr5、Tr6が介在し出力可能の電圧範囲が存在するため、ソースフォロワ用PMOSトランジスタTr13及びTr14の閾値電圧Vthのシフトによって線形性を保つ領域が最大になるように最適化する。

(もっと読む)

液晶表示装置

【課題】ソースフォロワ用トランジスタの基板効果を無くしてリニアリティを改善する。

【解決手段】ソースフォロワ用PMOSトランジスタTr3、Tr4は、ソースがバックゲートに接続されている。PMOSトランジスタTr8は、画素部の同一列方向の各画素に共通に接続されている。このTr8は、各画素内のソースフォロワ用PMOSトランジスタTr3、Tr4のソースとバックゲートに共通に接続された定電流用トランジスタである。トランジスタTr3、Tr5、Tr4、Tr6、Tr7及びTr8は、保持容量C1に保持された正極性の画素値と、保持容量C2に保持された負極性の画素値とを、垂直走査周期より短い周期で交互に画素電極PEへ読み出す読み出し部を構成している。ソースフォロワ用PMOSトランジスタTr3、Tr4の閾値電圧Vth3、Vth4は、信号レベル(ゲート電圧)により変動しない(基板効果がない)状態となり固定の電圧となる。

(もっと読む)

表示ドライバ及びそれを備えた表示装置

【課題】所望の分散時間にて動作することが可能な表示ドライバ及びそれを備えた表示装置を提供すること。

【解決手段】本発明にかかる表示ドライバは、外部から入力される映像信号を増幅して増幅信号を生成する複数のパネル駆動用アンプと、対応する増幅信号を外部に出力するか否かを、対応する出力制御信号に基づいて制御する複数の出力制御回路と、外部から入力される出力タイミング信号を遅延させて生成した複数の遅延信号を出力し、対応する前記遅延信号に基づいて対応する前記出力制御信号を生成するカスケード接続された複数の遅延ブロックと、を備え、2つ以上の前記遅延回路の遅延値を共通の遅延制御信号によって制御する。

(もっと読む)

レベル変換回路および表示装置、並びに電子機器

【課題】回路構成の複雑化、消費電流の増加、特性低下を防止することができ、レイアウト面積の削減を図れるレベル変換回路および表示装置、並びに電子機器を提供する。

【解決手段】バイアス部12は、第5のNMOSトランジスタNT15と、抵抗素子R11を含む降圧部16と、電圧源15に接続された電流源I11と、を含み、第5のNMOSトランジスタNT15のソースが第1電圧源14に接続され、ドレインが抵抗素子R11の一端に接続され、抵抗素子R11の他端が電流源I11に接続され、第5のNMOSトランジスタNT15のゲートが抵抗素子R11の他端側に接続され、第1電圧から第1および第2のNMOSトランジスタNT11,NT12のしきい電圧分高く、または第1電圧より高くこのしきい値電圧より低いバイアス電圧を抵抗素子の一端側に生成し、レベル変換部11の第1および第2のNMOSトランジスタNT11,NT12のゲートに供給する。

(もっと読む)

駆動回路及び画像表示装置

【課題】シフトレジスタの各段の単位駆動回路において、当該段が出力動作を行わない期間にてオン状態に維持されるトランジスタがしきい値電圧のシフトを生じる。

【解決手段】出力動作期間以外にて単位駆動回路の出力端子OUTをLレベルに設定するスイッチとして、OUTと交流電源VA,VBとの間に複数のトランジスタT6A,T6Bを接続する。T6A,T6Bは、出力動作期間以外にて少なくとも1つがオン状態とされ、かつ交代してオフ状態とされる。T6AはVAに、またT6BはVBに接続され、それぞれのオン期間には交流電源はLレベルを供給し、オフ期間にはHレベルとLレベルとの中間電位である接地電位GNDを供給する。

(もっと読む)

レベルシフタ回路および表示ドライバ回路

【課題】回路面積を大きくすることなく入力信号に対する応答速度が速いレベルシフタ回路および表示ドライバ回路を提供することである。

【解決手段】本発明にかかるレベルシフタ回路1は、第1の電圧変換回路11、第2の電圧変換回路12を備える。第1の電圧変換回路11は、電源電位GNDと電源電位VDDLとの間の振幅を有する入力信号INが入力されると共に、電源電位VDDLよりも高い電源電位VDDHが供給される。また、電源電位VDDHの電源線41から供給される電流を制限する電流制限回路34を備え、入力信号INよりも大きな振幅を有する電圧信号を入力信号INに応じて出力する。第2の電圧変換回路12は、電源電位VDDHが供給されると共に、第1の電圧変換回路11から出力された電圧信号に応じて電源電位GNDと電源電位VDDHとの間の振幅を有する出力信号を出力する。

(もっと読む)

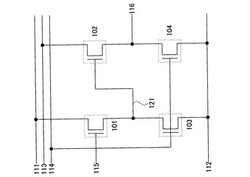

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

双方向シフトレジスタ、及びこれを用いた画像表示装置

【課題】シフトの方向に応じて回路構成を切り替える単位レジスタ回路を従属接続した双方向シフトレジスタは小型化が難しい。

【解決手段】単位レジスタ回路38は、基準点N1がHレベルのとき、4相クロック信号のうちトランジスタT5のドレインに入力されるパルスに同期して端子NOUTにパルスを出力する。セット端子NSFは1つ前の段、セット端子NSBは1つ後の段、リセット端子NRFは2つ後の段、リセット端子NRBは2つ前の段の出力にそれぞれ接続される。単位レジスタ回路38はいずれかのセット端子にパルスを入力されると基準点をHレベルに設定し、いずれかのリセット端子にパルスを入力されると基準点をLレベルに設定する。シフト方向に応じてクロック信号の相間の位相の変化順序が反転され、またスタートトリガ信号を先頭段、後尾段のいずれに印加するかが切り替えられる。

(もっと読む)

液晶表示装置、液晶表示装置の駆動方法、及び、電子機器

【課題】階調を反映した信号電位を保持する容量素子をDRAMとして利用し、画素構造の簡略化を図るに当たり、低消費電力化を可能にする。

【解決手段】階調を反映した信号電位を保持する保持容量22をDRAMとして利用することで、画素20の構造の簡略化を図る。そして、画素20において、保持容量22の極性反転動作及びリフレッシュ動作を行うためのインバータ回路23の入力端に対して、第4のスイッチングトランジスタ27による反転電位の書き込み後の一定期間、信号線31から第1,第3のスイッチングトランジスタ24,26を通じて電源電位、例えば、接地(GND)電位を与える。これにより、インバータ回路23の入力電位INVinを接地電位に確定し、インバータ回路23に貫通電流が流れないようにする。

(もっと読む)

液晶表示装置

【課題】液晶表示装置において、画素トランジスタの長寿命化と消費電力を低減させるゲート信号の波形をより簡易な構成により出力する。

【解決手段】各画素の液晶の配向を制御する画素トランジスタのゲートに入力されるゲート信号を出力し、各画素が並べられたライン毎に配置された複数のシフトレジスタ回路(281,282)と、奇数ラインシフトレジスタ回路(281)に入力される第1クロック出力線CK1と、偶数ラインシフトレジスタ回路(282)に入力される第2クロック出力線CK2と、を備え、第1クロック出力線CK_A及び第2クロック出力線CK_Bには、1画面分を表示する期間であるフレーム期間ごとに第1クロック信号CK_A及び第2クロック信号CK_Bの2種類の異なるクロック信号が交互に印加され、第1クロック信号CK_A及び第2クロック信号CK_Bは、周期が同じで位相が異なるクロック信号である。

(もっと読む)

電気光学装置

【課題】電気光学装置の走査線駆動回路において、救済用の単位シフトレジスタの駆動能力の向上および動作の高速化を図る。

【解決手段】救済用単位シフトレジスタSRBkは、液晶アレイ部10を挟んで正規の単位シフトレジスタSRの反対側に配設される。救済用単位シフトレジスタSRBkは、2行前のゲート線駆動信号Gk-2を受け、その活性化の2水平期間後に活性化するクロック信号に同期して、自己が出力するゲート線駆動信号Gkを活性化させる。

(もっと読む)

シフトレジスタ回路

【課題】シフトレジスタ回路の駆動能力の向上、および動作の高速化を図る。

【解決手段】シフトレジスタ回路は、クロック信号CLKを出力端子OUTに供給するトランジスタQ1と、当該トランジスタQ1のゲート(ノードN1)を放電するトランジスタを駆動するインバータとを備える。インバータの入力ノード(ノードN3)は、ノードN1から分離されており、ノードN1,N3はそれぞれ個別の回路によって充放電される。

(もっと読む)

画素回路、これを利用した表示装置及び表示装置の駆動方法

【課題】画素回路、これを利用した表示装置及び表示装置の駆動方法を提供する。

【解決手段】2つの走査トランジスタを含む表示装置用画素回路。2つの走査トランジスタは、アニーリング区間とオフ区間とを反復するように駆動される。アニーリング区間によって走査トランジスタのしきい電圧がシフトされることにより、漏れ電流が発生することを防止できる。

(もっと読む)

差動増幅器およびその制御方法

【課題】高スルーレートの差動増幅器を提供する。

【解決手段】差動増幅器は、差動入力信号を受ける差動対トランジスタ(TN12/TN13、TP12/TP13)と、定電流源(ICS11、ICS12)と、スイッチ(TN11、TP11)とを具備する。定電流源(ICS11、ICS12)は、差動対トランジスタ(TN12/TN13、TP12/TP13)に流れる電流を制御する。スイッチ(TN11、TP11)は、定電流源(ICS11、ICS12)と並列に配置され、差動入力信号の反転動作に同期して差動入力信号の反転動作の遷移時間より短い時間だけ差動対トランジスタTN12/TN13、TP12/TP13)に流れる電流を増加する。

(もっと読む)

1 - 20 / 88

[ Back to top ]