Fターム[5C006BC05]の内容

Fターム[5C006BC05]の下位に属するFターム

3端子型(TFT、FET) (1,869)

2端子型(非線形素子、MIM) (26)

半導体等の積層構造 (64)

Fターム[5C006BC05]に分類される特許

1 - 20 / 63

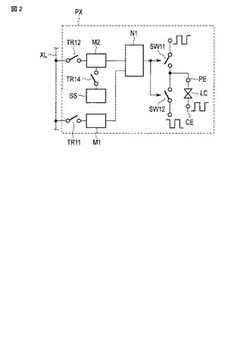

表示装置及び表示装置の駆動方法

【課題】入力位置情報の処理速度が速く、全てのユーザにとってあらゆる場面で容易に利用が可能である表示装置及び表示装置の駆動方法を提供する。

【解決手段】表示装置は、複数の信号線XLと、それぞれ画素電極PEと、画素制御スイッチとを有し、複数の画素群の何れかに分類される複数の画素PXと、を備える。画素群は、メモリと、入力情報を検知した際に検知信号のデータをメモリに与えるように構成されたセンサ回路と、を有する。画素制御スイッチは、信号線XLを介して入力される表示信号のデータと、メモリから入力される検知信号のデータと、に応じて画素電極PEの電圧レベルを切替える。

(もっと読む)

表示装置および電子機器

【課題】表示画質を向上させることが可能な表示装置および電子機器を提供する。

【解決手段】表示装置1は、表示素子(液晶素子LC)を含む複数の画素10と、互いに異なる階調電位を保持する複数種類の電位線(黒電位線LBおよび白電位線LW)と、複数種類の電位線のうちの選択された1種の電位線の階調電位が表示素子に対して供給されるように、映像信号に基づいて各画素10の表示駆動を行う駆動部とを備えている。表示素子への印加電圧または印加電流の変動量に対する表示輝度の変動量に対応する輝度勾配が相対的に急峻である階調電位(例えば黒階調電位)を保持する第1の電位線(例えば黒電位線LB)の抵抗値が、輝度勾配が相対的に緩やかである階調電位(例えば白階調電位)を保持する第2の電位線(例えば白電位線LW)の抵抗値と比べて低くなっている。

(もっと読む)

液晶表示装置、液晶表示装置の制御方法、液晶表示装置の制御プログラム

【課題】 フリッカを抑制する液晶表示装置を提供すること。

【解決手段】 上記課題を解決するために、本発明の液晶表示装置は、光源からの光を変調する光変調素子と、前記光変調素子からの光を検出する光検出手段と、前記光変調素子に印加する電圧値を設定する制御手段を有する液晶表示装置であって、フリッカを低減するために、前記光変調素子に印加する電圧値を調整する調整モードにおいて、前記制御手段は、前記光検出手段の検出結果の振幅が小さくなるように調整した第1の電圧値を設定し、前記光変調素子に対して電圧が印加されない期間の後に、前記光変調素子に対して電圧を印加するときは、前記第1の電圧値よりも低い第2の電圧値を設定することを特徴とする。

(もっと読む)

電気光学装置の駆動回路、電気光学装置及び電子機器

【課題】画素への書込極性を指定する極性信号を用いないで、当該書込極性に対応した容

量線駆動を実現する。

【解決手段】容量線駆動回路150において、第2ラッチ回路152は、一垂直走査期間

で一の容量線に対応する走査線よりも先に選択される所定の走査線に対する走査信号が供

給されたとき、自身が保持する信号をラッチする。第1ラッチ回路151は、前記一垂直

走査期間で前記一の容量線に対応する走査線よりも後に選択される所定の走査線に対する

走査信号が供給されたとき、第1ラッチ回路151でラッチされた信号を論理反転した信

号をラッチする。信号出力回路154は、第1ラッチ回路151が保持する信号が第1論

理レベルのときは第1電位信号を、第2論理レベルのときは第2電位信号を前記一の容量

線に供給する。

(もっと読む)

表示装置、表示装置の制御方法、及び、電子機器

【課題】垂直同期信号に同期させた画素データの書き換えではなく、顧客側から画素データの書き換え要求をもらうことによって任意のタイミングで書き換え処理を行えるようにする。

【解決手段】外部コントローラ40側からもらう表示データは1画面分ではなく、書き換えを行う領域に属する画素4についての表示データとし、この部分的な表示データをバッファメモリ32に一旦保持する。そして、外部コントローラ40から画面リフレッシュコマンドを受けることで、ドライバIC3による駆動の下に、外部コントローラ40との間におけるデータ伝送に垂直同期信号Vsyncが介在しなくても、バッファメモリ32に格納した表示データを基に画素データの書き換え処理を行う。

(もっと読む)

液晶表示装置

【課題】マルチ画素技術にブロック反転駆動法を適用した場合の列方向(ソースバスラインに沿った方向)に隣接する画素行ごとに生じる輝度むらの発生を抑制する。

【解決手段】画素は、第1副画素および第2副画素を有する。垂直走査期間は、連続する複数の奇数行または偶数行の画素を順次走査する第1サブ垂直走査期間と、第1サブ垂直走査期間に連続し、第1サブ垂直走査期間において飛び越された複数の偶数行または奇数行の画素を順次走査する第2サブ垂直走査期間とを含む。ソースバスラインのそれぞれに供給されるソース信号電圧の極性は、一定のシークエンスに従って変化しており、シークエンスは、ソース信号電圧の極性が互いに異なる連続する2つのサブ垂直走査期間を含み、ソースバスラインに沿って隣接する2つの画素は、第1副画素および第2副画素の内の一方の副画素がソースバスラインに沿って隣接するように配置されている。

(もっと読む)

立体映像表示装置

【課題】1台の液晶プロジェクタで立体映像を表示する場合のクロストークを低減させることができるような立体映像表示装置を提供する。

【解決手段】信号処理部101は、入力される3D映像信号から左目用信号、右目用信号が時間的に交互に並べ替えられた信号に変換する。液晶表示素子の駆動装置102は、ステップビットパルスにより全サブフレームを構成し、駆動階調が1のとき最後のサブフレームが駆動状態となり、駆動階調が1増加する毎に駆動状態となるサブフレームが1個ずつ既に駆動状態となっているサブフレームの前に向かって増加していく駆動階調テーブルによりサブフレームデータを作成するサブフレームデータ作成部26を有する。液晶表示素子6は、駆動装置で駆動される。照明光学系1は液晶表示素子に照明光を入射させる。投射レンズ11は、液晶表示素子から射出された変調光を投射する。

(もっと読む)

画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置

【課題】超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な画素回路を提供する。

【解決手段】電気光学素子と、第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、第2スイッチ素子の制御端子に一方の電極端子が接続され、第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子と、電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する第1容量素子及び第2容量素子と、を備え、電気光学素子に保持された画像データに対応する電圧レベルが、第1スイッチ素子を介して第1容量素子にサンプリングされ、第2スイッチ素子を介して第2容量素子にサンプリングされることを特徴とする、画素回路が提供される。

(もっと読む)

液晶表示素子及びその駆動方法

【課題】ランプ信号を用いることなくDA変換を行う構造とすることでランプ信号の波形の変形による表示画像の不具合を解消する。

【解決手段】1H内において、表示する映像信号の画素値と一定周期のクロックを計数するカウンタのカウンタ値とを比較し、画素値とカウンタ値とが一致した時に、データ線VDjの電位がそれまでのaからbに変化する。蓄積ゲートGSは、ゲート線AGiの電圧が、電位aよりも低い電位cから電位よりも高い電位dに変化した時に、VDjから一定量の電荷を転送されて蓄積する。転送ゲートGTは、ゲート線TGiの電圧が、電位cよりも低い電位eから電位cよりも高い電位fに変化した時に、上記の蓄積電荷を保持容量CSに転送して保持させる。データ線VDjの電位がbに変化するまで、上記の蓄積と転送の動作を巡回的に繰り返し、その繰り返し回数に応じた電荷量を保持容量CSに保持する。

(もっと読む)

液晶表示装置

【課題】各画素内の正極性信号側画素回路部と負極性信号側画素回路部で互いに対になっている回路構成要素及び配線同士を、仮想の画素中心線に対して線対称で配置構成することにより、画素ピッチを増大させることなく液晶素子に正常な駆動電圧を印加する。

【解決手段】Vdd配線102、Cs1接続配線104、データ線Di+用配線106などの正極性信号側画素回路部の配線と、Vdd配線103、Cs2接続配線105、データ線Di-用配線107などの負極性信号側画素回路部の配線とは、画素中心線II−II’に対して対応する配線同士が線対称位置に配置されている。Vdd配線102とVdd配線103とは、1画素内の左右両端に配置されているため、左右両隣の画素のCs1接続配線、又はCs2接続配線からのクロストークを抑制するガードパターンの役割を果たしている。データ線Di+用配線106及びデータ線Di-用配線107は、画素の中心部付近に配置されている。

(もっと読む)

液晶表示装置、液晶表示装置の駆動方法、及び、電子機器

【課題】階調を反映した信号電位を保持する容量素子をDRAMとして利用し、画素構造の簡略化を図るに当たり、低消費電力化を可能にする。

【解決手段】階調を反映した信号電位を保持する保持容量22をDRAMとして利用することで、画素20の構造の簡略化を図る。そして、画素20において、保持容量22の極性反転動作及びリフレッシュ動作を行うためのインバータ回路23の入力端に対して、第4のスイッチングトランジスタ27による反転電位の書き込み後の一定期間、信号線31から第1,第3のスイッチングトランジスタ24,26を通じて電源電位、例えば、接地(GND)電位を与える。これにより、インバータ回路23の入力電位INVinを接地電位に確定し、インバータ回路23に貫通電流が流れないようにする。

(もっと読む)

液晶表示装置及びその駆動方法

【課題】表示品質を向上させた液晶表示装置及びその駆動方法を提供すること。

【解決手段】

本発明の一実施形態に係る液晶表示装置は、ゲート線と、前記ゲート線と絶縁されて交差し、データ電圧を供給するデータ線、前記ゲート線及び前記データ線から分離され、一定の電圧を伝達する共通電圧線と、前記ゲート線及び前記データ線と接続される第1スイッチング素子と、前記ゲート線及び前記データ線と接続される第2スイッチング素子と、前記第1スイッチング素子と接続される第1液晶キャパシタと、前記第2スイッチング素子と接続される第2液晶キャパシタと、前記第2スイッチング素子と接続される入力端子、フローティングされた制御端子、及び出力端子を含む第3スイッチング素子と、前記第3スイッチング素子及び前記共通電圧線と接続される第3キャパシタとを含む。

(もっと読む)

液晶表示装置

【課題】バックライト装置の光源各々の輝度を中央部から外周に向かって徐々に低下させる構成において画面全体の輝度ムラを抑制しつつ極力省電力化を図ることのできる液晶表示装置を提供すること。

【解決手段】液晶パネルの垂直方向や水平方向に配列された複数の光源により該液晶パネルを背後から照明する際に,光源各々の輝度を液晶パネルの中央部から外周に向かって徐々に低下するように傾斜させる構成において,液晶パネルの表示映像の1フレームにおける変化量が小さいほど輝度傾斜が小さく(図3(b)参照),該変化量が大きいほど輝度傾斜が大きくなるように光源各々の輝度を制御する(図3(c)参照)。

(もっと読む)

2ステージD/Aコンバータ及びこれを用いた液晶表示装置のソースドライバ

【課題】高解像度の液晶表示装置のソースドライバに用いられる斬新なD/Aコンバータ及び液晶表示装置のソースドライバを提供する。

【解決手段】ソースドライバは2ステージD/Aコンバータを含む。この2ステージD/Aコンバータは、1ビットシリアル電荷再分配D/Aコンバータと、電圧選択手段と、ガンマ校正エキスパンディングと決定論理と、を含む。1ビットシリアル電荷再分配D/Aコンバータは、第1容量と、端末容量と、第1スイッチ回路と、第2スイッチ回路と、を含む。第1容量は容量充電節点(ノード)とロー参考電圧入力節点の間に接続される。端末容量は電荷収集節点とロー参考電圧入力節点の間に接続される。第1スイッチ回路は、容量の充電周期において、容量充電節点をロー参考電圧入力節点またはハイ参考電圧入力節点に接続する。第2スイッチ回路は、電荷の再分配周期において、容量充電節点を電荷収集節点に接続する。

(もっと読む)

2ステージD/Aコンバータ及びこれを用いた液晶表示装置のソースドライバ

【課題】高解像度の液晶表示装置のソースドライバに用いられる斬新なD/Aコンバータ及び液晶表示装置のソースドライバを提供する。

【解決手段】ソースドライバは2ステージD/Aコンバータを含む。この2ステージD/Aコンバータは、入力されたMビットのデジタルコードによってアナログ電圧を出力する。ソースドライバは、2ビットシリアル電荷再分配D/Aコンバータと、電圧選択手段と、を含む。2ビットシリアル電荷再分配D/Aコンバータは、ハイ参考(参照)電圧を受けるハイ参考電圧入力節点(ノード)及びロー参考電圧を受けるロー参考電圧入力節点を有する。電圧選択手段は、前記Mビットのデジタルコードの少なくとも一部によって前記ハイ参考電圧と前記ロー参考電圧を選択電圧に設定する。

(もっと読む)

表示装置

【課題】表示装置における表示映像が、人体や物体により遮られた場合でも、ユーザが必要な情報を得ることができる表示装置を提供する。

【解決手段】表示装置1は、映像を表示する表示パネル10と、表示パネル10における表示映像を遮蔽する物体等を検知するセンサと、前記センサにより検知された物体等により表示パネル10における前記表示映像が遮られる遮蔽領域10a、又は、遮られない非遮蔽領域10bの位置情報を検知する領域検知部と、前記位置情報に基づき、非遮蔽領域10bに表示中の映像を縮小表示する表示制御部を備える。

(もっと読む)

一体型タッチスクリーン

【課題】ディスプレイの表示画素スタックアップに一体化されたタッチ感知回路を有するディスプレイ。

【解決手段】表示画素スタックアップにおける駆動線及び感知線のようなタッチ信号線並びに接地領域などの回路素子を共にグループ化し、ディスプレイ上又はその近傍のタッチを感知するタッチ感知回路を形成する。一体型タッチスクリーンは、ディスプレイシステムの回路として動作してディスプレイ上に画像を生成することができる多機能回路素子を含み、更に、ディスプレイ上又はその近傍での1つ又はそれ以上のタッチを感知するタッチ感知システムの一部を形成する。多機能回路素子は、例えば、ディスプレイシステムにおける表示回路のストレージキャパシタ/電極、共通電極、導電線/導電路、その他として動作するよう構成され、更に、タッチ感知回路の回路素子として動作するよう構成することもできる表示画素内のキャパシタとする。

(もっと読む)

アクティブマトリクス型ディスプレイ装置及びこれを有する電子機器

【課題】画素内蔵記憶回路を有しながら低消費電力を実現するアクティブマトリクス型ディスプレイ装置等を提供する。

【解決手段】行及び列のマトリクス状に配置された複数の画素100の夫々は、第1の端子及び第2の端子を有し、第2の端子が一定電位に接続される表示素子Clと、表示素子Clの第1の端子への画像データの供給を制御する制御スイッチQ11と、第1の端子及び第2の端子を有し、第1の端子が表示素子Clの第1の端子へ接続され、表示素子Clへ制御スイッチQ11を介して供給される画像データを保持する保持容量Csと、表示素子Clの第1の端子での電圧状態を記憶する記憶回路200とを有する。ディスプレイ装置は、記憶回路200のリフレッシュ動作に同期して、2以上の多段階に切り替わる電圧を保持容量Csの第2の端子に供給する電圧供給部40を有する。

(もっと読む)

表示装置

【課題】表示装置の消費電力を低減し、且つ表示品質の低下を抑制すること。

【解決手段】表示装置の各画素に設けられるトランジスタとして、酸化物半導体層を具備するトランジスタを適用する。なお、当該酸化物半導体層を高純度化することで、当該トランジスタのオフ電流を少なくすることが可能である。そのため、当該トランジスタのオフ電流によるデータ信号の値の変動を抑制することができる。すなわち、当該トランジスタが設けられた画素へのデータ信号の書き込み頻度を低減した場合(休止期間が長期化した場合)における表示の劣化(変化)を抑制することができる。加えて、休止期間において信号線に供給される交流の駆動信号の周波数を低減した場合における表示のちらつきを抑制することができる。

(もっと読む)

液晶装置、電子機器、および投射型表示装置

【課題】デジタル駆動方式を採用するにあたって、画素スイッチング回路としてトランスファーゲートを用いた場合でも、画素電極に対するHレベルの電圧書き込み時間とLレベルの電圧書き込み時間との差を短縮することのできる液晶装置、並びに当該液晶装置を備えた電子機器および投射型表示装置を提供すること。

【解決手段】デジタル駆動方式の液晶装置100において、画素スイッチング回路30は、Nチャネル型トランジスター30NとPチャネル型トランジスター30Pとのトランスファーゲートからなる。Nチャネル型トランジスター30Nのチャネル長L1、チャネル幅W1、Pチャネル型トランジスター30Pのチャネル長L2、Pチャネル型トランジスター30Pのチャネル幅W2は、下式

W1/L1 < W2/L2

を満たしている。

(もっと読む)

1 - 20 / 63

[ Back to top ]