Fターム[5C024HX23]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | A/D変換、D/A変換 (1,126)

Fターム[5C024HX23]の下位に属するFターム

リファレンス電圧調整 (46)

Fターム[5C024HX23]に分類される特許

1 - 20 / 1,080

撮像装置

ADコンバータおよびそれを用いた固体撮像装置

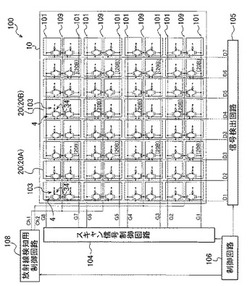

放射線検出器、放射線画像撮影装置、及び放射線画像撮影システム

【課題】、放射線画像の品質を維持したまま放射線の照射に関する検出を行うこができる、放射線検出器、放射線画像撮影装置、及び放射線画像撮影システムを提供する。

【解決手段】照射された放射線が変換された光に応じて電荷を発生するセンサ部103、センサ部103から読み出した電荷を信号配線3に出力するTFTスイッチ4、及び信号配線3と非接続の放射線検知用TFTスイッチ34を備えた画素20Aと、センサ部103、TFTスイッチ4、及び信号配線3と接続され、センサ部103から読み出した電荷を信号配線3に出力する放射線検知用TFTスイッチ34を備えた放射線検知用画素20Bと、を備える。放射線検知用TFTスイッチ34の制御端子は、放射線検知用走査配線109に接続されており、放射線検知用制御回路108から出力されたスキャン信号により、オン、オフが制御される。

(もっと読む)

A/D変換装置および固体撮像装置

【課題】電圧分解能を低下させることなく、高速化することができるA/D変換装置および固体撮像装置を提供する。

【解決手段】所定のアナログ・デジタル変換期間をTsとしたとき、(1−1/n)Ts(n:正の整数、n≧2)より短い第1のサンプリング期間と、(1/n)Tsの第2のサンプリング期間とを設定し、アナログ信号を出力して第1のサンプリングを行わせ、該アナログ信号をn倍に増幅し、デジタルオフセット信号で選択されたアナログオフセット信号を加えた増幅アナログ信号を出力して第2のサンプリングを行わせるA/D制御回路と、第1のサンプリング結果から第1のデジタル信号とデジタルオフセット信号とを生成し、第2のサンプリング結果から第2のデジタル信号を生成し、デジタルオフセット信号と第2のデジタル信号とに基づいて、期間Tsに対応した第3のデジタル信号を生成して出力するデジタル生成回路と、を備える。

(もっと読む)

AD変換回路および撮像装置

【課題】エンコードエラーの発生を抑圧することができるAD変換回路および撮像装置を提供する。

【解決手段】VCO100aの出力信号CK0〜CK8のうち出力信号CK7が上位計数部101のカウントクロックとなる。演算部106は、出力信号CK7を基準として定義される出力信号CK0〜CK8の状態(状態0〜状態7)を検出するため、各出力信号の論理状態の変化位置を検出し、検出された変化位置に基づいて下位計数信号を生成する。演算部106がこの変化位置を検出する際の手順では、立下りエッジが略同時になる出力信号CK0と出力信号CK7の論理状態の比較は行われない。このため、エンコードエラーの発生を抑圧することができる。

(もっと読む)

撮像装置及び電子機器

【課題】 静止画モード時にA/D変換時のセトリング期間を確保でき、画像信号の劣化を抑制できる撮像装置及び電子機器を提供する。

【解決手段】 撮像装置は、入射光を信号電荷に変換する光電変換部を有する複数の画素部と、前記信号電荷を蓄積し、信号電圧に変換するフローティングディフュージョン部と、前記信号電圧をデジタル信号に変換するアナログ・デジタル変換部と、リセットパルスが入力されることで、前記フローティングディフュージョン部に蓄積された信号電荷を破棄するリセット部と、前記画素部の信号電荷をそれぞれ信号電圧に変換する第1モードの場合、第1のLowレベルを有する第1のリセットパルスを生成し、前記複数の画素の信号電荷を加算して前記信号電圧に変換する第2モードの場合、前記第1のLowレベルより低い第2のLowレベルを有する第2のリセットパルスを生成して、前記リセット部に供給するリセットパルス生成部とを備える。

(もっと読む)

固体撮像装置、固体撮像装置の制御方法、および撮像装置

【課題】複数枚のチップを接続した構成の固体撮像装置において、それぞれのチップの大きさの差を少なくすることによって、固体撮像装置のチップ面積(実装面積)の縮小化と、コストの削減を図ることができる固体撮像装置、固体撮像装置の制御方法、および撮像装置を提供する。

【解決手段】第1の基板と第2の基板とが接続部によって電気的に接続された固体撮像装置であって、第1の基板に配置された光電変換素子と、第2の基板に配置され、光電変換素子で発生した信号をアナログの読み出し信号として出力する読み出し回路とを具備する画素が複数配置された画素部と、読み出し信号に対して信号処理を行う信号処理回路とを備え、信号処理回路を構成する回路要素を区分基準に基づいて第1の基板側または第2の基板側に区分し、第1信号処理回路に区分された回路要素を第1の基板内に配置し、第2信号処理回路に区分された回路要素を第2の基板内に配置する。

(もっと読む)

固体撮像装置

【課題】画質の劣化を抑制しつつ、消費電力を低減することができる固体撮像装置を提供することを課題とする。

【解決手段】固体撮像装置は、光電変換した信号をソースフォロワ回路により出力する複数の画素(11)と、前記複数の画素に接続される出力線(3)と、前記出力線に電流を供給する電流源回路部(5)と、前記画素のリセット状態の前記出力線の信号をクランプ容量にクランプし、その後の前記画素の非リセット状態の前記出力線の信号を増幅する第1の増幅部(7)とを有し、前記電流源回路部は、前記クランプの終了時刻より前に、前記出力線に電流を供給しない状態から前記出力線に電流を供給する状態に変化することを特徴とする。

(もっと読む)

撮像装置及び撮像システム

【課題】 ダミー画素をAD変換するサンプリングタイミングと有効画素をAD変換するサンプリングタイミングのサンプリング時間差を小さくし、横引きノイズを軽減することを可能にした撮像装置を提供すること。

【解決手段】 第1のアナログ−デジタル変換手段がアナログ−デジタル変換を行っている期間中に、ダミー画素部から出力されるアナログ信号を複数回アナログ−デジタル変換する第2のアナログ−デジタル変換手段と、第2のアナログ−デジタル変換手段によって得られた複数のデータを記録する為の複数の記録手段と、第1のアナログ−デジタル変換が行われたタイミング応じて、複数の記録手段に記録された複数のデータのうちの1つを選択する選択手段と、第1のアナログ−デジタル変換手段から得られるデータと、選択手段によって選択されたデータを演算する第1の演算手段を有する事を特徴とする構成とした。

(もっと読む)

撮像装置

【課題】 CMOSセンサの横筋ノイズ除去のために水平ライン平均でのクランプ補正があるが、水平OB画素が十分に多くないと水平ラインクランプによる横引きノイズが無視できなくなる。経験的にOB画素は1ラインあたり64画素以上必要であるがCMOSセンサは多チャンネル出力が主流であるため、1ch当たりの水平OB画素を64画素以上確保することは読み出し速度及びデバイスサイズの観点から非常に困難である。

【解決手段】 OB領域の複数ラインの平均値を用いて有効画素をクランプするクランプ回路と、各水平ライン毎の平均値を演算して有効画素をクランプするクランプ回路と、OB領域を用いて横筋ノイズを検出する検出ブロックを有し、該検出ブロックで線キズが検出されたどうかで前記2種類のクランプ回路を切り替えることでライン平均クランプによる横引きノイズの影響を低減する。

(もっと読む)

AD変換回路および撮像装置

【課題】カウントクロックの周波数によらず、AD変換により得られるデジタルデータの分解能を向上させることができるAD変換回路および撮像装置を提供する。

【解決手段】ラッチ部108は、比較部109による比較処理の間、クロック生成部18からのクロック信号を通過させ、比較処理の終了に係るタイミングでクロック信号をラッチする。列カウント部103は、クロック生成部18からのクロック信号をカウントすることに加えて、ラッチ部108にラッチされたクロック信号の論理状態に基づいて生成された計数信号をカウントする。

(もっと読む)

固体撮像装置、撮像装置および撮像方法

【課題】ストリーキングを低減することができるようにする。

【解決手段】 入射された光に対応する画素読み出し信号を出力する複数の単位画素から出力された画素読み出し信号が信号線により伝達され、信号線に接続され、単位画素から画素読み出し信号を読み出すための読み出し電流を供給され、画素読み出し信号のレベルをディジタルデータに変換するための参照信号が生成され、信号線の電圧の振幅の変化を制限する閾値を参照信号のゲインに連動して切り替えて、信号線の電圧の振幅の変化が制限される。

(もっと読む)

固体撮像装置、固体撮像装置の制御方法、及び、固体撮像装置の制御プログラム

【課題】より適切な太陽黒点の補正を実現可能とする。

【解決手段】リセット期間とP相期間の間で、フローティングディフュージョンFDに接続されているリセットトランジスタTR2に印加するリセット信号のレベルを、リセットオン電圧とリセットオフ電圧の中間的なFDクリップ電圧とすることにより、フローティングディフュージョンFDに流入するブルーミングに起因する相関2重サンプリングの失敗を回避し、ADC回路が画素信号に対応した適切なデジタル信号を出力する。

(もっと読む)

固体撮像装置

【課題】CCD型の固体撮像装置において、水平方向の読み出しの際の転送動作による発熱を効率良く放熱し、且つ出力信号に含まれるノイズを低減する。

【解決手段】固体撮像装置2Aは、M×N個(M,Nは2以上の整数)の画素がM行N列に2次元配列されて成る撮像面12、及び、撮像面12に対して列方向の一端側に各列毎に配置されており各列から取り出される電荷の大きさに応じた電気信号をそれぞれ出力するN個の信号読出回路20を有するCCD型の固体撮像素子10と、信号読出回路20から各列毎に出力される電気信号をディジタル変換してシリアル信号として順次出力するC−MOS型の半導体素子50と、主面81a及び裏面81bを有する伝熱部材80と、裏面81b上に設けられた冷却ブロック84とを備え、半導体素子50と伝熱部材80の主面81aとが互いに接合されている。

(もっと読む)

撮像装置および撮像表示システム

【課題】撮像画像の高画質化を実現することが可能な撮像装置等を提供する。

【解決手段】撮像装置は、各々が光電変換素子を含む複数の画素を有する撮像部と、アンプを含んで構成されると共に、光電変換素子により得られた電荷をアンプを用いて画素から信号として読み出す読み出し動作と、画素内の電荷をリセットするための画素リセット動作と、アンプの動作をリセットするためのアンプリセット動作とがそれぞれ行われるように各画素を駆動する駆動部とを備えている。この駆動部は、画素リセット動作の終了タイミングおよびアンプリセット動作の終了タイミングのうちの少なくとも一方が所定の電源電位不安定化期間内に含まれないように、各画素の駆動を行う。

(もっと読む)

撮像装置

【課題】撮影環境に応じて相関多重サンプリング処理のサンプリング回数を可変すること。

【解決手段】温度センサ11は画素アレイ部51の温度を測定し、サンプリング回数決定部121は測定温度に反比例して温度サンプリング回数を設定する。出力レベル算出部21は前回のフレームで出力された画像信号が示す画像の明るさを算出し、この明るさに反比例して明るさサンプリング回数を設定してサンプリング回数決定部121へ出力する。そして、サンプリング回数決定部121は温度サンプリング回数と明るさサンプリング回数を比較し、温度サンプリング回数が明るさサンプリング回数以下であるとき、温度サンプリング回数をサンプリング回数Mに設定してカラムADCアレイ部53へ出力する。一方、温度サンプリング回数が明るさサンプリング回数より大きいとき、明るさサンプリング回数をサンプリング回数Mに設定してカラムADCアレイ部53へ出力する。

(もっと読む)

固体撮像装置

【課題】従来よりも高精度かつ高速の変換が可能なカラムADCを内蔵した固体撮像装置を提供する。

【解決手段】固体撮像装置200において、各変換部12は、対応の垂直読出線9を介して出力された各画素の信号を第1〜第N(Nは3以上の整数)の変換ステージを順に実行することによってデジタル値に変換する。第1〜第N−1の変換ステージでは、各変換部12は、画素の信号を保持する保持ノードND1の電圧を所定の電圧ステップずつ変化させながら参照電圧と比較することによって、デジタル値の最上位ビットを含む上位の複数ビットの値を決定する。第Nの変換ステージでは、各変換部12は、第N−1の変換ステージにおける電圧ステップの範囲またはそれを超える範囲で、保持ノードND1の電圧を連続的に変化させながら参照電圧と比較することによって、残りの最下位ビットまでの値を決定する。

(もっと読む)

撮像装置および撮像装置の制御方法

【課題】構成を複雑にすることなく、グローバルリセットシャッタ方式とローリングシャッタ方式との双方で本撮影を適切に行うことができる撮像装置および撮像装置の制御方法を提供する。

【解決手段】CMOSセンサの画素ラインごとに電荷リセット動作を行うローリングシャッタ方式により本撮影を行う場合に、CMOSセンサの全画素同時に電荷リセット動作を行うグローバルリセットシャッタ方式により本撮影を行う場合よりも、CMOSセンサから画像信号を読み出す速度を速くする。

(もっと読む)

固体撮像装置

【課題】消費電流を低減することができる固体撮像装置を提供する。

【解決手段】画素信号のレベルに応じた論理状態の信号を出力する複数の遅延ユニットのいずれかの出力信号の論理状態をラッチするラッチ回路L_7において、複数の遅延ユニットのいずれかの出力信号が入力端子Dに入力される。NAND回路NAND1およびINV回路INV2は、画素信号のレベルに応じた制御信号が出力される制御信号出力タイミングまでは停止しており、制御信号出力タイミングの後に動作する。スイッチ回路SW1,SW2は、制御信号出力タイミングまでは複数の遅延ユニットのいずれかの出力信号を、信号線LN2を介して出力端子Mから出力し、制御信号出力タイミングから所定時間が経過した後のラッチタイミングで複数の遅延ユニットのいずれかの出力信号の論理状態をNAND回路NAND1およびINV回路INV2がラッチするように接続の切替を行う。

(もっと読む)

固体撮像装置及び撮像システム

【課題】カウント値の伝搬遅延が異なることに起因する列毎の固定のノイズ成分を低減することができる固体撮像装置を提供することを課題とする。

【解決手段】行列状に配列され、光電変換により信号を生成する複数の画素と、行列状に配列された複数の画素の各列に設けられ、複数の画素の信号を列毎に読み出す複数の読み出し回路と、複数の読み出し回路から出力される信号と時間的にレベルが変化する参照信号とを比較する複数の比較部と、参照信号のレベルが変化を開始してからの時間をカウントするカウンタと、カウンタのカウント値をバッファリングする第1のバッファ(9n)と、カウンタのカウント値をバッファリングする第2のバッファ(9s)と、複数の比較部に接続され、複数の読み出し回路から出力される信号と参照信号との大小関係が逆転したときのカウンタのカウント値を記憶する複数の記憶手段(6)とを有する。

(もっと読む)

1 - 20 / 1,080

[ Back to top ]