Fターム[5C080DD09]の内容

陰極線管以外の表示装置の制御 (251,852) | 目的、効果 (44,953) | 誤動作防止 (2,465)

Fターム[5C080DD09]の下位に属するFターム

クロストーク防止 (911)

Fターム[5C080DD09]に分類される特許

101 - 120 / 1,554

駆動装置及び駆動装置を用いた電子機器

【課題】基板に実装された駆動装置から出力されるデマルチ制御信号の波形の鈍りを、基板に形成された配線上で、従来よりも軽減する。

【解決手段】第1の信号を出力する第1の端子と、第2の信号を出力する第2の端子と、第3の信号を出力する第3の端子と、を含み、前記第1の信号はアナログ信号であり、前記第2の信号及び前記第3の信号の各々は、第1のタイミング信号を元に生成され、第1の期間における前記第1の信号の値を抽出するために用いられる信号であることを特徴とする駆動装置を提供する。

(もっと読む)

ディスプレイ駆動回路、及びその動作方法

【課題】ビットエラー率(BER)をテストするための別のテスト装置及びテスト環境が必要としないディスプレイ駆動回路を提供する。

【解決手段】ディスプレイパネルの複数のソースラインを駆動するソースドライバーと、前記ソースドライバーに映像データを伝送し、前記伝送された映像データが前記ディスプレイパネルを通じてディスプレイされるように前記ソースドライバーを制御するタイミングコントローラと、を含み、前記タイミングコントローラはビットエラー率をテストするための制御信号とテストパターンを前記ソースドライバーに伝送し、前記ソースドライバーは前記伝送された制御信号に応答して前記伝送されたテストパターンのビットエラー率をテストすることを特徴とする。

(もっと読む)

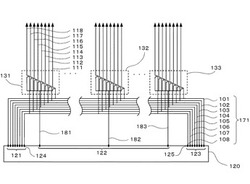

半導体装置

【課題】入力データの転送周波数よりも低い動作周波数で内部を動作させることで、表示パネルの画素数の増加に対応することができる信号の駆動が可能な半導体装置を提供する。

【解決手段】表示パネルに信号を駆動する半導体装置であって、前記半導体装置の第1の辺において中心から一方側に設けられた第1の端子から出力される信号の元となるデータを伝搬させる第1データバスと、前記第1の辺において中心から他の一方側に設けられた第2の端子から出力される信号の元となるデータを伝搬させる第2データバスと、前記第1データバスに接続された第1の回路と、前記第2データバスに接続された第2の回路と、データ分割部とを含む。

(もっと読む)

表示制御装置、表示制御方法、および表示制御プログラム

【課題】コマ落ちの発生を容易に抑制することが可能な表示制御装置を提供する。

【解決手段】この表示制御装置1は、フレームバッファ6のA面とB面から画素データを順次読み出し、読み出した画素データを画像信号に変換するとともに、画像表示装置11の画面の複数のラインのうちの表示中のラインの番号を示すライン表示信号を出力する一方、画素データの読出が行なわれているメモリ領域(A面またはB面)に書き込まれた画素データのうちの、ライン表示信号によって示される番号よりも小さな番号のラインに対応する読出済みの画素データを新たな画素データに順次書き換える。したがって、A面またはB面で画素データの読出と書込を並列に行なうことができ、画素データの書込性能の向上を図ることができる。

(もっと読む)

電子機器

【課題】原画像を、反転させるなど姿勢変更して表示する場合にティアリングの発生を防止することができる電子機器を提供する。

【解決手段】携帯電話機1は、GRAM41から表示画像データを読み出してLCD11に表示する表示モジュール25と、表示モジュール25と外部バス27で結合された制御モジュール26とを備え、CPU64は、LCD11に原画像を基準姿勢以外の姿勢で表示させるモードが選択されると、選択されたモードに応じ、第1バッファ62から原画像データを、原画像が選択されたモードに対応する姿勢に変換されるよう各画素間の位置関係を入れ替えながら、外部バス27より高速な内部バス65を用いて第2バッファ63に転送し、第2バッファ63に保持された表示画像データを外部バス27を用いて表示モジュール25のGRAM41に転送する。

(もっと読む)

画像投影装置、メモリ制御装置、レーザープロジェクタ、メモリアクセス方法

【課題】斜め投射時に発生する投影画像の歪みを、実用的な制御負荷にて補正可能な画像投影装置を提供すること。

【解決手段】画像データを記憶するフレームメモリ58と、レーザー発振器60と、レーザー光を反射する1つ以上の反射光学素子533と、レーザー光の包絡線が所定形状となるよう反射光学素子を振動させる偏向方向可変手段53と、反射光学素子の角度からレーザー光の照射位置を三角関数を用いずに求める多項式の係数情報が記憶された係数情報記憶手段63と、係数情報に演算を施して求めた係数及び角度を多項式に適用することで、レーザー光の照射位置を演算する照射位置演算手段62と、照射位置に対応するフレームメモリのアドレスを演算するアドレス演算手段64と、アドレスの画素情報を読み出すメモリ制御手段100と、画素情報に応じた輝度でレーザー光を照射するレーザー駆動手段59と、を有する画像投影装置200を提供する。

(もっと読む)

画像処理装置、画像処理方法

【課題】 メモリの小容量化と圧縮誤差の低下の両立を可能にする画像処理装置を提供する

【解決手段】 出力画像データ生成手段11は、特定参照データ及び処理前画像データに基づいて処理済画像データを生成する。参照データ生成手段5は、2以上の連続したフレームで構成される1タームに同一の処理を繰り返し実行する。対象フレームがターム内の先頭である場合、データ伸張手段15が生成した復元参照データを特定参照データとして出力する。対象フレームがターム内の2番目以後である場合、データ伸張手段15が生成した復元参照データと対象フレームの処理前画像データとに基づいて模擬特定参照データを生成し、これを特定参照データとして出力する。更に対象フレームがターム内の最終である場合には、上記動作に加えて特定参照データと当該対象フレームの処理前画像データとに基づいて参照データを生成してデータ圧縮手段13に出力して圧縮させる。

(もっと読む)

ディスプレイ駆動回路

【課題】ラッチアップ防止部を備えてラッチアップの発生を防止するディスプレイ駆動回路を提供する。

【解決手段】外部から同じ大きさの入力電圧を受けて互いに異なる大きさの電圧をそれぞれ生成する第1〜第3電圧生成部、及び前記第2電圧生成部と連結され、前記第2電圧生成部から出力される電圧の中で下位電圧を受けて既設定の時間の間に接地させるラッチアップ防止部とを含み、前記第2電圧生成部から出力される第2駆動電圧を接地連結された多数のスイッチング手段を含むラッチアップ防止部と連結して、既設定の時間の間に第2駆動電圧を接地させることで、ラッチアップの発生を防止し、駆動回路の大きさを減らす。

(もっと読む)

半導体装置および電気装置

【課題】薄くて軽く、薄厚化および狭額縁化などによる小型化や軽量化、さらには高堅牢性(高信頼性)を実現することのできる半導体装置および電気装置を提供する。

半導体装置および電気装置を提供する。

【解決手段】本発明の電気光学装置100は、フレキシブル性を有する第1基板30と、第1基板30上に形成される複数の画素電極35と、第1基板30内に埋め込まれた少なくとも1つのドライバIC89と、ドライバIC89と画素電極35とが接続配線22を介して接続されていることを特徴とする。

(もっと読む)

発光装置および電子機器

【課題】データ信号を伝送する信号線の寄生容量を低減する。

【解決手段】発光装置100は、複数の発光素子Pを含む有効領域Aと、各発光素子Pに供給されるデータ信号を伝送する複数の信号バス配線30と、信号バス配線30から分岐して各発光素子Pにデータ信号を供給するための信号供給線301と、各発光素子Pに電源電圧を供給するための電源配線20とを有する。信号バス配線30は有効領域Aの一辺と同じ方向に配設される。電源配線20は主電源配線20Aと副電源配線20Bとを有し、主電源配線20Aは信号供給線301を挟んで有効領域Aの反対側に配設される。これにより、信号供給線301と主電源配線20Aとは交差しない。

(もっと読む)

液晶表示装置の駆動回路及び液晶表示装置のフリッカ調整システム

【課題】表示装置の温度を正確に感知するセンサを備えた液晶表示装置の駆動回路及び液晶表示装置のフリッカ調整システムを提供する。

【解決手段】液晶表示装置の駆動回路は、第1電圧Vrefを生成するDVR750と、前記DVRに接続されており、第2電圧Vcを生成する温度センサ部50と、前記温度センサ部に接続されており、前記第2電圧と前記液晶表示板アセンブリからの第3電圧Vcomfとに基づいて共通電圧Vcomを生成する共通電圧生成部700とを含む。

(もっと読む)

マルチディスプレイシステム

【課題】共通の制御部によって複数のディスプレイの電源を起動するタイミングを制御することなく、電源起動時に発生する突入電流によりブレーカーやヒューズが切れるトラブルを回避できることができるマルチディスプレイシステムを提供する。

【解決手段】PCおよび複数個のディスプレイは、デイジーチェーンで接続される。PCは、バックライト11に電力を供給する待ち時間を表わす数値を含むコマンドを接続されているディスプレイへ送信し、各ディスプレイのスケーラ1は、第1のポートを通じて受信したコマンドに含まれる待ち時間を表わす数値に従って、バックライト用電源12からバックライト11に電力を供給させるとともに、受信したコマンドに含まれる待ち時間を表わす数値を増加して修正したコマンドを第2のポートを通じて次のディスプレイへ送信する。

(もっと読む)

表示装置

【課題】 指先等の接触位置の検出感度を向上させ、動作正確性の高い表示装置を提供する。

【解決手段】 マトリクス状に配置された表示画素PXを含む表示部DYPと、表示画素PXに配置された画素電極PEと、画素電極PEが配列する行に沿って延びる走査線GLおよびセンサ用電極CsLと、画素電極PEが配列する列に沿って延びる信号線SLと、アレイ基板10と、複数の画素電極PEと対向するように配置された対向電極CEを備えた対向基板20と、センサ用電極CsLおよび信号線SLを駆動する駆動回路XD、YDと、駆動回路XD、YDへセンサ用信号を出力するとともに、センサ用電極CsLおよび信号線SLからの信号を受信してセンサデータを出力するセンサ用回路30と、を備え、表示部DYPの周囲の領域において、信号線SLが延びる方向に並ぶ複数のセンサ用電極が電気的に接続されている表示装置。

(もっと読む)

プラズマディスプレイパネルの駆動方法およびプラズマディスプレイ装置

【課題】強制初期化動作を行わずに安定した書込み動作を行ってプラズマディスプレイパネルに表示される黒の輝度を抑えるとともに、黒の次に低い階調の輝度を低下させ、表示画像が黒の画像から通常の画像に切り換わるときに書込み放電を安定に発生させる。

【解決手段】1つのフィールドは、維持期間に輝度重みに応じた数の維持パルスを発生して表示電極対に印加する第1種サブフィールドと、維持期間に維持パルスを発生せず上り傾斜波形電圧および下り傾斜波形電圧を発生して走査電極に印加する最も輝度重みの小さい第2種サブフィールドとを含み、プラズマディスプレイ装置の周囲の明るさを検出し、検出された明るさに応じた点灯率で、最も輝度重みが小さいサブフィールドの強制点灯を行う。

(もっと読む)

液晶表示装置

【課題】消費電力を抑えつつ、ソースライン電位を安定化することができる液晶表示装置を提供する。

【解決手段】電位設定部2は、制御信号POL2がハイレベルの時には、1行分のn個の画素の画素値に応じた各電位を電位出力端D1〜Dnから出力し、電位出力端Dn+1をハイインピーダンス状態にする。このとき、スイッチ12は、ソースラインSn+1をVp設定用配線5またはVn設定用配線6に接続させる。また、電位設定部2は、POL2がローレベルの時には、1行分のn個の画素の画素値に応じた各電位を電位出力端D2〜Dn+1から出力し、電位出力端D1をハイインピーダンス状態にする。このとき、スイッチ11は、ソースラインS1をVp設定用配線5またはVn設定用配線6に接続させる。

(もっと読む)

立体映像表示装置

【課題】1台の液晶プロジェクタで立体映像を表示する場合のクロストークを低減させることができるような立体映像表示装置を提供する。

【解決手段】信号処理部101は、入力される3D映像信号から左目用信号、右目用信号が時間的に交互に並べ替えられた信号に変換する。液晶表示素子の駆動装置102は、ステップビットパルスにより全サブフレームを構成し、駆動階調が1のとき最後のサブフレームが駆動状態となり、駆動階調が1増加する毎に駆動状態となるサブフレームが1個ずつ既に駆動状態となっているサブフレームの前に向かって増加していく駆動階調テーブルによりサブフレームデータを作成するサブフレームデータ作成部26を有する。液晶表示素子6は、駆動装置で駆動される。照明光学系1は液晶表示素子に照明光を入射させる。投射レンズ11は、液晶表示素子から射出された変調光を投射する。

(もっと読む)

LCDバックライトのためのデュアル機能光ガイド

【課題】ディスプレイに表示される情報が広域な周辺光のレベルの下においてより容易に読むことできる携帯コンピュータ機器を提供する。

【解決手段】携帯コンピュータ機器は、外側表面、イベント通知子(162)を有するハウジング、ハウジング内に配置される表示デバイスおよび光コントローラ含む。イベント通知子は、イベント通知ランプ(166)、およびイベント通知ランプと外側表面との間に光を伝えるための外側表面において終端する光コンジット(168)を含む。表示デバイスは、その上に示される情報の改良された視覚化のための照明手段を含む。光コントローラは、イベント通知子および照明手段に結合され、光コンジットを介してハウジングの外の周辺光の強度を決定するように、および決定された周辺光の強度に従って照明手段によって放たれる光の強度を調節するように、構成される。

(もっと読む)

画素回路、電気光学装置及び電子機器

【課題】ラッチ回路の誤動作発生等を抑止しながら画素を駆動できる画素回路等の提供。

【解決手段】画素回路は第1、第2のラッチ回路11、12を含む。第1のラッチ回路11は、並列接続されたP型トランジスターTP1及びN型トランジスターTN1により構成される第1のトランスファーゲートTG1と、直列接続されたP型トランジスターTP2、TP3、N型トランジスターTN3、TN2により構成される帰還用第1のクロックドインバーター回路CIV1と、第1のインバーター回路IV1を含む。第2のラッチ回路12は、並列接続されたP型トランジスターTP5及びN型トランジスターTN5により構成される第2のトランスファーゲートTG2と、直列接続されたP型トランジスターTP6、TP7、N型トランジスターTN7、TN6により構成される帰還用第2のクロックドインバーター回路CIV2と、第2のインバーター回路IV2を含む。

(もっと読む)

画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置

【課題】超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な画素回路を提供する。

【解決手段】電気光学素子と、第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、第2スイッチ素子の制御端子に一方の電極端子が接続され、第2スイッチ素子の他方の電極端子に他方の電極端子が接続され、第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する容量素子と、を備え、電気光学素子に保持された画像データに対応する電圧レベルが、第1スイッチ素子をオンすることにより、第2スイッチ素子を介して容量素子にサンプリングされることを特徴とする、画素回路が提供される。

(もっと読む)

表示装置

【課題】 保持回路110へのデータの誤書き込みを防止すると共に、低消費電力化及び表示画素の高集積化を図る。

【解決手段】 表示画素にデジタル映像データを保持するための保持回路を備えた表示装置において、データ書き込み時には、保持回路110に供給される電源電圧をデータ保持に必要な最小電圧に設定し、書き込み終了後に、昇圧回路95により保持回路110に供給される電源電圧を昇圧する。保持回路110はゲート信号線51から入力される信号に応じて、ドレイン信号線61からのデジタル映像信号が書き込まれると共に該デジタル映像信号を保持する。そして、保持回路110に保持された信号に応じて表示が行われる。

(もっと読む)

101 - 120 / 1,554

[ Back to top ]