Fターム[5C080DD26]の内容

陰極線管以外の表示装置の制御 (251,852) | 目的、効果 (44,953) | 省エネ、低発熱化 (4,862)

Fターム[5C080DD26]に分類される特許

41 - 60 / 4,862

情報表示装置

【課題】複数の情報表示パネルが着脱可能に構成されるとともに、所望の情報表示パネルに所定情報を表示させる際の手間を削減し、利便性に優れた情報表示装置を提供する。

【解決手段】情報表示装置は、複数の情報表示パネルと、駆動装置とを備える。駆動装置は、情報表示パネルを着脱する着脱機構を備え、複数の情報表示パネルの各々は、所定信号を入力する入力電極部と、所定信号を出力する出力電極部と、表示領域に表示される所定画像を制御する制御回路とを備える。所定信号には、画像信号と、複数の情報表示パネルの各々の順番を検出するための検出信号とが含まれており、制御回路は、予め定められた特定情報を記憶する記憶部と、検出信号と特定情報とに基づいて所定画像を表示すべきか否かを判定する表示制御部と、検出信号によって検出される順番を一つ変更する所定の変更処理を行って、出力電極部から検出信号を出力する出力制御部とを備える。

(もっと読む)

画像処理装置、投影型表示装置および画像処理装置の消費電力低減方法

【課題】CMOSタイプの画像処理回路を用いた画像処理装置において、装置の停止時に、画像処理回路に接続されたCPUから回り込んで、画像処理回路の出力ラインから流れ出る電流による消費電力を低減する。

【解決手段】 画像処理装置の停止時に、CPUから画像処理回路にリセット信号を出力して画像処理回路の出力ラインをロウレベルまたはハイインピーダンス状態とし、画像処理回路に供給するクロック信号を停止する。更に、画像処理回路への電源供給は継続しつつ、表示デバイスとその駆動回路への電源供給は停止する。この結果、CPUからの回り込みによる電力消費は抑制される。

(もっと読む)

電子装置

【課題】電子装置において、新規の駆動方法および回路を用いることにより、デューテ

ィー比(発光期間と非発光期間との比)の低下に起因した、輝度不足を始めとした問題点

を改善することを目的とする。

【解決手段】 1ゲート信号線選択期間内に、異なる複数段の画素に信号を書き込む点に

特徴がある。それにより、ある段の画素において、信号を入力してから次の信号を入力す

るまでの時間を、画素への書き込み時間を確保した上である程度任意に設定することによ

り、サステイン(点灯)期間を任意に設定し、高デューティー比を実現する。

(もっと読む)

投影装置、投影方法及びプログラム

【課題】入力される画像の階調値における明るさを忠実に再現した光像を形成して投影する。

【解決手段】光源となるLEDアレイ17及びこれを駆動するRドライバ22,Gドライバ23及びBドライバ24と、光源からの光を用いて光像を形成し、形成した光像を投影する投影系13〜16,20,21と、投影系13〜16,20,21で表現し得る全階調値に対する明るさを測定する照度センサ26と、その測定結果に基づき、得られた明るさの順序に従って全階調値を記憶する階調記憶部15aと、階調記憶部15aで記憶される全階調値の記憶順序に従い、画像の階調値を書換えて投影系13〜16,20,21で投影させる投影画像処理部15とを備える。

(もっと読む)

負荷駆動装置、画像形成装置、負荷駆動方法、およびプログラム

【課題】共振を利用し、かつ、容量性負荷の両端に逆位相の電圧パルスを印加可能とすることにより、消費電力を低減できる負荷駆動装置、画像形成装置、負荷駆動方法およびプログラムを提供する。

【解決手段】負荷駆動装置3は、第1電極および第2電極で構成され、1〜4番目まで順番に接続された容量性負荷51〜54を備える。この負荷容量51〜54をそれぞれ隣接する負荷容量間で放電、充電を繰り替えるようにSW駆動部30はスイッチを駆動して、逆パルス電圧を印加する。

(もっと読む)

頭部装着型表示装置、プログラム及び画像処理システム

【課題】 表示バッファの表示レイアウトを変更することができ、頭部姿勢情報に応じた画像を表示することができる頭部装着型表示装置、プログラム及び画像処理システム等の提供。

【解決手段】 頭部装着型表示装置100は、画像データと画像の表示レイアウトデータとを情報端末から受信する通信部110と、表示レイアウトデータにより設定された画像記憶領域に画像データを記憶する表示バッファ120と、表示バッファ120の画像記憶領域に表示領域を設定する処理部130と、設定された表示領域の画像を表示画像として表示する表示部140と、を含む。そして、処理部130は、頭部装着型センサから取得される頭部姿勢情報に基づいて、画像記憶領域に表示領域を設定する。

(もっと読む)

表示装置

【課題】限られた画素サイズの中でブートストラップ比を大きく設定することで、消費電力を増やすことなく、画質の向上を図る。

【解決手段】第1,第2,第3電極24A,24B,24Cによって第1,第2容量24−1,24−2を形成し、これら第1,第2容量24−1,24−2を電気的に並列に接続することによって保持容量24を形成する。そして、第1電極24Aと第3電極24Cとの間において、絶縁平坦化膜203を除去して第2容量24−2の容量値を大きくし、保持容量24の容量値Csを大きくすることで、限られた画素サイズの中でブートストラップ比を大きく設定する。

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供することを課題の一とする。また、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。また、暗所でも長時間の利用が可能な、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。

【解決手段】高純度化された酸化物半導体を用いた薄膜トランジスタで回路を構成し、画素が一定の状態(映像信号が書き込まれた状態)を保持することを可能とする。その結果、静止画を表示する場合にも安定した動作が容易になる。また、駆動回路の動作間隔を長くできるため、表示装置の消費電力を低減できる。また、自発光型の表示装置の画素部に蓄光材料を適用し、発光素子の光を蓄えれば、暗所でも長時間の利用が可能になる。

(もっと読む)

液晶表示装置

【課題】バックライトの点灯制御を高速化し、遅延の発生を防止することにより、バックライトの点灯制御と液晶パネルの駆動制御との間の同期をとるためのフレームメモリを不要とし、装置の簡略化および低コスト化を実現するとともに、映像の明るさを効果的に高める。

【解決手段】映像を表示する液晶表示装置に設けられたバックライト制御部24が、映像の各領域をそれぞれ照明するバックライトの各領域の第1の輝度を、映像の各領域の輝度の情報に基づいてバックライトの領域ごとに決定し、各領域の第1の輝度に、映像のジャンルに応じて設定された一定倍率を一律に乗算してバックライトの各領域の第2の輝度を設定し、各領域の第2の輝度を用いてバックライトの各領域の点灯を、バックライトの領域ごとに制御する。

(もっと読む)

表示装置及びその制御方法

【課題】小規模な外部周辺回路及び配線数の少ない低損失な画素回路を有し、簡略化された製造工程による表示装置及びその制御方法を提供する。

【解決手段】表示装置1が有する発光画素は、有機EL素子14と、ドレインが電源線PSに接続された電流駆動トランジスタ21と、電流駆動トランジスタ21のVgsを保持するコンデンサ22と、コンデンサ22と電源線PSとを導通させるスイッチトランジスタ23と、コンデンサ22とデータ線DTとを導通させるスイッチトランジスタ24と、電流駆動トランジスタ21により駆動される電流を有機EL素子14へ流すための電流径路を導通及び遮断する電流スイッチトランジスタ11と、電流スイッチトランジスタ11のVgsを保持するコンデンサ12と、電流スイッチトランジスタ11のゲートとデータ線DTとを導通させる選択トランジスタ13とを備える。

(もっと読む)

表示装置およびその駆動方法

【課題】可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、画素回路の簡略化による高精細化と高信頼性化を両立させる。

【解決手段】画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、前記第2制御電極には第2制御電圧が入力され、前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有する。

(もっと読む)

ディスプレイドライバーとイメージデータ処理装置の動作方法

【課題】ディスプレイドライバーを提供する。

【解決手段】入力データを圧縮して第1データDATA1を出力する圧縮器と、いずれのデータを出力させるかに関する第1選択信号に応答して、入力データまたは第1データをメモリに伝送する第1選択回路と、メモリから出力された第2データを圧縮解除して第3データを出力する圧縮解除器と、第3データを処理して生成された第4データをディスプレイに伝送するためのディスプレイインターフェースと、を含むディスプレイドライバー。

(もっと読む)

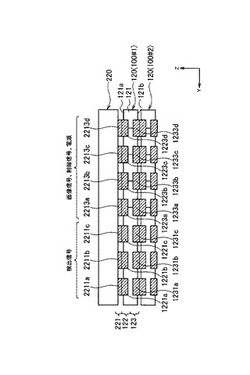

マルチディスプレイシステム

【課題】 視聴者に違和感を与えることなく、消費電力を低減することができるマルチディスプレイシステムを提供する。

【解決手段】 マルチディスプレイシステム1は、複数の光源31が設けられ、かつ画像を表示可能な表示画面を有する表示部13をそれぞれ備える複数の画像表示装置10と、配列情報61a、姿勢情報61b、境界位置情報61c、傾斜量情報61dおよび目標消費電力情報61eが記憶される記憶部15と、各情報61a〜61eに基づいて、マルチディスプレイ画面Dの周縁領域Sbに対応して配置される光源31の輝度が、マルチディスプレイ画面Dの中央領域Saに対応して配置される光源31の輝度よりも低くなり、かつ、各光源31の消費電力の合計が目標値以下となるように、光源31毎に、輝度を調整するための制御情報を生成する輝度傾斜演算部52と、該制御情報に基づいて、各光源31を駆動するバックライト駆動部42とを備える。

(もっと読む)

表示装置及びその制御方法

【課題】小規模な外部周辺回路及び配線数の少ない低損失な画素回路を有し、簡略化された製造工程による表示装置及びその制御方法を提供する。

【解決手段】表示装置1が有する発光画素は、有機EL素子14と、ドレインが定電流スイッチ部を介して電源線PSに接続された電流駆動トランジスタ21と、電流駆動トランジスタ21のVgsを保持するコンデンサ22と、コンデンサ22とデータ線DTとを導通させるスイッチトランジスタ23と、コンデンサ22と走査線SCNとを導通させるスイッチトランジスタ24と、電流駆動トランジスタ21により駆動される電流を有機EL素子14へ流すための電流径路を導通及び遮断する電流スイッチトランジスタ11と、電流スイッチトランジスタ11のVgsを保持するコンデンサ12と、電流スイッチトランジスタ11のゲートとデータ線DTとを導通させる選択トランジスタ13とを備える。

(もっと読む)

表示装置及びその駆動方法

【課題】行方向の制御配線の数を低減し、高精細化した場合においても消費電力の増加を抑制できる表示装置及びその駆動方法を提供する。

【解決手段】本発明の表示装置1の発光画素10A及び10Bは、それぞれ、有機EL素子15A及び15Bと、コンデンサ13A及び13Bと、駆動トランジスタ14A及び14Bと、信号線16とコンデンサ13A及び13Bとを導通させるスイッチトランジスタ12A及び12Bと、駆動トランジスタ14A及び14Bのソースとコンデンサ13A及び13Bとを導通させるスイッチトランジスタ19A及び19Bと、スイッチトランジスタ12A及び12Bのゲートと走査線17とを導通させるスイッチトランジスタ23A及び23Bとを備え、スイッチトランジスタ19A及び23Bのゲートは制御線18Aに接続され、スイッチトランジスタ23A及び19Bのゲートは制御線18Bに接続されている。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

電位生成回路および液晶表示装置

【課題】本発明は、簡単な回路構成で消費電力を低減することが可能な電位生成回路および液晶表示装置を提供することを目的とする。

【解決手段】本発明による電位生成回路は、容量性負荷に印加するコモン電位を生成する電位生成回路であって、所定の設定電位が正入力に入力され出力電位が負入力に負帰還される差動アンプ2と、差動アンプ2からの出力を増幅し、コモン電位を出力する電流増幅部3と、一端が基準電位に接続された電荷回収容量5と、電荷回収容量5の他端とコモン電位との間に接続された逆並列ダイオード4とを備えることを特徴とする。

(もっと読む)

電気光学装置の駆動方法、制御装置、表示装置および電子機器

【課題】2T1C方式において、データ信号の電圧のレンジを1T1C方式より狭くして消費電力を低減すること。

【解決手段】本発明の電気光学装置の駆動方法は、駆動トランジスターのオンオフにかかわらず電気光学素子の光学状態を異ならせない電圧にするステップと、画素トランジスターをオンにする電圧Gonを走査線に印加することにより、駆動トランジスターのオンオフを指定するデータ電圧を信号線から駆動トランジスターのゲートに印加するステップと、画素トランジスターをオフにする電圧Goffを走査線に印加することにより、駆動トランジスターのゲートに印加されたデータ電圧をフィードスルー電圧Vftだけ低い電圧にするステップと、素子駆動電源を電圧Vep0よりVepだけ高く、またはVepだけ低くした電圧に制御するステップとを有し、各電圧、容量が所定の条件を満たしていることを特徴とする。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

シフトレジスタ回路

【課題】トランジスタのしきい値電圧の制御を行いながら、ゲート電極の電位は変動させず、バックゲート電極の電位のみを変動させることで、入力信号に応じた信号を出力することが可能な論理回路を有するシフトレジスタ回路を提供する。

【解決手段】同じ導電型の第1のトランジスタ及び第2のトランジスタを有する論理回路、を含むシフトレジスタ回路において、第1のトランジスタの第1のゲート電極を、第1のトランジスタのソース電極またはドレイン電極に接続し、第1のトランジスタの第2のゲート電極に入力信号を供給し、第2のトランジスタのゲート電極にクロック信号を供給し、第1のゲート電極と、ゲート電極とは、同じ層とする。

(もっと読む)

41 - 60 / 4,862

[ Back to top ]