Fターム[5C094AA21]の内容

要素組合せによる可変情報用表示装置 (81,180) | 目的 (21,550) | 電気的特性向上 (2,053)

Fターム[5C094AA21]の下位に属するFターム

低消費電力 (483)

電圧特性向上 (148)

電流特性向上(電流漏れ防止等) (199)

Fターム[5C094AA21]に分類される特許

1 - 20 / 1,223

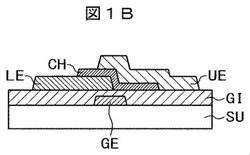

酸化物半導体装置およびその製造方法

【課題】

短いチャネル長の酸化物半導体装置およびそれを低コストで実現することのできる製造方法を提供する。

【解決手段】

酸化物半導体装置において、チャネルとなる酸化物半導体層CHと、第1方向に、酸化物半導体層CHを介して延伸する第1の電極層(ソース又はドレイン)LEおよび第2の電極層(ドレイン又はソース)UEと、第1方向と交差する第2方向に延伸し、酸化物半導体層CHと基板SUに垂直な方向においてゲート絶縁層GIを介して重なるゲート電極層GEとを有し、酸化物半導体層CHの膜厚がそのチャネル長となる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

電気光学装置および電子機器

【課題】データ信号の振幅を圧縮しつつ、データ線の狭ピッチ化を可能とする。

【解決手段】一端がデータ線14に接続された保持容量44と、データ線14の各々の電位をそれぞれ保持する保持容量50と、階調レベルに応じた電位のデータ信号Vd(j)を一旦保持し、保持したデータ信号が所定のタイミングで保持容量44の他端に供給される保持容量41とを備え、これらは半導体基板に形成され、保持容量41は、電気的に並列に接続される第1容量411と第2容量412とを備え、半導体基板150と垂直方向から見たとき、第1容量411と第2容量412とは重なるように形成される。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】酸化物半導体層、及びチャネル保護層を覆うようにソース電極層、及びドレイン電極層となる導電膜を形成した後、酸化物半導体層、及びチャネル保護層と重畳する領域の導電膜を化学的機械研磨処理により除去する。ソース電極層、及びドレイン電極層となる導電膜の一部を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、チャネル保護層を有することにより、導電膜の化学的機械研磨処理時に当該酸化物半導体層に与える損傷、または膜減りを低減できる。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気的特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】チャネル形成領域、及びチャネル形成領域を挟む低抵抗領域を含む酸化物半導体膜、ゲート絶縁膜、及び上面及び側面を覆う酸化アルミニウム膜を含む絶縁膜が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び酸化アルミニウム膜を含む絶縁膜の上面及び側面の一部に接して設けられる。

(もっと読む)

発光装置

【課題】発光素子へ微少な電流を供給する低階調表示を行う場合、駆動用トランジスタの

ゲート・ソース間電圧が小さいため、そのしきい値電圧のバラツキが顕著となってしまう

。

【解決手段】低階調表示であっても、駆動用トランジスタのしきい値電圧のバラツキの影

響が低減された半導体装置であって、低階調表示で高階調表示よりも駆動用トランジスタ

のゲート・ソース間電圧を高くする。

(もっと読む)

表示パネル、表示装置および電子機器

【課題】隣接する配線間の寄生容量を低減することの可能な表示パネル、表示装置および電子機器を提供する。

【解決手段】表示パネルは、行方向に延在する複数の第1配線と、列方向に延在する複数の第2配線と、各第1配線と各第2配線との交差点に対応して1つずつ配置された複数の画素とを備えている。複数の第1配線のうち2つの配線、または複数の第2配線のうち2つの配線は、ともに、互いに隣接する2つの画素に挟まれた共通の領域に配置されている。さらに、これら2つの配線の厚さ方向のレイアウトが、少なくとも一部において互いに異なっている。

(もっと読む)

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第1の透明導電膜6は、当該第1の透明導電膜6のコーナー部近傍では第2の導電膜5の端面を覆っておらず、コーナー部近傍以外において第2の導電膜5の端面を覆う部分を有している。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

電気光学装置、及び電子機器

【課題】液晶装置等の電気光学装置において、保持容量を十分に確保することができ、高品質な画像を表示可能とする。

【解決手段】ゲート電極30gと電気的に接続された走査線3aと、データ線側ソースドレイン領域30sと電気的に接続されたデータ線6aと、画素電極側ソースドレイン領域30dと電気的に接続された画素電極27と、容量線3bに電気的に接続された第1容量電極16aと、第1容量電極16aと対向して設けられた第2容量電極16cと、第1容量電極16aと第2容量電極16cとに挟持された誘電体層16bと、を有する容量素子16と、を備え、層間絶縁膜11eに設けられた複数の第1コンタクトホールCNT4を介して第1容量電極16aと容量線3bとは電気的に接続される。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

表示装置およびその製造方法、並びに電子機器

【課題】互いに電気的に接続された薄膜トランジスタの第2電極と配線層との間の電食の発生を防止して、安定した電気特性を得ることできる表示装置およびその製造方法、並びに電子機器を提供する。

【解決手段】薄膜トランジスタおよび配線層を備え、前記薄膜トランジスタは、制御電極

と、前記制御電極と対向する半導体層と、前記半導体層に電気的に接続され、光透過性材

料からなる第1電極と、前記光透過性材料よりも低抵抗の金属膜を含むと共に、前記半導

体層および前記配線層にそれぞれ電気的に接続された第2電極とを備え、前記金属膜の構

成材料と前記配線層の少なくとも一部を構成する導電材料とのイオン化傾向の差は、前記

光透過性材料と前記導電材料とのイオン化傾向の差よりも小さい表示装置。

(もっと読む)

表示装置

【課題】本発明では、信頼性の高い表示装置を低いコストで歩留まり良く製造するこ

とができる技術を提供することを目的とする。

【解決手段】本発明は、画素電極層上にスペーサを形成し、電界発光層形成時のマス

クから画素電極層を保護する。また、透水性を有する有機材料を含む層を表示装置の中に

シール材で封止し、かつシール材と有機材料を含む層が接しないため、発光素子の水等の

汚染物質による劣化を防ぐ事ができる。シール材は表示装置の駆動回路領域の一部に形成

されるため表示装置の狭額縁化も達成できる。

(もっと読む)

表示装置

【課題】額縁領域を大きさを抑えつつ、製造時に発生する静電気による静電破壊を防ぐダミー画素を有する表示装置を提供する。

【解決手段】表示装置は、薄膜トランジスタを含む画素を複数有し、画像を表示するための領域である表示領域(260)と、表示領域の外側に形成され、ダミー画素を複数有するダミー画素領域(270)と、を備え、ダミー画素(310)は、薄膜トランジスタのゲート信号線と平行なダミーゲート信号線(311)と、ダミーゲート線と絶縁層を介して交差する半導体層(313)と、を有し、半導体層には、一の導体層(312)のみが接続される。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減する。また、酸化物半導体膜の結晶性を向上させる。該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記ゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜における、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域において、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さく、少なくとも第1の領域内に、結晶部を含む半導体装置である。

(もっと読む)

発光装置

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口部もシンプルな形状にすることが出来る。

(もっと読む)

電気光学装置及び電子機器

【課題】極性反転駆動を行う際、極性反転に伴って、画素電極に導通する保持容量を切り換えることのできる電気光学装置、および電子機器を提供する。

【解決手段】電気光学装置において、画素電極9aの電位が共通電極21の電位より高い第1期間では、第1保持容量80aが画素電極9aに導通状態となるので、第1電極81、第1誘電体層86(第1絶縁材料/シリコン酸化膜/SiO2)、第2誘電体層87(第2絶縁材料/シリコン窒化膜/SiN)、および第2電極82に向けて電流が流れ、電荷が蓄積される。これに対して、画素電極9aの電位が共通電極21の電位より低い第2期間では、第2保持容量80bが画素電極9aに導通状態となるので、第4電極84、第4誘電体層89(第1絶縁材料/シリコン酸化膜/SiO2)、第3誘電体層88(第2絶縁材料/シリコン窒化膜/SiN)、および第3電極83に向けて電流が流れ、電荷が蓄積される。

(もっと読む)

電気光学装置、電気光学装置の製造方法、及び電子機器

【課題】表示品質を向上させることが可能な電気光学装置、電気光学装置の製造方法、及び電子機器を提供する。

【解決手段】液晶装置100は、TFT30と、TFT30に電気的に接続された容量素子16とを備え、容量素子16は、TFT30と第2層間絶縁層11cを介して形成された第1容量電極16aと、第1容量電極16aに第1誘電体層16bを介して対向配置され、TFT30の半導体層30aに第2層間絶縁層11cに形成されたコンタクトホールCNT53を介して電気的に接続された第2容量電極16cとを有し、第2容量電極16cは、第1導電層16c1と第1導電層16c1上に積層された第2導電層16c2を有し、第1導電層16c1は、コンタクトホールCNT53と重なる領域が除去されてなり、第2導電層16c2と半導体層30aとがコンタクトホールCNT53を介して電気的に接続される。

(もっと読む)

1 - 20 / 1,223

[ Back to top ]