Fターム[5E001AF06]の内容

セラミックコンデンサ (14,384) | 端子、リード (1,238) | 積層電極間の接続 (726)

Fターム[5E001AF06]に分類される特許

1 - 20 / 726

セラミック電子部品及びその製造方法

セラミック電子部品及びその製造方法

セラミック電子部品及びその製造方法

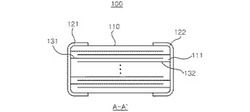

積層セラミック電子部品及びその製造方法

【課題】一定水準のESRを具現しながら、同一容量の積層セラミック電子部品におけるQ値の選択幅を広げる。

【解決手段】複数の誘電体層111が積層されたセラミック素体110と、セラミック素体110の内部に形成された第1及び第2内部電極131、132とを含み、第1及び第2内部電極131、132は、銅が80から99.9wt%、及び、ニッケルが0.1から20wt%を含み、周波数が1000MHz以下である積層セラミック電子部品を形成する。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品及びその製造方法に関する。

【解決手段】誘電体層を含み、誘電体層の積層方向に互いに対向する第1及び第2主面、第1及び第2主面を連結し、互いに対向する長さ方向の第3、第4側面及び幅方向の第5、第6断面を有するセラミック本体と、セラミック本体内で誘電体層を挟んで互いに対向するように配置される第1及び第2内部電極と、第5断面上に形成され、第1内部電極と電気的に連結された一つ以上の第1外部電極及び第6断面上に形成され、第2内部電極と電気的に連結された一つ以上の第2外部電極と、を含んでおり、第1及び第2外部電極は、導電性金属及びガラスを含み、平均厚さが3〜30μmであり、第1及び第2外部電極のうち少なくとも一つを厚さ方向に3等分したときに、中央部領域の面積に対してガラスが占める面積が35〜80%である。

(もっと読む)

セラミック電子部品

【課題】セラミック電子部品の鉛フリー半田実装時の半田食われを防止する。

【解決手段】端子電極のNi層にLi、Na、K、Rb及びCsの少なくとも1種を2×10−8mol/g以上7×10−6mol/gを添加することにより鉛フリー半田実装時の半田食われを防止する。さらに効果を顕著にするために、セラミック素体にZnを含ませる、あるいは、端子電極のNi層の結晶配向(111)面の相対強度を10−65%の範囲に制御する、ことの少なくとも一つをなす。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】めっき液の浸透を防止することでIRの低下を防止しながらも低いESL特性を有するようにした積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、複数の誘電体層が積層されたセラミック素体と、前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成され、前記セラミック素体の一面から露出するように延設された第1及び第2リード部をそれぞれ有する第1及び第2内部電極と、前記セラミック素体の一面に形成され、前記第1及び第2リード部の露出部により前記第1及び第2内部電極とそれぞれ電気的に接続される第1及び第2外部電極とを含み、前記第1又は第2外部電極の幅に対する前記第1又は第2リード部の幅の比が10〜85%である。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】デラミネーション及びBDVの低下を防止しながらも低いESL特性を有するようにした積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、複数の誘電体層が積層されたセラミック素体と、前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成される本体部、及び前記本体部の一面で前記セラミック素体の一面から露出するように延設された第1及び第2リード部をそれぞれ含む第1及び第2内部電極とを含み、前記本体部と前記第1及び第2リード部の内側連結部が曲面に形成され、前記連結部の曲率半径が30〜100μmである。

(もっと読む)

積層セラミック電子部品

【課題】本発明は、積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明は、誘電体層を含むセラミック本体と、上記セラミック本体内で上記誘電体層を介して対向するように配置される第1及び第2の内部電極と、上記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、を含み、上記第1及び第2の外部電極は導電性金属とガラスとを含み、上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%である積層セラミック電子部品及びその製造方法を提供する。

本発明によると、チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品の具現が可能となる。

(もっと読む)

4端子型セラミックコンデンサ

【課題】 実装面積をより小さくすることができ、かつ、耐振動性を向上させることが可能な4端子型セラミックコンデンサを提供する。

【解決手段】 4端子型セラミックコンデンサ1は、直方体状のセラミックコンデンサ部10と、対向する側面10a,10bに形成された一対の電極20,21と、一対の電極20,21それぞれに接続されたヘアピン状のリード線30,31とを備える。リード線30(31)は、側面10a(10b)の長手方向に伸びる一対の直線部30a,30b(31a,31b)と、該一対の直線部30a,30b(31a,31b)の端部同士を滑らかに接続する湾曲部30c(31c)とを含む。一方の直線部30a(31a)は電極20(21)に接続され、他方の直線部30b(31b)は電極20(21)と離間して設けられ、湾曲部30c(31c)は、平面視した場合に、側面10a(10b)に対して垂直な方向に伸びる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は積層セラミックキャパシタに関する。

【解決手段】本発明による積層セラミックキャパシタは、複数の誘電体層が積層されたセラミック素体と、上記複数の誘電体層に形成される複数の内部電極と、上記内部電極が形成されない誘電体層のマージン部に形成され、気孔率が10%以下であるマージン部誘電体層と、上記セラミック素体の外表面に形成される外部電極とを含んでよい。

(もっと読む)

積層セラミック電子部品

【課題】信頼性の高い高圧・高容量の積層セラミック電子部品を提供する。

【解決手段】セラミック本体10と、ギャップによって離隔して配置された導電パターンを含む第1の層と、当該第1の層とセラミック層を挟んで配置され上記導電パターンと重なる重なり部を有するフローティングパターンを含む第2の層と、を含み、上記第1の層の数と上記第2の層の数との和は100以上であり、上記セラミック本体の外部面には第1及び第2の外部電極が形成され、上記第1及び第2の外部電極21,22を連結して延びる長さ方向と上記第1の層及び上記第2の層を積層する積層方向によって形成される平面において、上記セラミック本体の長さに対する上記フローティングパターンの長さの比は0.7〜0.9であり、上記フローティングパターンの長さに対する上記重なり部の長さの比は0.5〜0.95以下であることを特徴とする。

(もっと読む)

積層セラミックキャパシタ及びその製造方法

【課題】本発明は、積層セラミックキャパシタ及びその製造方法に関する。

【解決手段】本発明は、誘電体層と内部電極が積層されたキャパシタ本体と、前記キャパシタ本体の表面に形成された外部電極と、めっき層と、前記外部電極とめっき層との間に無電解めっき層と、を含む積層セラミックキャパシタ及びその製造方法に関する。本発明の実施例によると、外部電極にめっき層を形成する前に、無電解めっき層を形成することにより、外部電極にニッケルのようなめっき層を形成する場合、不めっき不良を解決することができる。従って、ニッケルなどの不めっきによる実装の際のはんだ付け不良問題を解決することができ、高信頼性を有する積層セラミックキャパシタを提供することができる。

(もっと読む)

チップ型電子部品及びチップ型電子部品の製造方法

【課題】チップ型電子部品が外部から受ける応力を緩和して、チップ型電子部品に発生するクラックを抑制すること。

【解決手段】チップ型電子部品10は、誘電体を含むセラミック素体11と、セラミック素体11の内部に配置され、かつ、セラミック素体11の表面に一部が露出する内部電極17、18と、セラミック素体11の表面に配置された端子電極20、30と、を含む。端子電極20、30は、第1の導電性材料と第1の樹脂とを含み、かつセラミック素体11の内部電極17、18が露出する端面13、14に配置される第1の樹脂層21、31と、第2の樹脂を含むとともに、第1の樹脂層21、31の少なくとも一部と接触し、かつ第1の樹脂層21、31よりもヤング率が低い第2の樹脂層22、32と、を含む。

(もっと読む)

セラミック電子部品及びその製造方法

【課題】はんだ接合部の信頼性を高めた低コストなセラミック電子部品及びその製造方法を提供する。

【解決手段】端面にはんだ接合部を有し、そのはんだ接合部がセラミック素体上に設けられた銅層11と、その銅層11上に設けられたCuNiSn金属間化合物層12と、その金属間化合物層12上に設けられたSnAgCuNiGeの5元系はんだ層13とを有するように構成して上記課題を解決した。そのCuNiSn金属間化合物層12は、はんだ食われのバリア層となって銅層11のはんだ食われを防ぐので、セラミック電子部品10をプリント基板の銅ランド等にはんだ実装する際に、従来そのはんだ実装時にも起こる銅層11のはんだ食われが抑制でき、セラミック素体1の銅層11が十分に確保されて信頼性を高めることができる。

(もっと読む)

実装構造

【課題】回路設計において高い自由度を得つつ、鳴きを低減することができる実装構造を提供することである。

【解決手段】電子部品10が回路基板50上に実装されている実装構造1。ランド54a,54bは、基板本体52上に設けられ、外部電極12a,12bのそれぞれとはんだ60a,60bにより接続されている。ランド電極54a,54bからはんだ60a,60bの頂上までの高さH1は、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さH2の1.27倍以下である。

(もっと読む)

電子部品

【課題】低コストで且つ生産性に優れると共に、狭隣接高密度実装を可能とする電子部品を提供すること。

【解決手段】電子部品1は、素体2と、外部電極3,4と、絶縁性樹脂コーティング層21と、を備えている。素体2は、互いに対向する一対の端面2a,2bと、一対の端面2a,2b間を連結するように伸び且つ互いに対向する一対の主面2c,2dと、一対の主面2c,2dを連結するように伸び且つ互いに対向する一対の側面2e,2fと、を有している。外部電極3,4は、主面2c,2dの一部及び/又は側面2e,2fの一部を少なくとも覆うように形成されると共に、Sn又はSn合金からなるめっき層を有している。絶縁性樹脂コーティング層21は、外部電極3,4における側面2e,2fを覆うように形成された部分を少なくとも覆っている。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は、誘電体層と内部電極との接着力に優れた積層セラミック電子部品に関する。

【解決手段】本発明は、誘電体層を含むセラミック本体と、当該セラミック本体内で当該誘電体層を介して対向配置される内部電極と、を含み、上記誘電体層の平均厚さをtd、上記内部電極の平均厚さをteとすると、0.1μm≦te≦0.5μmであり、(td+te)/te≦2.5を満足し、上記内部電極の中心線平均粗さをRa、十点平均粗さをRzとすると、5nm≦Ra≦30nm、150nm≦Rz≦td/2及び8≦Rz/Ra≦20を満足する積層セラミック電子部品を提供する。本発明によると、誘電体層と内部電極との接着力及び耐電圧特性が向上して信頼性に優れた大容量積層セラミック電子部品の具現が可能となる。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタに関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、セラミック素体と、上記セラミック素体の内部に形成され、上記セラミック素体の第1面及び上記第1面と連結された第3面または第4面に露出し、上記第1面に露出した領域のうち一部が互いに重なる引出し部を有する第1及び第2内部電極と、上記セラミック素体の第1面及び上記第1面から延長されて上記第1面と連結された第3面または第4面に形成され、上記引出し部と夫々連結される第1及び第2外部電極と、上記セラミック素体の第1面、上記第1面と連結された第3面及び第4面に形成される絶縁層と、を含む。

(もっと読む)

電極用銅ペースト。

【課題】現状では、銀ペーストの変わる銅導電性ペーストが開発されているが、接着強度に問題がある。接着強度が強く、特に、フェライトコアーの外部電極として使用できる銅導電性ペーストの提供。

【解決手段】微細銅粉を主体とし、金属或はこれ等の酸化物、ガラスフリット、ビビクルで構成された銅導電性ペーストに、更に、多くの気孔率を有する炭化珪素及び多孔質セラミックス等を添加することで、微細銅粉との、結合を強め銅導電性ペーストとして素子との密着強度を向上させる。

(もっと読む)

1 - 20 / 726

[ Back to top ]