Fターム[5E082AA01]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 外観形状 (1,673) | 表面実装型、チップ型 (1,454)

Fターム[5E082AA01]の下位に属するFターム

本体から突出した端子を持つもの (29)

Fターム[5E082AA01]に分類される特許

161 - 180 / 1,425

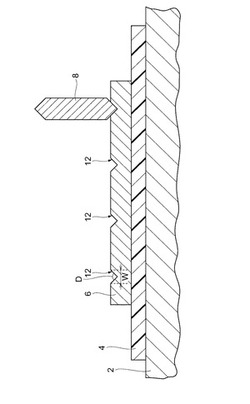

セラミック電子部品の製造方法

【課題】ガラスセラミックチップのチッピング及び飛散を抑制することが可能なセラミック電子部品の製造方法を提供すること。

【解決手段】ガラスセラミックチップを具備するセラミック電子部品の製造方法であって、台座2に貼り付けた粘着シート4上に固定したガラスセラミック基板6の片面のみに、刃先がテーパー状である第一ダイシングブレード8を用いてV字形の溝12を形成する工程と、刃幅が溝の幅よりも小さい第二ダイシングブレードを、粘着シート4上に固定されたガラスセラミック基板6の溝12内に当接させて、ガラスセラミック基板6を完全に切断して、ガラスセラミックチップを形成する工程と、を備える。

(もっと読む)

コンデンサ構成用ユニット及びコンデンサ

【課題】従前の積層型コンデンサと互換性があり、且つ、高耐電圧化の要求を満たすコンデンサを構成するのに有用なユニットを提供する。

【解決手段】ユニットU10は、厚さ方向の複数の貫通孔11aが形成された矩形状の誘電体プレート11と、プレート上面の前端部及び後端部を除く領域を覆う第1導体膜14と、プレート上面の前端部を覆う第1絶縁体膜16と、プレート上面の後端部を覆う第2絶縁体膜17と、プレート下面の前端部及び後端部を除く領域を覆う第2導体膜15と、プレート下面の前端部を覆う第3絶縁体膜17と、プレート下面の後端部を覆う第4絶縁体膜18と、複数の貫通孔11aの一部の内側に配置されていて第1導体膜14に電気的に接続され第2導体膜15に電気的に絶縁された複数の第1電極棒12と、複数の貫通孔11aの残部の内側に配置されていて第2導体膜15に電気的に接続され第1導体膜14に電気的に絶縁された複数の第2電極棒13とを備える。

(もっと読む)

積層セラミックキャパシタ及びその製造方法

【課題】本発明は積層セラミックキャパシタ及びその製造方法に関する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、対向する第1側面及び第2側面、上記第1側面及び第2側面を連結する第3側面及び第4側面を有するセラミック本体と、上記セラミック本体の内部に形成され、上記第3側面または第4側面に一端が露出する複数個の内部電極と、上記第3側面または第4側面に形成され、上記内部電極と電気的に連結される外部電極とを含み、上記複数個の内部電極のうち最外郭に配置される内部電極の末端から上記第1側面または第2側面までの最短距離は中央部に配置される内部電極の末端から上記第1側面または第2側面までの最短距離より小さいか、同一に形成されることができる。

(もっと読む)

積層コンデンサ

【課題】ESLを高めることが可能な積層コンデンサを提供すること。

【解決手段】第一貫通導体17は、複数の絶縁体層11の積層方向に沿って延びるように素体2内に配置され、一端が第一端子電極3の第二電極部分3bに接続され且つ他端が素体2内に位置している。第二貫通導体19は、上記積層方向に沿って延びるように素体2内に配置され、一端が第二端子電極5の第二電極部分5bに接続され且つ他端が素体内2に位置している。第一内部電極13は、第一接続導体7のみに接続されている。第二内部電極15は、第二接続導体9のみに接続されている。第三内部電極14は、第一接続導体7及び第一貫通導体17に接続されている。第四内部電極16は、第二接続導体9及び第二貫通導体17に接続されている。第三及び第四内部電極14,16は、第一及び第二内部電極13,15よりも第一主面2a側に位置している。

(もっと読む)

積層セラミックキャパシタ及びその製造方法

【課題】機械的強度及び信頼性に優れた積層セラミックキャパシタ及びその製造方法を提供する。

【解決手段】積層セラミックキャパシタは、対向する第1の側面及び第2の側面と当該第1の側面及び第2の側面を連結する第3の側面3及び第4の側面4とを有する積層本体と、当該積層本体の内部に形成され上記第3の側面又は第4の側面から所定の間隔をおいて形成される内部電極121,122と、上記積層本体の上面及び下面の少なくとも一面に形成され上記第3の側面又は第4の側面と所定の間隔をおいて当該第3の側面又は第4の側面に沿って形成される溝部Vと、上記第3の側面及び第4の側面から上記積層本体の上面又は下面まで伸びて上記溝部を覆うように形成される外部電極131,132とを含むことができる。

(もっと読む)

積層セラミックキャパシタ及びその製造方法

【課題】信頼性に優れた高容量積層セラミックキャパシタ及びその製造方法を提供する。

【解決手段】本発明の一実施形態による積層セラミックキャパシタは、対向する第1及び第2側面、上記第1及び第2側面を連結する第3及び第4側面を有する積層本体と、上記積層本体の内部に形成され、上記第1側面及び第2側面に末端が露出する複数個の内部電極と、上記複数個の内部電極の末端を覆うように上記第1及び第2側面に形成される第1及び第2サイド部と、上記第3及び第4側面に形成され、上記内部電極と電気的に連結される外部電極とを含み、上記複数個の内部電極の末端を連結する仮想線と上記第1サイド部または第2サイド部の成す角度が90゜(π/2)以下になるように形成されている。

(もっと読む)

積層セラミックコンデンサ及び積層セラミックコンデンサの製造方法

【課題】内部電極層が位置ずれして積層されても、所定の静電容量を確保できる、寸法安定性に優れた積層セラミックコンデンサ及び積層セラミックコンデンサの製造方法を提供する。

【解決手段】この積層セラミックコンデンサは、静電容量形成部及び引出部を有する第1の内部電極層23及び第2の内部電極層23が、セラミック誘電体層21を介して交互に積層されたセラミック積層体20と、その両端面に形成された外部電極とを備え、第1の内部電極層23の静電容量形成部23aの幅は、第2の内部電極層25の静電容量形成部25aの幅よりも広く形成され、第1の内部電極層23の引出部23bは、その静電容量形成部23aよりも幅狭で、かつ、第2の内部電極層25の引出部25bの幅と等しくなるように形成されている。

(もっと読む)

3端子コンデンサおよびその実装構造

【課題】 従来の3端子コンデンサを非貫通で使用してバイパスコンデンサとしても、ESLの低減が十分でなく、さらなる低ESL化が求められている。

【解決手段】 3端子コンデンサ21には、誘電体22の厚さ方向に貫通する貫通ビア26が、グランド内部電極25に電気接触せず、貫通内部電極23に電気接触して、設けられている。この貫通ビア26は、上下の両端面が、入出力端子24a、24b間の誘電体22の表面に露出している。このため、貫通ビア26を電源プレーン層32に接続すると共に、入出力端子24a、24b間を電源プレーン層32で短絡して非貫通で使用することにより、電源ライン用配線パターン31a、31bとグランドプレーン層33との間には、電源プレーン層32から貫通ビア26を経由して容量を介しグランドプレーン層33に至るリターン経路が新たに形成される。

(もっと読む)

チタン酸バリウム粉末の製造方法およびそれを用いた積層セラミックコンデンサ

【課題】小さい粒子径でかつ高い正方晶性を有するチタン酸バリウム粉末の製造方法およびそのチタン酸バリウム粉末を用いた積層セラミックコンデンサを提供することを目的とする。

【解決手段】BET法による比表面積がそれぞれ20m2/g以上の炭酸バリウム粉末と20m2/g以上の酸化チタン粉末を少なくとも含む原料粉末を準備する準備工程と、BET法による比表面積がAm2/gの前記炭酸バリウム粉末xgとBET法による比表面積がBm2/gの前記酸化チタン粉末ygを混合する際に

C=(Ax+By)/(x+y)

で表される混合前の前記原料粉末のトータル比表面積Cm2/gに対し混合後の混合粉末のBET法による比表面積が1.1×Cm2/g以下となるように混合する混合工程と、この混合工程にて得られた混合粉末を1×102Pa以下の酸素分圧中で熱処理する熱処

理工程を含む、チタン酸バリウム粉末の製造方法。

(もっと読む)

積層セラミックキャパシタ

【課題】本発明は積層セラミックキャパシタに関する。

【解決手段】本発明による積層セラミックキャパシタは、対向する第1側面及び第2側面、第1側面及び第2側面を連結する第3側面及び第4側面を有するセラミック本体と、セラミック本体の内部に形成され、第3側面または第4側面に一端が露出する複数個の内部電極と、第3側面または第4側面に形成され、内部電極と電気的に連結される外部電極と、内部電極と交互に積層され、セラミック粉末からなる誘電体層とを含み、セラミック粉末の粒径が130μm以下であることを特徴とする。これにより、セラミック粉末とチップ誘電率及び誘電体の厚さを調節することで、積層セラミックキャパシタで発生される音響ノイズ(acoustic noise)を減少させることができる効果がある。よって、積層セラミックキャパシタが用いられる電子製品の騷音も減少させることができる。

(もっと読む)

ペロブスカイト型複合酸化物の製造方法

【課題】誘電体層の積層数が多く、薄層化された積層セラミックコンデンサの誘電体層などに好適に用いることが可能な、微細で、結晶性の高いペロブスカイト型複合酸化物を効率よく、しかも経済的に製造する方法を提供する。

【解決手段】少なくとも酸化チタン、カルシウム化合物、および水酸化バリウムを、スラリー液中で反応させることにより、ペロブスカイト型複合酸化物を生成させる反応工程を含み、かつ、カルシウム化合物として、炭酸カルシウムを用い、ペロブスカイト型複合酸化物を(Ba1-xCax)mTiO3で表したときに、xが0<x≦0.125の範囲にあるペロブスカイト型複合酸化物を得る。

また、カルシウム化合物として、水溶性のカルシウム化合物を用い、ペロブスカイト型複合酸化物を(Ba1-xCax)mTiO3で表したとき、xが0<x≦0.20の範囲にあるペロブスカイト型複合酸化物を得る。

(もっと読む)

チップ状電子部品

【課題】耐湿性が高く且つ工程負荷の小さなチップ状電子部品を提供する。

【解決手段】 内部電極11が埋設された略直方体形状の部品本体10と、部品本体10外面に形成され且つ前記内部電極11と導通する外部電極20とを備えたチップ状電子部品1において、外部電極形成部以外の部品本体10の外面には窒化珪素系薄膜30が形成されている。

(もっと読む)

積層セラミックコンデンサ内部電極に用いられるグラビア印刷用導電性ペースト

【課題】 グラビア印刷に適した粘度を有し、乾燥性が良く、なおかつ導電性粉末と誘電体粉末の分離が発生しない積層セラミックコンデンサ内部電極作製に用いられるグラビア印刷用導電性ペーストを提供する。

【解決手段】 導電性粉末、有機樹脂、有機溶剤、添加剤、及び誘電体粉末を含む積層セラミックコンデンサ内部電極用導電性ペーストであって、有機樹脂として重合度が10000〜50000のポリビニルブチラールと、重量平均分子量が10000〜100000のエチルセルロースを含み、有機溶剤はプロピレングリコールモノブチルエーテル、もしくはプロピレングリコールモノブチルエーテルとプロピレングリコールメチルエーテルアセテートの混合物又はプロピレングリコールモノブチルエーテルとミネラルスピリットの混合物うちのいずれかからなり、添加剤が分離抑制剤と分散剤からなり、そのうち分離抑制剤がポリカルボン酸ポリマーもしくはポリカルボン酸の塩を含む組成物からなる。

(もっと読む)

積層セラミックコンデンサ

【課題】焼結性を向上させることができると共に耐還元性を付与することができ、しかも比誘電率を高めることができる積層セラミックコンデンサを提供する。

【解決手段】積層セラミックコンデンサ1は、積層された複数の誘電体セラミック層2と、これらの誘電体セラミック層間に配置された内部電極3A3Bと、これらの内部電極に電気的に接続された外部電極4A4Bと、を備え、上記誘電体セラミック層は、組成式(K1−yNay)Sr2Nb5O15(但し、0≦y<0.2)で表されるタングステンブロンズ型複合酸化物を主成分として含む誘電体セラミック組成物によって形成されていると共に、上記組成式中のNbの20モル%以下が副成分で置換されており、上記副成分として、Mnが含まれると共にCr、Co、Fe、Ni、Zn、Mg、Siから選択される少なくとも一種が含まれることがある。

(もっと読む)

セラミック電子部品の製造方法及びセラミック電子部品

【課題】直方体状のセラミック素体の端面に引き出された内部電極に電気的に接続されており、めっき膜からなる外部電極を備えるセラミック電子部品を好適に製造し得る方法を提供する。

【解決手段】複数の第1及び第2の内部電極11,12が内部に形成されたセラミック素体30を用意する。第1及び第2の内部電極露出率が102%〜153%となるようにセラミック素体30を加工する加工工程を行う。加工されたセラミック素体10の上にめっき膜を形成するめっき工程を行う。

(もっと読む)

貫通型積層コンデンサ

【課題】コンデンサ素体と接地用端子電極との密着性を向上させることができる貫通型積層コンデンサを提供すること。

【解決手段】貫通型積層コンデンサC1は、誘電体層10が積層されたコンデンサ素体L1と、接地用内部電極20と、接地用内部電極20よりも積層数が多い信号用内部電極31,32と、接地用内部電極20に接続される接地用端子電極3,4と、信号用内部電極31,32に接続される信号用端子電極1,2と、引き出し電極部20b,20cの幅Aよりも狭い幅B1,B2で接地用端子電極3,4に接続されるダミー電極36〜39とを備えている。ダミー電極36〜39は、誘電体層10の積層方向から見た際に積層方向に隣接するダミー電極36〜39同士が接地用内部電極20の引き出し電極部20b,20cに重なる領域内において互いに重ならないように配置される。

(もっと読む)

誘電体磁器組成物およびセラミック電子部品

【課題】高い電界強度下においても良好な特性を示す誘電体磁器組成物、および該誘電体磁器組成物が誘電体層に適用されたセラミック電子部品を提供すること。

【解決手段】チタン酸バリウムを、主成分として含有し、チタン酸バリウム100モルに対して、副成分を5.0モル以上含む誘電体磁器組成物である。副成分は希土類元素の酸化物を有している。誘電体磁器組成物には、誘電体粒子として、コア21aと、コアの周囲に存在し、R元素が固溶しているシェル21bと、からなるコアシェル構造を有するコアシェル構造粒子21と、R元素が誘電体粒子全体に固溶している全固溶粒子22と、が存在しており、誘電体粒子の個数100%に対して、全固溶粒子22の個数割合をx(%)としたとき、x≧10である。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】本発明は積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明による積層セラミック電子部品は、平均粒径が100から300nmであるセラミック粉末を含む誘電体組成物で形成された誘電体層と内部電極が交互に積層されたアクティブ層と、上記アクティブ層の上面及び下面のうち少なくとも一面に形成され、平均粒径が50から250nmで、上記アクティブ層と同一種類のセラミック粉末を含む誘電体組成物で形成されたカバー層と、上記内部電極層と電気的に連結される外部電極とを含む。本発明による積層セラミック電子部品は、カバー層とアクティブ層を同時に均一に焼成させ、焼結収縮の不一致を最小化することで、信頼性が向上する効果がある。

(もっと読む)

容量素子、容量素子の製造方法、共振回路、通信システム、ワイヤレス充電システム、電源装置及び電子機器

【課題】静電容量の値を精度良く確保できる容量素子、及び、容量可変率を十分に確保することのできる可変容量素子を提供する。また、これらの容量素子を用いた共振回路、通信システム、ワイヤレス充電システム、電源装置及び電子機器を提供する。

【解決手段】本発明の容量素子(可変容量素子1)は、誘電体層4と誘電体層4を挟持して誘電体層4に所望の電界を発生させる少なくとも1対の容量素子電極5a、5bとで構成される容量素子本体2を備える。また、容量素子本体2の誘電体層4に発生する応力を制御し、容量素子本体2の静電容量を増加させる応力制御部6、7を備える。

(もっと読む)

チップ部品およびその製造方法

【課題】大型でも、高性能で高品質で、実装状態で高い信頼性を確保することのできるチップ部品を提供する。

【解決手段】誘電体素子11と、該誘電体素子の内部に設けた内部電極11aと、該内部電極と電気的に接続した外部電極層15とを備え、誘電体素子11と外部電極層15の間に誘電体素子11の全面を覆うガラス層12を有し、外部電極層15は、金属成分を含む下地電極13と、樹脂電極14とからなり、樹脂電極14は、下地電極13を覆い、かつ誘電体素子11にガラス層12を介して接合する。ガラス層12は、結晶化ガラスからなることが好ましい。

(もっと読む)

161 - 180 / 1,425

[ Back to top ]