Fターム[5E082AA05]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 外観形状 (1,673) | 挿入実装型 (61)

Fターム[5E082AA05]の下位に属するFターム

Fターム[5E082AA05]に分類される特許

1 - 8 / 8

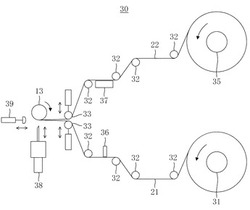

フィルムコンデンサ及びその製造方法

【課題】両面に金属膜が形成された金属化フィルムを厚み方向に重ね合わせたフィルムコンデンサにおいて、対向する分割電極同士を位置ずれすることなく重ね合わせる。

【解決手段】検出ユニット(36)により第1の金属化フィルム(21)における第1の分割電極(21a)の分割位置を検出し、検出ユニット(36)で検出された分割位置に基づいて、除去ユニット(37)により第2の金属化フィルム(22)の金属膜(20b)を分割して第2の分割電極(22a)を形成し、第1及び第2の分割電極(21a,22a)とがそれぞれ対向するように、第1及び第2の金属化フィルム(21,22)を重ね合わせる。

(もっと読む)

誘電体組成物及びこれを用いた積層セラミックキャパシタ内蔵型低温同時焼成セラミック基板

【課題】誘電体組成物及びこれを用いた積層セラミックキャパシタ内蔵型低温同時焼成セラミック基板を提供すること。

【解決手段】主成分として80wt%以上のBaTiO3と、副成分として20wt%以下のCuBi2O4及びZnO−B2O3−SiO2系ガラスを含む誘電体組成物と、セラミックシートの内部電極が印刷された複数のセラミックグリーンシートが積層されたセラミック積層体の内部に、複数の誘電体層と、前記誘電体層の間に形成され前記セラミックシートの内部電極に接続された複数のキャパシタの内部電極を含み、上記誘電体組成物を含む積層セラミックキャパシタ内蔵型低温同時焼成セラミック基板を提供する。

(もっと読む)

コンデンサ素子

【課題】コンデンサ素子内蔵多層配線基板において、小型化・接続信頼性および電気特性を満足できない。

【解決手段】本発明の一実施形態にかかるコンデンサ素子7は、複数の電極層5および複数の誘電体層6を積層して成る積層体と、前記複数の電極層5に対して積層方向に前記積層体を貫通する貫通孔9内に導体を充填して前記積層体と同時焼成して成り、積層方向に平行な断面形状が台形状である引き出し電極部10と、を備えたことを特徴とする。

(もっと読む)

キャパシタ内蔵基板及びその製造方法

【課題】キャパシタの静電容量が大きくなる場合であっても所望の高周波特性が得られると共に、キャパシタが簡易な電極構造で回路基板に内蔵されるキャパシタ内蔵基板を提供する。

【解決手段】下部共通電極12と、下部共通電極12の上に相互に分離されて形成され、下部共通電極12と電気的に結合する複数の誘電体部14と、複数の誘電体部14の間及び横領域に形成された絶縁層16と、誘電体部14及び絶縁層16の上に形成され、複数の誘電体部14に電気的に結合する上部共通電極18とにより構成されるキャパシタCを含む。

(もっと読む)

配線基板内蔵用コンデンサの製造方法、配線基板内蔵用コンデンサ、及び配線基板

【課題】配線基板に内蔵させた場合における導通不良を低減させることができる配線基板内蔵用コンデンサの製造方法、配線基板内蔵用コンデンサ、及びこれを備えた配線基板を提供する。

【解決手段】複数のセラミック層、及びセラミック層間に配置された複数の内部電極層とを有するコンデンサ本体部と、セラミック材料から構成されたコンデンサ端部とを備えるコンデンサの製造方法であって、セラミックグリーンシート25,28の表面にかつコンデンサ本体部となる領域に、内部電極パターン23,26を形成する工程と、セラミックグリーンシート22の表面にかつコンデンサ端部に、コンデンサ端部の一部となるセラミックパターン21を形成する工程とを備えるコンデンサの製造方法が提供される。

(もっと読む)

コンデンサおよびそれを用いた複合部品

【課題】特に小型・薄型化に適し、高周波特性に優れたコンデンサおよびそれを用いた複合部品を提供することを目的とするものである。

【解決手段】導電性を有する基板11に一つ以上の貫通孔10を設け、前記貫通孔10の内壁に誘電体層12を設け、この誘電体層12を設けた貫通孔10の内部に電極部13を設け、前記基板11の端部に基板11と接続された一方の接続端子16を設け、前記電極部13の少なくとも片面に他方の接続端子15を設けた構成とする。

(もっと読む)

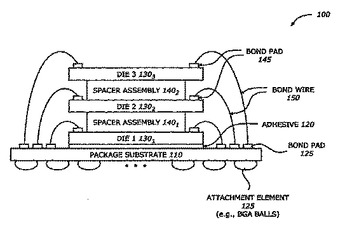

積層ダイ内のスペーサに接した複数の受動素子を集積する方法

本発明の一実施形態は、複数の受動素子をダイアセンブリの中に集積するための技術である。キャパシタ、インダクタ、またはレジスタは、複数の集積ダイの中の上部のダイと下部のダイとの間のスペーサに接して集積される。複数のコンダクタは、前記キャパシタ、インダクタ、またはレジスタを前記上部のおよび下部のダイに接続するために、前記キャパシタ、インダクタ、またはレジスタに取り付けられる。

(もっと読む)

(もっと読む)

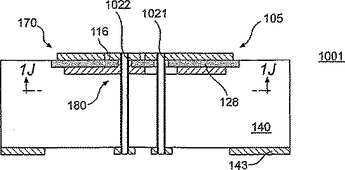

低インダクタンス埋め込みキャパシタを有するプリント配線板およびその製造方法

プリント配線板(PWB)は、受動回路素子(105)からなる積み重ねられた中間層パネル(1001、1002、1003、...)を有する。受動素子(105)は、電極終端がキャパシタ電極(170、180)のフットプリント内に位置付けられるキャパシタを含むことができる。したがってキャパシタ終端が、狭い間隔で離間して配置されるため、中間層内のループ・インダクタンスに対するキャパシタの寄与が減る。また電極フットプリント内にキャパシタ終端があることによって、キャパシタを形成する際に用いられるPWBボード表面積が減る。キャパシタ終端は、回路導体(1021、1022)によって接続される。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]