Fターム[5E082AA20]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 外観形状 (1,673) | その他の外観形状 (52)

Fターム[5E082AA20]に分類される特許

1 - 20 / 52

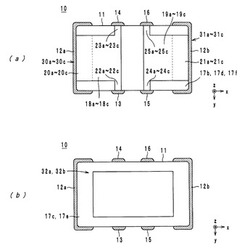

電子部品及び基板モジュール

【課題】低ESL化を図ることができると共に、回路基板への実装の際にショートが発生することを抑制できる電子部品及び基板モジュールを提供することである。

【解決手段】積層体11は、コンデンサを形成している容量導体18,19及び内部導体32を内蔵している。外部電極12a,12bはそれぞれ、容量導体18,19に引き出し導体20,21を介して接続されている。内部導体32は、容量導体18,19に対向している。外部電極13,14は、引き出し導体22,23を介して容量導体18に接続されている。外部電極15,16は、引き出し導体24,25を介して容量導体19に接続されている。

(もっと読む)

誘電体セラミックスおよび共振器

【課題】 比誘電率εrが40前後において、Q値が高く、共振周波数の温度係数τfの絶対値が小さく、高温域および低温域にわたる広範囲な温度域において、共振周波数の変化の少ない誘電体セラミックスを提供する。

【解決手段】 組成式をαNd2Ox・βMgO・γCaO・δTiO2(ただし、3≦x≦4)で表したとき、モル比α,β,γ,δが、0.216<α<0.385,0.064<β<0.146,0.181<γ<0.312,0.321<δ<0.386、かつα+β+γ+δ=1を満足し、前記組成式の成分100質量%に対してアルミニウムを酸化物換算で6質量%以下(0質量%を除く

)含む誘電体セラミックスである。この誘電体セラミックスは、比誘電率εrが40前後において、Q値が30000以上であり、共振周波数の温度係数τfの絶対値が10ppm/℃以

下であり、高温域および低温域の共振周波数の温度係数τfの値の差が2ppm/℃以下である。

(もっと読む)

印刷回路基板およびその製造方法

【課題】基板内形成のための加熱制限があってもキャパシタ誘電体膜において高い比誘電率を得る。

【解決手段】基板内部の基板樹脂層3にキャパシタ10を埋め込んで形成する。その形成工程では、下部電極11を形成し、基板樹脂層3の耐熱温度以下、室温以上で結晶質金属酸化物を含むキャパシタ誘電体膜12を形成し、その上面で下部電極11と対向する上部電極13を形成する。

(もっと読む)

部品内蔵配線板

【課題】絶縁板中に部品が埋設、実装された部品内蔵配線板において、薄板化が可能な部品内蔵配線板を提供すること。

【解決手段】第1の絶縁層と、第1の絶縁層に対して積層状に位置する第2の絶縁層と、第2の絶縁層に埋設された、複数の端子を有する受動素子部品と、第1の絶縁層と第2の絶縁層とに挟まれて設けられた、受動素子部品用の接続ランドを含む配線パターンと、受動素子部品の複数の端子と配線パターンの接続ランドとを電気的に接続する接続部材とを具備し、受動素子部品が、板状の無機材料基材と、該無機材料基材の一方の面上に層状に形成された受動素子とを有し、受動素子部品の複数の端子が、受動素子に電気的に連なり、かつ、前記無機材料基材の前記一方の面上に設けられている。

(もっと読む)

電子部品

【課題】端子と部品素子の端子電極との接続を簡便に行うことができる電子部品を提供する。

【解決手段】 チップ型積層コンデンサ1は、2つのコンデンサ素子2と、各コンデンサ素子2を収容する絶縁ケース6と、各コンデンサ素子2を絶縁ケース6に固定する固定金具7と、コンデンサ素子2の端子電極5と接続される端子接続部15を有する2つの端子金具8とを備えている。フレーム体9の対向する内側側面には、段差12aを有する溝部12が上下に形成されている。固定金具7により各コンデンサ素子2が絶縁ケース6に固定されるときは、固定金具7の弾性力により各折り返し部14が段差12aに係止された状態となる。端子接続部15がコンデンサ素子2の端子電極5と接続されるときは、端子接続部15の弾性力により折り返し部分17が段差12aに係止された状態となる。

(もっと読む)

セラミックコンデンサの製造方法

【課題】面取り部を短時間でかつ低コストで形成することができるセラミックコンデンサの製造方法を提供すること。

【解決手段】本発明のセラミックコンデンサは、積層工程、溝部形成工程、焼成工程及び分割工程を経て製造される。積層工程では、グリーンシート211〜213を積層一体化して、セラミックコンデンサとなるべき製品領域217を平面方向に沿って縦横に複数配列した構造の多数個取り用積層体216を作製する。溝部形成工程では、製品領域217の外形線221に沿ってレーザー加工を行うことにより、面取り部を形成するための溝部222,223を形成する。焼成工程では多数個取り用積層体216を焼結させ、分割工程では製品領域217どうしを溝部222,223に沿って分割する。

(もっと読む)

電気エネルギー蓄積装置

時間的に変化する電磁場で使用するために構成された電気エネルギー蓄積装置であって、その蓄積装置は、その蓄積装置内で循環するようにその電磁場により誘導される渦電流の能力を妨げるように構成される、少なくとも電極の一部を備える。 (もっと読む)

薄膜キャパシタ

【課題】周辺環境の水分を吸湿することもなく、良好な信頼性を有する耐湿性の向上した薄膜キャパシタを実現する。

【解決手段】キャパシタ部8は、誘電体薄膜5の下面に第1の電極膜4が形成されると共に前記誘電体薄膜5の上面に第2の電極膜5が形成され、さらに第2の電極膜5の上面に誘電体薄膜5と同一材料からなる絶縁体薄膜7が形成されている。キャパシタ部8、密着層3、及びSiO2からなる酸化物層1は、二層の絶縁膜9、すなわち無機保護膜10及び有機保護膜11で被覆されている。第1及び第2の引出電極12、13は、互いに電気的に絶縁されると共に、保護膜10を貫通して第1及び第2の電極膜4、5に電気的に接続されている。そして、外部接続電極14、15を除く部位が無機保護膜16で被覆され、かつ無機保護膜16は有機保護膜17で被覆されている。

(もっと読む)

交差部のアレイを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(100)は、ICの層に形成され、キャパシタの第1のノードに電気的に接続され、かつ第1のノードの一部分を形成する第1の複数の導電性交差部(102,104)と、ICの金属層に形成された第2の複数の導電性交差部(108,110)とを有する。第2の複数の導電性交差部の導電性交差部は、キャパシタの第2のノードに電気的に接続され、かつ第2のノードの一部分を形成し、第1のノードに容量結合する。  (もっと読む)

(もっと読む)

はんだボール

【課題】受動素子としての機能を有するはんだボールについて、実装状態がばらついても、受動素子としての機能を維持することができるはんだボールを提供する。

【解決手段】受動素子としての機能を有するはんだボール1であって、はんだボール1の中心部に配設される芯部材2と、芯部材2を被装するはんだ合金部材3と、を備え、はんだ合金部材3には、所望する抵抗値R1aを実現するために必要な電気抵抗率を有するはんだ合金が使用され、芯部材2には、所望する抵抗値R1aに比して十分大きな抵抗値を有する素材(芯部材2に流れる電流値がほぼ0となるような抵抗値を有する素材)が使用され、所望する抵抗値R1aを有する抵抗器としての機能を有する。

(もっと読む)

蓄電装置の応用構造

【課題】スーパーキャパシタや磁気コンデンサ等の体積が微小な蓄電素子に応用できる蓄電装置の応用構造を提供する。

【解決手段】複数個の蓄電素子150と、少なくとも一組の正負極構造とを備えた蓄電装置の応用構造100である。複数個の蓄電素子150の配列構造は、数量の異なる蓄電素子150を直列または並列に接続しやすくするものであり、各々の蓄電素子150は平面型正極端子153と、平面型負極端子156とを備え、平面型負極端子156および平面型正極端子153は同じ辺、または平面型正極端子153の対向辺に配置されている。少なくとも一組の正負極構造が対外的に接続される。

(もっと読む)

コンデンサ

【課題】等価直列抵抗ESR(Equivalent Series Resistance)を低減することができるコンデンサを提供する。

【解決手段】コンデンサは、(a)一対の電極層15,17と、(b)一対の電極層15,17の間に配置された誘電体層16と、(c)一対の電極層15,17にそれぞれ接続された一対の引き出し電極30s,32;30t,34とを備える。一方の電極層15は、電極層15,17及び誘電体層16が積層された方向から透視したとき、(i)一対の電極層15,17が誘電体層16を介して対向する容量発生部に重なる中心部15pと、(ii)中心部から外側に延在し、かつ中心部を全周に渡って連続的に取り囲む外周部15qとを有する。一方の引き出し電極30sは、一方の電極層15の外周部15sに1箇所で接続され、当該接続面は中心部15pを全周に渡って連続的に取り囲む。

(もっと読む)

部品内蔵配線基板及びその製造方法

【課題】内蔵された部品と導体層とを確実に接続し、接続信頼性を向上させることができる部品内蔵配線基板の製造方法及び部品内蔵配線基板を提供する。

【解決手段】金属球7を外部電極121、122に接合して突設導体51を形成する突設導体形成工程と、キャパシタ101をコア基板11の収容穴部90に収容する収容工程と、キャパシタ101が収容されたコア基板11の収容穴部90内の間隙を絶縁性樹脂(樹脂充塞部92となる。)で充塞する樹脂充塞工程と、を備える。樹脂充塞工程の後に、複数の突設導体51の頂部と、コア基板11のコア裏面13等とが1つの平坦面に含まれるように高さを合わせる高さ合わせ工程を備えることが好ましい。

(もっと読む)

薄膜電子部品

【課題】ウェハ上に形成された複数の部品がウェハの切断によって個片化されて得られるものであっても、外部接続用の内部電極や配線が剥離等することなく切断面に確実に露出する薄膜電子部品を提供する。

【解決手段】薄膜インダクタ1は、ウェハ上に複数形成された単位構造がダイシングによって個片化されたものであり、面内中央部に突起部11が突設されたウェハWの環状の溝部12上に、絶縁層20内に埋め込まれるように、かつ、突起部11の周囲を巻回するように設けられたコイル22が形成されたものである。コイル22の内側端部24には、導体リード配線30が一方端が接続されており、その他方端側には、櫛形状をなす櫛部32が延出しており、櫛歯状に分割されたサブ電極35が側面Sに露出している。

(もっと読む)

電子部品内蔵配線基板

【課題】コンデンサの大容量化に対応しながら陽極接続端子部間に流れる高周波ノイズを除去する効果を向上させることができるとともに、基板の薄型化を実現する。

【解決手段】接続端子部は配線パターンおよびインダクタおよび/またはビア電極および/または貫通電極を介して固体電解コンデンサの弁金属シート体と少なくとも2箇所以上電気的に接続した陽極接続端子部と、前記配線パターンおよび/またはインダクタおよび/またはビア電極および/または貫通電極を介して前記固体電解コンデンサの集電体層と電気的に接続した陰極接続端子部とからなり、前記インダクタは導体パターン形状にて形成されたことを特徴とする電子部品内蔵配線基板である。

(もっと読む)

回路構成部品

【課題】プリント回路基板上に搭載された半導体LSIチップからの電磁波の漏洩を抑止し、シグナルインテグリティ(信号品質)と電力利用効率、ならびに回路設計効率を向上させ、、結果的にディジタル機器ならびにマルチメディア機器の高性能化と低コスト化を実現する。

【解決手段】 1枚の高誘電率高損失セラミック薄膜を絶縁体とし該薄膜を挟む2枚の金属薄膜を導体とするストリップ線路で構成され、1GHzにおいて0.5Ω以下の特性インピーダンスを有するとともに50Ωの線路に挿入したときに1GHzにおいて40dB以上の挿入損失を有する回路構成部品を形成し、該回路構成部品を半導体素子または半導体チップとともにプリント回路基板上に搭載し、前記半導体素子または半導体チップに直流電源を供給するプリント回路基板のライン側配線とグランド側配線を有する電源分配回路中の、あらかじめ途中で切断されたライン側配線を該回路構成部品によって再接続する。

(もっと読む)

金属箔上の大面積薄膜コンデンサ及びその製作方法

金属箔上で誘電体を作る方法が開示され、本方法から得られる金属箔上の誘電体を含んだ大面積コンデンサを作る方法が開示されている。誘電体の前駆体層及びベースメタル箔は、還元性ガスも含む湿潤雰囲気中で、350〜650℃の範囲内の予備焼成温度において予備焼成される。予備焼成された誘電体の前駆体層及びベースメタル箔はその後、誘電体を生成するために約10-6気圧未満の酸素分圧を有する雰囲気中で、700〜1200℃の範囲内の焼成温度において焼成される。本開示方法に従って作られるコンデンサの面積は10mm2を超え得る。そしてプリント配線板内に埋め込まれ得る複数の個々のコンデンサユニットを作製するために細分され得る。誘電体は、典型的には結晶質のチタン酸バリウム、又は結晶質のチタン酸バリウム・ストロンチウムを含む。  (もっと読む)

(もっと読む)

セラミック部品の製造方法

【課題】セラミック部品の外部電極上に突起状の導体を位置ズレがなく正確に形成することができるセラミック部品の製造方法を提供する。

【解決手段】フィルム設置工程において、感光性を有する厚さ200μmのフォトレジストフィルムをセラミック焼結体104上に設ける。直接露光工程において、直描露光機を用いてレーザ光を走査しながら照射してフォトレジストフィルムの露光を行う。現像工程において、露光されたフォトレジストフィルムを現像して、プレーン状電極111,112,121,122を露出させる開口部を有しためっきレジストを形成する。導体形成工程において、開口部を介して露出するプレーン状電極111,112,121,122に対してめっきを施すことにより、突起状導体50を形成する。

(もっと読む)

セラミックス膜およびその製造方法ならびに半導体装置、圧電素子およびアクチュエータ

【課題】セラミックス膜の表面モフォロジを改善することができる、セラミックス膜の製造方法を提供する。このセラミックス膜の製造方法により得られたセラミックス膜を提供する。このセラミックス膜が適用された半導体装置および圧電素子を提供する。

【解決手段】セラミックス膜の製造方法は、原材料体20を結晶化することにより、セラミックス膜30を形成する工程を含み、原材料体20は、種類が異なる原料を混在した状態で含み、種類が異なる原料同士は、原料の結晶化における結晶成長条件および結晶成長機構の少なくとも一方が相互に異なる関係にある。

(もっと読む)

薄膜コンデンサ及びその製造方法

【課題】高い静電容量を維持しつつ、ESRを低減することができる薄膜コンデンサ及びその製造方法を提供する。

【解決手段】本発明による薄膜コンデンサ1は、基体2上に設けられた複数のトレンチ3aが形成された絶縁層3と、トレンチ3aの内壁上及び絶縁層3上に形成された下部電極4と、下部電極4上に追従して形成された誘電体膜5と、誘電体膜5上に追従して形成された上部電極6と、2つのトレンチ3a間の絶縁層3を介して離間した下部電極4の部位同士、及び/又はトレンチ3aを介して離間した上部電極6の部位同士を連結する補助導体10と、を備える。

(もっと読む)

1 - 20 / 52

[ Back to top ]