Fターム[5E082FF05]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 誘電体及びその組合せ (1,937) | 固体誘電体 (1,792)

Fターム[5E082FF05]に分類される特許

1 - 20 / 1,792

フィルムコンデンサ用のフィルムおよびフィルムコンデンサ

積層セラミック電子部品

積層セラミックコンデンサ及びその製造方法

セラミック電子部品及びその製造方法

セラミック電子部品及びその製造方法

フィルムコンデンサ用樹脂組成物及びフィルムコンデンサ

セラミック電子部品及びその製造方法

誘電体磁器組成物およびセラミック電子部品

【課題】 誘電体層を薄層化した場合であっても、良好な特性を示す電子部品を提供すること。

【解決手段】セラミック粒子の内部がABO3(AはBa、CaおよびSrから選ばれる少なくとも1つであり、BはZr)を主成分として含有し、このセラミック粒子の表層部が、Ba及びTiとABO3が固溶した領域を有することにより、誘電率を下げることなく高温負荷寿命が長い誘電体磁器組成物を得た。この、誘電体磁器組成物を積層し焼成することにより、誘電率と高温負荷寿命を両立させた電子部品を製造することができる。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品及びその製造方法に関する。

【解決手段】誘電体層を含み、誘電体層の積層方向に互いに対向する第1及び第2主面、第1及び第2主面を連結し、互いに対向する長さ方向の第3、第4側面及び幅方向の第5、第6断面を有するセラミック本体と、セラミック本体内で誘電体層を挟んで互いに対向するように配置される第1及び第2内部電極と、第5断面上に形成され、第1内部電極と電気的に連結された一つ以上の第1外部電極及び第6断面上に形成され、第2内部電極と電気的に連結された一つ以上の第2外部電極と、を含んでおり、第1及び第2外部電極は、導電性金属及びガラスを含み、平均厚さが3〜30μmであり、第1及び第2外部電極のうち少なくとも一つを厚さ方向に3等分したときに、中央部領域の面積に対してガラスが占める面積が35〜80%である。

(もっと読む)

コンデンサ素子の乾燥方法およびコンデンサ素子の乾燥装置

【課題】コンデンサ素子の乾燥に要するエネルギーを削減する。

【解決手段】コンデンサ素子(43)の乾燥方法では、フィルム(44)を巻回してコンデンサ素子(43)を形成する素子形成工程と、素子形成工程で吸湿したコンデンサ素子(43)を100℃で加熱して乾燥させるための乾燥時間を設定する乾燥時間設定工程と、乾燥時間設定工程で設定された乾燥時間の間、100℃でコンデンサ素子(43)を加熱して乾燥する乾燥工程とを備えている。

(もっと読む)

蒸着重合膜形成装置及び蒸着重合膜の形成方法

【課題】蒸着重合膜を連続形成しつつ、蒸着重合膜の組成や膜厚の変化を把握できる蒸着重合膜形成装置を提供する。

【解決手段】赤外光源88と分光手段と検出器90と光学系92とを有する反射型赤外分光光度計86を設置すると共に、分光手段により分光された赤外光を蒸着重合膜上に集光させる集光鏡124と、蒸着重合膜上の集光点での反射光を更に反射させて、検出器90に導く反射鏡126,122,118とを、光学系92に設け、更に、集光鏡124を、基材フィルムの移送に伴って、蒸着重合膜上での赤外光の集光点の位置を基材フィルムの長さ方向に変化させ得る位置に配置して構成した。

(もっと読む)

高誘電率セラミックスの製造方法

【課題】ニッケル内部電極を使用した積層セラミックコンデンサに適用可能であり、かつ100nm未満の粒径のチタン酸アルカリ土類金属化合物を主原料としても誘電率が向上しうる高誘電率セラミックスの製造方法を提供する。

【解決手段】平均粒子径が50nm以上100nm未満であるチタン酸アルカリ土類金属化合物とランタン化合物とを混合する工程と、前記混合する工程で得られた混合物を、不活性ガス雰囲気下、1000℃以上1200℃未満の温度で焼成する工程と、を有し、前記ランタン化合物の混合量が、前記チタン酸アルカリ土類金属化合物に対するランタンの原子数換算で0.5〜1.5at%である、高誘電率セラミックスの製造方法。

(もっと読む)

金属化フィルムコンデンサ

【課題】コンデンサ素子を構成する金属化フィルムにヒューズ機能が設けられたフィルムコンデンサにおいて、安全性を損なうことなく、ヒューズ機能の作動による容量減少を最小限に抑えることを目的とする。

【解決手段】誘電体フィルムの長さ方向に並ぶように分割された複数の分割電極と、この分割電極と外部電極につながる第一の電極との間にヒューズ機能を持つ接続部を備え、この接続部は分割電極に少なくとも一つ以上設けられ、一つの分割電極に接続された接続部の誘電体フィルムにおける長さ方向の合計の寸法が、少なくとも二つ以上の異なる寸法となるように個々の分割電極に接続した構成とした。

(もっと読む)

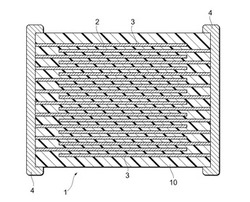

コンデンサとその製造方法

【課題】コンデンサ本体の積層構造が露出している端面に金属膜が密着しているコンデンサの量産効率を高める。

【解決手段】コンデンサ本体2の端面6に連なる側面を側面保護シート4で覆う。その際に、側面保護シート4が端面6の周囲を一巡しているとともに、端面6より突出している部分4eが形成されるようにする。次に、複数個のコンデンサ本体2を、側面同士が密着する関係で一列に並置する。次に、少なくとも側面同士が密着していない範囲の側面から突出している側面保護シートの突出部4c1,4d1の端縁4fの近傍をマスク10で覆い、その状態で端面6に金属を吹付ける。隣接するコンデンサ本体の端面6に形成される金属膜8は側面保護シートの突出部4eで分離され、コンデンサ本体2同士を容易に分離することができる。側面保護シートの突出部4eによって、端面6に吹付ける金属が露出している側面に到達して付着することもない。

(もっと読む)

チップ型電子部品

【課題】はんだ喰われを防止しつつ、応力緩和が可能な端子電極を有するチップ型電子部品を提供すること。

【解決手段】チップ型電子部品Cは、セラミック素体Lと、セラミック素体Lの内部に配置され、かつ、セラミック素体Lの表面に一部が露出した内部電極20と、セラミック素体の表面に配置された端子電極10とを含み、端子電極10は、第1の導電性材料12a、12bを含むとともに、内部電極の露出した部分および内部電極が露出しているセラミック素体の表面を覆う第1の電極層12と、第1の電極層12よりもセラミック素体の表面から離れた位置に配置される導電性めっき層14と、はんだ成分を含む第2の導電性材料16aと樹脂16cとを含むとともに、導電性めっき層14よりもセラミック素体の表面から離れた位置に配置される第2の電極層16と、を含む。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】めっき液の浸透を防止することでIRの低下を防止しながらも低いESL特性を有するようにした積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、複数の誘電体層が積層されたセラミック素体と、前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成され、前記セラミック素体の一面から露出するように延設された第1及び第2リード部をそれぞれ有する第1及び第2内部電極と、前記セラミック素体の一面に形成され、前記第1及び第2リード部の露出部により前記第1及び第2内部電極とそれぞれ電気的に接続される第1及び第2外部電極とを含み、前記第1又は第2外部電極の幅に対する前記第1又は第2リード部の幅の比が10〜85%である。

(もっと読む)

積層セラミック電子部品及びその製造方法

【課題】デラミネーション及びBDVの低下を防止しながらも低いESL特性を有するようにした積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、複数の誘電体層が積層されたセラミック素体と、前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成される本体部、及び前記本体部の一面で前記セラミック素体の一面から露出するように延設された第1及び第2リード部をそれぞれ含む第1及び第2内部電極とを含み、前記本体部と前記第1及び第2リード部の内側連結部が曲面に形成され、前記連結部の曲率半径が30〜100μmである。

(もっと読む)

金属化フィルムコンデンサ

【課題】優れた耐湿性と自己回復性を有する金属化フィルムコンデンサを提供する。

【解決手段】金属化フィルムコンデンサは、一対の金属化フィルム1、2の金属蒸着電極4a、4bのうち少なくとも一方は、金属蒸着電極膜を有しない非蒸着のスリットまたはマージン7a,7bにより大電極部9a,9bと分割小電極部10a,10bに区分され、アルミニウムとマグネシウムの合金電極であり、大電極部においてマグネシウムの原子濃度分布が最大となる構成とした。これによりマグネシウム添加合金化に伴うセルフヒーリング性減少を抑制でき、耐電圧減少を最小限にできる。

(もっと読む)

4端子型セラミックコンデンサ

【課題】 実装面積をより小さくすることができ、かつ、耐振動性を向上させることが可能な4端子型セラミックコンデンサを提供する。

【解決手段】 4端子型セラミックコンデンサ1は、直方体状のセラミックコンデンサ部10と、対向する側面10a,10bに形成された一対の電極20,21と、一対の電極20,21それぞれに接続されたヘアピン状のリード線30,31とを備える。リード線30(31)は、側面10a(10b)の長手方向に伸びる一対の直線部30a,30b(31a,31b)と、該一対の直線部30a,30b(31a,31b)の端部同士を滑らかに接続する湾曲部30c(31c)とを含む。一方の直線部30a(31a)は電極20(21)に接続され、他方の直線部30b(31b)は電極20(21)と離間して設けられ、湾曲部30c(31c)は、平面視した場合に、側面10a(10b)に対して垂直な方向に伸びる。

(もっと読む)

積層セラミックコンデンサ

【課題】積層セラミックコンデンサの、基板上への実装状態での電界印加時における「鳴き」を抑制する。

【解決手段】コンデンサ本体29における内部電極27,28の対向による静電容量形成に寄与する活性部37を、積層方向に沿って分布する第1領域40と基板22側の第2領域41とに区分し、第2領域41における誘電体セラミック層25の誘電率を、第1領域40における誘電体セラミック層24の誘電率より低くし、かつ第2領域41における誘電体セラミック層25の体積に対する内部電極27,28の体積の比率を、第1領域40における誘電体セラミック層24の体積に対する内部電極27,28の体積の比率より高くする。

(もっと読む)

1 - 20 / 1,792

[ Back to top ]