Fターム[5E319BB07]の内容

印刷回路に対する電気部品等の電気的接続 (35,455) | 接続材料 (4,656) | 形状、性質又は組成が特定されているはんだ (3,830) | Pb−Snのみを含有するはんだ (36)

Fターム[5E319BB07]に分類される特許

1 - 20 / 36

リフローフィルム、はんだバンプ形成方法、はんだ接合の形成方法及び半導体装置

【課題】はんだ成分を自己組織化により基板の電極上に偏在させることにより、保存性、運搬性、及び使用時のハンドリング性に優れ、電極のみに対して選択的にはんだバンプ又ははんだ接合を形成することができるリフローフィルムを提供し、さらにこれを用いたはんだバンプ又ははんだ接合の簡便な形成方法、これにより形成されたボイドが少なく高さばらつきが少ないはんだバンプ及びはんだバンプ付き基板を提供する。

【解決手段】溶媒に溶解可能な熱可塑性樹脂と、はんだ粒子とを含むフィルムであって、前記はんだ粒子は前記フィルム中に分散した状態であることを特徴とするリフローフィルム、および(ア)基板の電極面側に前記リフローフィルムを載置する工程、(イ)さらに平板を載置して固定する工程、(ウ)加熱する工程、及び(エ)前記リフローフィルムを溶解除去する工程を含むはんだバンプ形成方法。

(もっと読む)

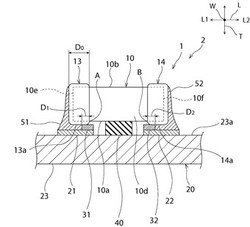

電子部品の実装構造及び電子部品の実装方法

【課題】電子部品が損傷しにくい電子部品の実装構造及び電子部品の実装方法を提供する。

【解決手段】電子部品1の実装構造2は、第1のソルダーレジスト層31と、第2のソルダーレジスト層32と、第1のランド電極21の第1のソルダーレジスト層31よりも長さ方向Lの一方側部分と第1の外部電極13とを接続している第1のはんだ層51と、第2のランド電極22の第2のソルダーレジスト層32よりも長さ方向Lの他方側部分と第2の外部電極14とを接続している第2のはんだ層52とをさらに備えている。第1のソルダーレジスト層31は、第1のランド電極21の上において、第1の外部電極13の長さ方向Lの他方側端部の下方に位置するように配されている。第2のソルダーレジスト層32は、第2のランド電極22の上において、第2の外部電極14の長さ方向Lの一方側端部の下方に位置するように配されている。

(もっと読む)

はんだ接続用通電部材、配線用基板及びめっき皮膜の形成方法

【課題】CuまたはCu合金からなる通電部材(電極端子)に、Cu成分を含有しないはんだを使用しても、通電部材側とはんだとが十分な接合強度を発現するはんだ接続用通電部材、配線用基板及びめっき皮膜の形成方法を提供する。

【解決手段】CuあるいはCu合金を含む通電部材1上に、ピンホール7を有する置換Snめっき皮膜5と、電解Niめっき皮膜4と、電解Pdめっき皮膜3と、電解Auめっき皮膜2と、がこの順に積層されているはんだ接続用通電部材である。

(もっと読む)

半田材および半導体装置

【課題】凝固収縮割れの発生を抑制できる半田材およびその半田材が用いられた半導体装置を提供する。

【解決手段】半田材4は、固相線の直上の温度における固相率が30%以上となる組成を有する。

(もっと読む)

配線基板

【課題】コンデンサ素子接続パッド間で電気的な短絡が発生することがなく、搭載する半導体素子を正常に作動させることが可能な配線基板を提供すること。

【解決手段】上面中央部に半導体素子搭載部1aを有する絶縁基板1の半導体素子搭載部1a周辺の上面にコンデンサ素子Cの電極T2が半田B3を介して接続される少なくとも一対のコンデンサ素子接続パッド5a,5bが、半導体素子搭載部1aに近い側の第一のコンデンサ素子接続パッド5aと半導体素子搭載部1aから遠い側の第二のコンデンサ素子接続パッド5bとに分かれて配置されている配線基板10であって、第一のコンデンサ素子接続パッド5aは、半導体素子搭載部1aに沿う方向の長さL1がコンデンサ素子Cの半導体素子搭載部1aに沿う方向の長さL3よりも短い。

(もっと読む)

銅または銅合金の表面処理剤及びその利用

【課題】半田を使用して電子部品等をプリント配線板に接合する際に、プリント配線板の回路部等を構成する銅または銅合金の表面に、耐熱性および半田との濡れ性に優れた化成皮膜を形成させることによって、半田付け性を良好なものとする表面処理剤、表面処理方法、プリント配線板ならびに半田付け方法を提供する。

【解決手段】特定のイミダゾール化合物を含有することを特徴とする表面処理剤を用いて銅または銅合金の表面を処理する。

(もっと読む)

配線基板の製造方法

【課題】配線基板上に、加熱溶融条件の異なる複数種類のはんだバンプを形成する場合に、各々のはんだバンプを良好に形成する。

【解決手段】配線基板の本体部の表面をなす複数の電極パッド上にはんだバンプが設けられた配線基板の製造方法は、複数の電極パッドの内、一部の電極パッド上で開口する開口部を有すると共に、他の電極パッドを覆うマスクを準備する第1の工程と、マスクを配線基板の本体部表面側に配置し、マスクの開口部を介して外部に露出する一部の電極パッド上に、はんだ材料を含有するバンプ形成部を形成する第2の工程と、バンプ形成部を加熱溶融処理して、バンプ形成部から第1のはんだバンプを形成する第3の工程と、他の電極パッドの各々に対して、加熱溶融したはんだ材料を吐出供給し、第2のはんだバンプを形成する第4の工程と、を備える。

(もっと読む)

フラックス、はんだペースト及び実装基板の製造方法

【課題】はんだペーストのリフロー時におけるに優れ、ボイドの発生が少なく接合強度に優れたはんだペースト用のフラックスを提供する

【解決手段】Pb及びSnを含有するはんだ合金粉末と混合されてはんだペーストを形成するフラックスであって、前記はんだペーストの融点より低い温度領域である135〜165℃での前記フラックスのイオン伝導率の最大値が0.05mS/m以上であり、且つ前記融点を含む温度領域である183〜220℃での前記フラックスのイオン伝導率が0.03mS/m以下である。

(もっと読む)

フラックス、はんだペースト及び実装基板の製造方法

【課題】はんだペーストの保管時及び取り扱い時における粘度上昇等の経時変化が少なく塗布性に優れ、濡れ性にも優れたはんだペースト用のフラックスを提供する。

【解決手段】Pb及びSnを含有するはんだ合金粉末と混合されてはんだペーストを形成するフラックスであって、はんだペーストが保管ないし取扱われる常温域のイオン伝導率が0.002mS/m以下であり、且つリフローされる高温域のイオン伝導率が0.02mS/m以上である。

(もっと読む)

扁平はんだグリッド配列のための処理方法、装置及びコンピュータシステム

【課題】プリント回路基板表面実装部品のための扁平はんだグリッド配列を提供する。

【解決手段】スタンドオフ接触配列は、フリップフロップパッケージの実装基板とボードとの間に配置される(410)。このスタンドオフ接触配列は、実装基板上の扁平なはんだバンプをボード上の扁平なはんだペーストと結合する(430)ことによって、形成可能である。その後に、スタンドオフ接触配列は、実装基板上の扁平なはんだバンプに対してボード上の扁平なはんだペーストをリフローする(440)ことによって、形成される。

(もっと読む)

回路装置およびその製造方法

【課題】半田のヒケの発生を抑止して半田接合部の接続信頼性を向上させた回路装置およびその製造方法を提供する。

【解決手段】本形態の回路装置の製造方法では、先ず、パッド18Aの上面に複数個の離間した半田19を形成し、同時にチップ部品14Bおよびトランジスタ14Cを固着する。次に、シリンジ30を用いてパッド18Aの上面に半田ペースト31を供給して、この半田ペースト31の上部にヒートシンク14Dを載置し、リフロー工程により溶融する。本発明では、パッド18Aの上面に離散的に半田19を配置しているので、半田19がヒケる恐れが小さい。

(もっと読む)

配線基板の製造方法

【課題】導体層及び樹脂絶縁層が交互に積層されるとともに、第1の主面側とこの第1の主面と相対する第2の主面側の最表面にソルダーレジスト層が形成され、前記ソルダーレジスト層に形成された開口部から前記導体層が露出してなる配線基板において、導体層と半田バンプ等との密着性を改善した新規な配線基板の製造方法を提供する。

【解決手段】配線基板の最表面のソルダーレジスト層に形成された開口部から露出した導体層上に、Snを含む下地層を形成する。次いで、下地層のうち第1の主面側に位置する第1の下地層及び第1の主面と相対向する第2の主面側に位置する第2の下地層上に、それぞれ第1の半田及び第2の半田を供給する。次いで、第1の半田及び第2の半田を同時に加熱して、それぞれ第1の下地層及び第2の下地層と接続する。

(もっと読む)

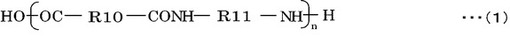

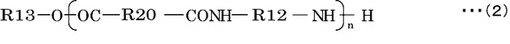

ソルダペーストおよびフラックス

【課題】リフローハンダ付け法において、加熱だれを抑制することができるソルダペーストおよびフラックスを提供する。

【解決手段】ソルダペーストは、ハンダ粉末と、樹脂成分、溶剤成分、活性剤、チキソ剤および添加剤を含むフラックスとを含む。添加剤は、式(1)または式(2)に示す加熱だれ抑制成分を含む。

【化1】

(式中、R10は炭素数14以上の脂肪族炭化水素基である。R11は炭化水素基である。)

【化2】

(式中、R12は炭化水素基である。R13は炭化水素基である。R20は炭素数14以上の脂肪族炭化水素基である。)

(もっと読む)

電子装置の製造方法及び電子装置

【課題】温度変化が激しい環境下において、半田接合部に発生する応力を低減することができる電子装置の製造方法及び電子装置を提供することを目的とする。

【解決手段】電子装置の製造方法が、電子部品がプリント基板に半田付けされている電子装置の製造方法であって、前記電子部品と前記プリント基板との間に台材を配置して半田付けすることで、前記半田の厚さを作り出す半田厚生成工程を具備する。

(もっと読む)

透明の基板の上にデバイスを導電性結合する方法

本発明は、少なくとも1つの導電性層と電気デバイスを導電性結合する方法に関するものであり、導電性層は光の可視波長領域で実質的に透明の基板に塗布され、次の各ステップを含んでおり、すなわち、電気デバイスまたは導電性層にデバイスが導電性層と結合されるべき領域ではんだ材料が施され、はんだ材料にエネルギー源から放出されるエネルギーが供給され、それにより、はんだ材料が溶融し、取外し可能でない物質接合式の導電性結合が電気デバイスと導電性層との間に構成される。 (もっと読む)

単一プリント回路板のはんだバンプ印刷方法

【課題】単一プリント回路板のはんだバンプ印刷方法を提供する。

【解決手段】本発明は、単一プリント回路板のはんだバンプ印刷方法を提供し、完成した内部回路を含むプリント回路板全板を提供するステップと、プリント回路板全板を複数の独立した単一プリント回路板に分割するステップと、単一プリント回路板に電子テストを実行するステップと、複数のはんだバンプを単一プリント回路板中に形成するステップと、からなる。

(もっと読む)

配線基板および配線基板の判別方法

【課題】配線基板に半田付けされた半田が鉛半田と鉛フリー半田のどちらであるかを判別可能な配線基板を提供することを目的とする。

【解決手段】塗布された半田ペーストが加熱されて半田付けされる配線基板において、半田付けされた半田が鉛を含有する鉛半田と鉛を含有しない鉛フリー半田のどちらであるかを判別するための判別用ランド2を備え、半田ペーストを判別用ランド2に塗布して加熱し、半田ペーストを判別用ランド2に溶融・固化するとともに、判別用ランド2に塗布する半田ペーストの塗布領域21を、半田ペーストが鉛フリー半田の半田ペーストである場合に、判別用ランド2に溶融・固化される鉛フリー半田が判別用ランドより狭くなる領域とする。これにより、判別用ランド2において塗布領域21に塗布して溶融・固化した半田の広さから、配線基板に半田付けされた半田が鉛半田と鉛フリー半田のどちらであるかを判別できる。

(もっと読む)

位置合わせ性に優れたはんだペーストを用いた基板と被搭載物の接合方法

【課題】はんだペーストを用いて基板に対して被搭載物を同じ位置および方向となるように接合する方法を提供する。

【解決手段】メタライズ層を形成した基板におけるメタライズ層とメタライズ層を形成した正方形状を有する被搭載物4におけるメタライズ層との間にはんだペースト3を搭載または塗布したのちリフロー処理して基板と正方形状を有する被搭載物4をはんだペーストを用いた基板と正方形状を有する被搭載物を接合する際に、前記基板の表面に形成されるメタライズ層の面積が被搭載物4のメタライズ層の面積よりも小さいメタライズ層本体部分6と前記メタライズ層本体部分6の周囲から突出した少なくとも2個のはんだ誘引部メタライズ層7とからなる平面形状を有していると、リフロー処理中に正方形状の被搭載物4の対角線と前記はんだ誘引部メタライズ層7の突出方向とが一致するように回転してはんだ付けされる。

(もっと読む)

位置合わせ性に優れたはんだペーストを用いた基板と被搭載物の接合方法

【課題】はんだペーストを用いて基板に対して被搭載物を同じ位置および方向となるように接合する方法、特にAu−Sn合金はんだペーストを用いて基板に対して素子を同じ位置および方向となるように接合する方法を提供する。

【解決手段】メタライズ層を有する基板のメタライズ層とメタライズ層を有する被搭載物のメタライズ層との間にはんだペースト3を搭載または塗布したのち非酸化性雰囲気中でリフロー処理して基板と被搭載物を接合するはんだペーストを用いた基板と被搭載物の接合方法において、前記基板のメタライズ層を図1(a)のように面積が被搭載物4のメタライズ層の面積よりも小さいメタライズ層本体部分6と前記メタライズ層本体部分6の周囲から突出したはんだ誘引部7とからなる平面形状を有するようにすると、被搭載物が図1(b)の如くはんだ誘引部7の方向に揃ってはんだ付けされる。

(もっと読む)

ソルダペースト

【課題】はんだ粉末とフラックスの反応により、水や水素などのガスが発生する。はんだが溶融するとき、このガスおよびフラックス中の溶媒ガスおよびフラックス自体が取り込まれてしまい、ボイドと呼ばれる、はんだの中に空間が生じる。このボイドの発生を防止したソルダペーストを提供する。

【解決手段】はんだ合金粉末と、接合面およびはんだ合金粉末の酸化物を除去清浄化するためのフラックスとからなるソルダペーストにおいて、吸着剤Aを必須成分とする。

(もっと読む)

1 - 20 / 36

[ Back to top ]