Fターム[5E319CC33]の内容

印刷回路に対する電気部品等の電気的接続 (35,455) | 接続方法 (5,332) | 溶接方法 (4,641) | はんだ付け (4,215) | リフローはんだ付け (2,794)

Fターム[5E319CC33]の下位に属するFターム

プリント回路板の全体加熱 (275)

プリント回路板の局所加熱 (358)

Fターム[5E319CC33]に分類される特許

201 - 220 / 2,161

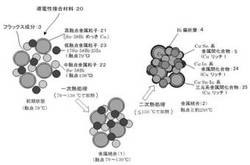

導電性接合材料、導体の接合方法、及び半導体装置の製造方法

【課題】導電性接合材料を基板の電極に供給しつつ溶着する導電性接合材料供給工程、及び電子部品の端子に導電性接合材料を一度溶融させて転写する転写工程を選択することができ、基板と電子部品を150℃以下の低温で効率よく接合することができる導電性接合材料及び導体の接合方法、及び半導体装置の製造方法の提供。

【解決手段】融点が150℃以上の高融点金属粒子と、融点が80℃以上139℃以下の中融点金属粒子と、融点が79℃以下の低融点金属粒子とからなる金属成分を含む導電性接合材料である。前記金属成分が、高融点金属粒子表面に、中融点金属粒子から形成された中融点金属層と、低融点金属粒子から形成された低融点金属層とをこの順に有する多層金属粒子である態様などが好ましい。

(もっと読む)

多層配線基板

【課題】導体層及び樹脂絶縁層が交互に積層されてなるビルドアップ層と、少なくとも1層の樹脂絶縁層の表面上において、表面から突出して形成された導電性パッドと、導電性パッドの上面において形成されたはんだ層とを備える多層配線基板において、導電性パッドへの応力集中を抑制し、半導体素子との接続不良及び導電性パッドの破損を抑制する。

【解決手段】導体層及び樹脂絶縁層が交互に積層されてなるビルドアップ層と、前記樹脂絶縁層の表面から突出して形成され、下部に位置する円柱部及び上部に位置する凸部からなる導電性パッドと、を備え、前記導電性パッドの前記凸部の表面は、連続した曲面形状であるようにして多層配線基板を構成する。

(もっと読む)

電子部品実装ラインおよび電子部品実装方法

【課題】異種類の基板を含めた複数枚の基板を対象として同時並行的に印刷作業を効率よく実行する電子部品実装ラインおよび電子部品実装方法を提供する。

【解決手段】電子部品搭載装置3の上流に2つのスクリーン印刷部7A,7Bをそれぞれ直列に配置して成る2列のスクリーン印刷ラインを並設したスクリーン印刷システムを連結して構成された電子部品実装ラインにおいて、2列のスクリーン印刷ラインは、スクリーン印刷システムの中心側にそれぞれのバイパス用の基板搬送路8を並列に配置し、それぞれのスクリーン印刷部7A、7Bを基板搬送路8の外側に配置した構成とする。これにより、下流側装置から当該スクリーン印刷装置の上流側へ基板5を戻すためのリターン搬送および上流側から送られた基板5を当該スクリーン印刷装置を通過させて下流側装置へ搬送するためのバイパス搬送など必要に応じて多様な基板搬送形態が可能となる。

(もっと読む)

フラックスおよび電気的接続構造の形成方法

【課題】本発明は、電気的接続構造を形成する際、有機系の絶縁膜への影響が少ないフラックスを提供することを目的とする。

【解決手段】アルカノールアミン、脂肪族カルボン酸およびこれらの塩から選ばれる少なくとも1種以上を含有するフラックスであって、アルカノールアミン、脂肪族カルボン酸及び前記塩の合計含有割合がフラックス全量の80質量%以上であることを特徴とするフラックス。

(もっと読む)

フラックス、はんだペースト及び実装基板の製造方法

【課題】はんだペーストの保管時及び取り扱い時における粘度上昇等の経時変化が少なく塗布性に優れ、濡れ性にも優れたはんだペースト用のフラックスを提供する。

【解決手段】Pb及びSnを含有するはんだ合金粉末と混合されてはんだペーストを形成するフラックスであって、はんだペーストが保管ないし取扱われる常温域のイオン伝導率が0.002mS/m以下であり、且つリフローされる高温域のイオン伝導率が0.02mS/m以上である。

(もっと読む)

発振器

【課題】 簡易な構成で安価に温度変化に伴う半田クラックの発生を抑制し、耐ヒートサイクル性能を向上させることができる発振器を提供する。

【解決手段】 エポキシ樹脂の基板1と、基板1上の搭載される電子部品2とを備える発振器であって、電子部品2の端子電極3に半田5により接続する2端子の電極パターン4が基板1上に形成され、電極パターン4の端子電極3に接続する部分に突起部6を形成し、端子電極3と電極パターン4との間に空間を形成し、当該空間に半田5のフィレット形状を形成するようにしているので、半田5の接着強度を高めることができる発振器である。

(もっと読む)

回路モジュール、電子部品実装基板および回路モジュールの製造方法

【課題】 回路モジュールの製造方法において、現状の材料、プロセスを活用して、はんだの接合信頼性を向上すること。

【解決手段】回路モジュールは、片側の面に半導体素子が搭載され対向する面には半導体素子に繋がる複数の電極パッドが形成されている半導体素子搭載基板と、片側の面に接地層を介して開口部を有するソルダーレジスト層が形成されている回路基板と、半導体素子搭載基板の電極パッドと回路基板の接地層を接合するはんだボールを備えている。接地層は、ソルダーレジスト層に被覆され第1の膜厚を有する第1の電極部分と、第1の電極部分と連続しかつソルダーレジスト層の開口部の内側に設けられ第1の電極部分よりも膜厚が厚い第2の電極部分から構成され、はんだボールは第2の電極部分と半導体素子搭載基板の電極パッドを接合しているものである。

(もっと読む)

フラックス、はんだペースト及び実装基板の製造方法

【課題】はんだペーストのリフロー時におけるに優れ、ボイドの発生が少なく接合強度に優れたはんだペースト用のフラックスを提供する

【解決手段】Pb及びSnを含有するはんだ合金粉末と混合されてはんだペーストを形成するフラックスであって、前記はんだペーストの融点より低い温度領域である135〜165℃での前記フラックスのイオン伝導率の最大値が0.05mS/m以上であり、且つ前記融点を含む温度領域である183〜220℃での前記フラックスのイオン伝導率が0.03mS/m以下である。

(もっと読む)

配線基板及びその製造方法

【課題】樹脂による補強を行う場合に、製造工程を簡易化でき、特に端子部材にソケット等の接続部材を装着する場合には、接続部材の装着を確実に行うことができる配線基板及びその製造方法を提供すること。

【解決手段】PGA用端子パッド21上に端子ピン15の基台63を配置するとともに、PGA用端子パッド21上に半田と樹脂製の電気絶縁材とを含む接合材ペースト85を配置し、その接合材ペースト85を加熱することによって、半田を溶融させるとともに電気絶縁材を軟化させる。そして、その後冷却することによって、半田を固化させて基台63とPGA用端子パッド21を接合するとともに、基台63に接合した半田接合部70の露出面に電気絶縁表面層72を形成する。

(もっと読む)

はんだ付け方法

【課題】プリント配線板に電子部品をはんだ付け実装する場合に、はんだボールの発生を防止し、高品質なはんだ付け実装を実現する。

【解決手段】プリント配線板1のパッド1a上にはんだ3を塗布するはんだ塗布ステップと、はんだ3を塗布したプリント配線板1を加熱し、当該はんだ3を溶融硬化させるはんだ溶融硬化ステップと、はんだ3を溶融硬化させたプリント配線板1を洗浄し、パッド1aからはみ出した不要物を除去する洗浄ステップと、不要物を除去したプリント配線板1の溶融硬化はんだコート6上にフラックス8を塗布するフラックス塗布ステップと、フラックス8を塗布したプリント配線板1に部品2を搭載し、当該プリント配線板1を加熱して部品実装を行う部品実装ステップとを有する。

(もっと読む)

ハンダ粉末及びこの粉末を用いたハンダ用ペースト

【課題】ファインピッチ化を実現するハンダ用ペーストに好適な微細なハンダ粉末であって、リフロー時の溶融拡散性が良く、ハンダバンプ形成時の組成制御が容易であり、濡れ性に優れた、ハンダ粉末及びこの粉末を用いたハンダ用ペーストを提供する。

【解決手段】中心核11と中心核11を被覆する被覆層12で構成される平均粒径5μm以下のハンダ粉末10において、中心核11が銀、銅、ニッケル、インジウム、コバルト又は金を成分とする金属元素核11aと、この金属元素核11aの外周に金属元素と錫との金属間化合物層11bを有する2層構造からなり、被覆層12が錫からなることを特徴とする。

(もっと読む)

はんだ、はんだ付け方法及び半導体装置

【課題】延性が高く、長期間にわたり十分な接合強度を維持できるPbフリーはんだ、そのはんだを用いた半導体装置及びはんだ付け方法を提供する。

【解決手段】Sn(スズ)、Bi(ビスマス)及びZn(亜鉛)を含み、Znの含有量が0.01wt%乃至0.1wt%であるはんだを使用する。例えばBi含有量が45wt%〜65wt%、Zn含有量が0.01wt%乃至0.1wt%、残部がSnからなるはんだ、又はBi含有量が45wt%〜65wt%、Sb(アンチモン)含有量が0.3wt%〜0.8wt%、Zn含有量が0.01wt%乃至0.1wt%、残部がSnからなるはんだを使用し、電子部品と基板とを接合する。

(もっと読む)

ハンダ粉末及びこの粉末を用いたハンダ用ペースト

【課題】ファインピッチ化を実現するハンダ用ペーストに好適な微細なハンダ粉末であって、リフロー時の溶融拡散性が良く、ハンダバンプ形成時の組成制御が容易であり、濡れ性に優れた、ハンダ粉末及びこの粉末を用いたハンダ用ペーストを提供する。

【解決手段】中心核11と中心核11を被覆する被覆層12で構成される平均粒径5μm以下のハンダ粉末10において、中心核11が銀、銅、ニッケル、インジウム、コバルト又は金を成分とする金属元素と錫との金属間化合物からなり、被覆層12が錫からなることを特徴とする。

(もっと読む)

実装方法

【課題】回路基板の実装面に設けられた実装用ランドの面積を大きくせずとも、十分な量のはんだペーストを供給して、電子部品と回路基板との間のはんだ不足による接続不良を低減することのできる技術を提供する。

【解決手段】電子部品の複数のバンプ接続用はんだボール電極にはんだペーストを転写により塗布すると共に、実装面1aの凹んでいる部分や、内部電極パターン5の積層方向における配線密度が小さく回路基板1の厚みが薄くなって窪みが生じるおそれのある部分、回路基板1または電子部品の反りにより回路基板1および電子部品間の間隔が大きい位置に設けられた実装用ランド2に、はんだペーストを塗布することにより、回路基板1の実装用ランド2の面積を大きくせずとも十分な量のはんだペーストを供給して、電子部品と回路基板1との間のはんだ不足による接続不良を低減することができる。

(もっと読む)

電子部品実装用配線基板の製造方法、電子部品実装用配線基板、及び電子部品付き配線基板の製造方法

【課題】電子部品と配線基板とを半田の再溶融によって接続する場合に、隣接する半田同士の接続を防止できる電子部品実装用配線基板の製造方法、電子部品実装用配線基板、及び電子部品付き配線基板の製造方法を提供すること。

【解決手段】チップ実装用端子パッド17上に半田と樹脂製の電気絶縁材とを含む接合材ペースト85を配置し、接合材ペースト85を加熱することによって、半田を溶融させるとともに電気絶縁材を軟化させる。その後、半田を固化させて半田バンプ9を形成するとともに、電気絶縁材を半田バンプ9の表面及び半田バンプ9の周囲の積層基板5の表面にて硬化させて電気絶縁表面層45を形成する。従って、この構造の半田バンプ9を備えた実装用配線基板1にICチップ3を実装する際に、半田を再溶融させた場合には、電気絶縁表面層45によって、隣合う半田バンプ9同士が接続し難いという利点がある。

(もっと読む)

配線基板およびその実装構造体

【課題】本発明は、実装構造体の電気的接続信頼性を向上させる要求に応える配線基板およびその実装構造体を提供するものである。

【解決手段】本発明の一形態にかかる配線基板は、交互に積層された複数の絶縁層13および導電層14を備え、複数の絶縁層13は、最外層に位置する第1絶縁層13aと、該第1絶縁層13aに接している第2絶縁層13bとを有し、導電層14は、第1絶縁層13aと第2絶縁層13bとの間に配された接続パッド18を有し、第1絶縁層13aは、厚み方向に貫通して接続パッド18を露出する貫通孔Pを具備し、接続パッド18は、貫通孔Pの開口部に向かって突出した突起部20とを具備する。

(もっと読む)

回路基板及び電子装置

【課題】開示の技術によれば、回路基板の表面に形成される保護膜の膜厚の抑制と、該保護膜による回路基板の表面保護と、を実現しつつ、電極パッドに供給される半田ペーストを増加することができる。

【解決手段】

少なくとも電子部品がハンダ接続により搭載される電極パッド領域を除き表面保護膜が形成された回路基板であって、上記表面保護膜は多層で構成され、上記電極パッド領域の開口面積が下層から上層に向かって拡大する部分を有する回路基板。

(もっと読む)

電子装置

【課題】回路基板に電子部品をはんだ実装してなる電子装置において、回路基板とこの回路基板にはんだ接合された電子部品との両者の膨張・収縮度合の差をより小さくすることで、はんだへの応力を低減させる。

【解決手段】回路基板10の方が電子部品20よりも線膨張係数が大きいものであり、電子部品20は、第1の電極21、第2の電極22にてそれぞれ、回路基板10にはんだ30を介して固定されており、回路基板10のうち第1の電極21との固定部と、第2の電極22との固定部との間に位置する部位である固定部間部位13は、一面11に貫通穴14が設けられることにより、回路基板10のうち固定部間部位13以外の部位よりも熱膨張および熱収縮の度合が小さくなっている。

(もっと読む)

ハンダ粉末及びその製造方法

【課題】金属粒子の構造上の不均一性から生じる組成ズレを抑制することにより、リフロー時の溶融性を大幅に改善させたハンダ粉末及びその製造方法を提供する。

【解決手段】中心核31と中心核31を被覆する中間層32と中間層32を被覆する最外層33で構成される金属粒子30からなる平均粒径5μm以下のハンダ粉末において、中心核21が銀、銅、ビスマス、ゲルマニウム、ニッケル、インジウム、金又はコバルトのいずれか1種の金属からなり、中間層32が中心核31の金属とは異なる銀、銅、ビスマス、ゲルマニウム、ニッケル、インジウム、金又はコバルトのいずれか一種の金属からなり、最外層33が錫からなり、金属粒子30の体積を100%とするときの中心核31、中間層32、最外層33の各体積割合をVc%、Vm%、Vo%とするとき、Vc<Vm<Voの関係を満たし、錫の含有割合が85〜99.8質量%であることを特徴とする。

(もっと読む)

半導体装置および半導体装置実装体

【課題】複数の差動信号を伝送する半導体装置の信頼性低下を抑制する。

【解決手段】複数の差動信号を伝送する複数のランド(第1外部端子)LDp1を含む複数のランド(外部端子)LDpが、配線基板12の裏面12bに行列状の配列パターンで配置されたエリアアレイ型の半導体装置10を以下の構成とする。複数のランドLDp1の一部は、配列パターンの最外周に配置される。また、複数のランドLDp1の他の一部は、配線基板12の裏面12bにおいて、配列パターンの最外周よりも内側で、かつ、最外周の隣の列に配置される。ここで、最外周の隣の列に配置されるランドLDp1と、配線基板12の側面の間の第2領域R2では、複数のランドLDpの配置間隔が、最外周の第1領域R1よりも広くなっている。

(もっと読む)

201 - 220 / 2,161

[ Back to top ]