Fターム[5E336AA04]の内容

プリント板への電気部品等の実装構造 (16,219) | 電気部品等の実装構造 (3,097) | 表面実装 (1,230)

Fターム[5E336AA04]の下位に属するFターム

挿入実装と表面実装との併用 (39)

Fターム[5E336AA04]に分類される特許

1 - 20 / 1,191

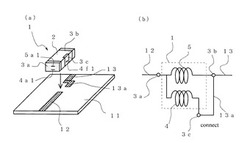

ノイズ対策電子部品の回路基板への実装構造

【課題】 実装箇所に応じたノイズ対策電子部品を複数用意する必要が無くなり、ノイズ対策の検討を容易迅速に行うことが可能なノイズ対策電子部品の実装構造を提供する。

【解決手段】 インダクタ1の実装する部品側面を底面にして第1の接続状態にすることで、第2のコイル4の他端の引出電極4f1が第3の外部電極3cおよび短絡用配線パターン13aを介して他方の外部電極3bに接続される。このため、コイル4,5は、各一端が一方の外部電極3aに共通接続され、各他端が他方の外部電極3bに共通接続されて、並列接続される。従って、インダクタ1の抵抗成分は小さくなる。一方、インダクタ1の実装する部品側面を異ならせて天面にし、第2の接続状態にすることで、第3の外部電極3cは電気的に浮き、第2のコイル4の他端も浮いた状態になる。このため、インダクタ1のインピーダンスは第1のコイル5が有するものとなって高くなる。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体素子

【課題】はんだによる短絡不良を低減すること。

【解決手段】半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。各々の電極端子13の中心軸L1は、電極パッド11の中心から、電極パッド11の配列方向と直交する方向に沿って半導体素子10の外側にずれた位置に形成されている。半導体素子10が実装される配線基板20には、半導体素子10の電極パッド11と対応する複数の接続パッド22が形成されている。各接続パッド22の中心L2は、半導体素子10の電極パッド11の中心と略一致する。また、各接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。電極端子13は接続パッド22にはんだ30により電気的に接続される。

(もっと読む)

ケーブルモジュールおよびその製造方法

【課題】半田接続作業においてケーブルの折れ等が発生しにくい構造を有するケーブルモジュールを提供する。また、半田接続作業においてケーブル折れ等の発生を抑制することができるケーブルモジュールの製造方法を提供する。

【解決手段】ケーブルモジュール1は、配線基板10と、複数のケーブルとを備えている。配線基板10に形成された接続端子12のうちで、外径が最も小さいケーブルに対応する接続端子12は接続端子列13の端に配置されている。そして、各ケーブルは対応する各接続端子12に接続されている。

(もっと読む)

リフローフィルム、はんだバンプ形成方法、はんだ接合の形成方法及び半導体装置

【課題】はんだ成分を自己組織化により基板の電極上に偏在させることにより、保存性、運搬性、及び使用時のハンドリング性に優れ、電極のみに対して選択的にはんだバンプ又ははんだ接合を形成することができるリフローフィルムを提供し、さらにこれを用いたはんだバンプ又ははんだ接合の簡便な形成方法、これにより形成されたボイドが少なく高さばらつきが少ないはんだバンプ及びはんだバンプ付き基板を提供する。

【解決手段】溶媒に溶解可能な熱可塑性樹脂と、はんだ粒子とを含むフィルムであって、前記はんだ粒子は前記フィルム中に分散した状態であることを特徴とするリフローフィルム、および(ア)基板の電極面側に前記リフローフィルムを載置する工程、(イ)さらに平板を載置して固定する工程、(ウ)加熱する工程、及び(エ)前記リフローフィルムを溶解除去する工程を含むはんだバンプ形成方法。

(もっと読む)

電子素子及び/又は電気素子のための回路装置

【課題】従来技術の欠点が改善された回路装置を提供すること。

【解決手段】少なくとも1つの電子素子及び/又は電気素子(30,30’)と、支持体(10,10’)とを有する回路装置であって、

前記少なくとも1つの電子素子及び/又は電気素子は、該電子素子及び/又は電気素子と前記支持体との間に空気層(LS,LS’)を形成しつつ、少なくとも1つのはんだ層(40,40’)を介して前記支持体と導電的に接続されている、

回路装置において、

前記支持体の中に少なくとも1つの3次元収容構造(20,20’)が組み込まれており、

前記3次元収容構造内にて、該3次元収容構造の少なくとも2つのコンタクト領域(22,22’)の間に、前記少なくとも1つの電子素子及び/又は電気素子が軸方向に配置されている、

ことを特徴とする回路装置。

(もっと読む)

回路基板の補強位置決定方法及び基板組立体

【課題】電子部品の周辺にスタッドが配置された回路基板において、必要最小限の反り低減対策を容易に決定することを目的とする。

【解決手段】回路基板の補強位置決定方法は、表面に、電子部品が複数のバンプにより実装され、裏面に、前記電子部品の角部に配置されたバンプに対応する位置に補強部材が貼り付けられた回路基板の数値モデルを設定する。そして、前記数値モデルに、前記電子部品の周囲に配置され且つ前記回路基板を電子機器の筐体に固定するスタッドに関する情報を取り込み、前記回路基板の裏側から前記電子部品に向かって力を加えたときに、前記角部のバンプにそれぞれ発生する応力値を求めるシミュレーションを行う。前記シミュレーションにより求めた前記応力値に基づいて、前記スタッドの位置に対応する前記補強部材の配置を決定する。

(もっと読む)

プリント配線板

【課題】表面実装部品の電極とプリント配線板上の電極パッドとの間の接続特性の劣化を招くことなく、極性を有する表面実装部品の搭載方向を判別できるようにする。

【解決手段】極性を有する表面実装部品101が実装されるプリント配線板1は、互いに間隔をあけて配置され、部品101の1対の電極がそれぞれ電気的に接続される1対の電極パッド13,14と、1対の電極パッド13,14をそれぞれ部分的に露出させる開口12a,12bを有するカバー層12と、を備える。一方の電極パッド13におけるカバー層12により覆われた部分13bの形状が、他方の電極パッド14におけるカバー層12により覆われた部分14bの形状と異なる。

(もっと読む)

基板ユニットおよび電子機器

【課題】電子部品を配線基板に高密度に実装することができるとともに、フレキシブル基板を配線基板に良好な状態で接続することができる基板ユニットを実現する。

【解決手段】本発明に係る基板ユニット1は、配線基板2と、フレキシブル基板6を挿入するための挿入口3aを有するFPCコネクタ3と、挿入口3aの配線基板2の実装面に対する高さを高くする部品内蔵基板8とを有する。

(もっと読む)

半導体パッケージ基板

【課題】電子素子を樹脂封止後に封止樹脂に開口を設け、加熱時のアウトガスやはんだの逃げ道を設けることにより、はんだフラッシュの発生を抑制するパッケージ基板を提供する。

【解決手段】多層配線基板上に1個以上の半導体素子と1個以上の受動部品が実装され、前記多層配線基板とその上に実装された前記半導体素子とのギャップにアンダーフィル樹脂6を充填することにより、フリップチップ実装部である半導体素子実装エリアを形成し、その半導体素子実装エリアの外周部と前記受動部品の周囲を樹脂7で充填した半導体パッケージ基板18において、充填した樹脂7の一部に、はんだ及びアウトガスの抜き孔15、16を設ける。

(もっと読む)

両面実装基板の製造方法

【課題】一度のリフロー工程で両面実装基板の表面および裏面に電子部品を接合させることができる両面実装基板の製造方法を提供する。

【解決手段】両面実装基板の製造方法において、基板9の裏面に接合される電子部品3,5の形状および電極との接合箇所に応じて形成された凹部7、およびリフロー工程中に蒸発するフラックスを外部へ排出する貫通穴2を有する治具1に電子部品3,5を嵌め込むステップと、電子部品3,5を嵌め込んだ治具1上に基板9を載せるステップと、基板9の表面の所定の位置に電子部品3,5を載せるステップと、基板9および電子部品3,5上に、凹部7、および貫通穴2を有する治具13を載せるステップと、治具1、基板9、および治具13を固定するステップと、治具1と治具13で挟持された基板2を傾斜させた状態で、リフロー炉に通すステップとを有する。

(もっと読む)

モジュール部品およびそれに用いられる配線基板

【課題】平面面積の大きいダミーパターンを設けることを必要とせずに、電子部品のθ回転を防止することが可能で、電子部品の高密度実装を妨げることがなく、例えば、高機能携帯電話(スマートフォン)に用いるのに適したモジュール部品およびそれに用いられる配線基板を提供する。

【解決手段】配線基板1に配設された実装用ランド2(2b)の近傍の、該実装用ランドを介して引回しパターン6と対向する領域に、実装用ランドの表面より一段低い位置に金属面10aを有するダミーパターン10を設け、はんだなどの導電性接合材3により、電子部品4の端子電極5(5b)と、実装用ランド2(2b)とを接合するとともに、引回しパターン6と、ダミーパターン10の金属面10aの両方に、導電性接合材3が流れ込むようにする。

配線基板1にビアホール電極9aを設けてその端面をダミーパターン10の金属面10aとして用いる。

(もっと読む)

実装基板および電子装置

【課題】配線基板と電子部品との電気的接続において、高周波特性に関して向上されたものとする。

【解決手段】実装基板は電子部品3の搭載部1aおよび信号導体層1bを含む上面を有している配線基板1と、搭載部1aの周辺に配置されており、信号導体層1bと電子部品3を電気的に接続するための配線層2aを含む主面を有している中継基板2とを備えており、主面は斜面からなる。本実施形態による実装基板は、このような構成を含んでいることによって、中継基板2の配線層2aが直線状に形成されるものとなり、配線層2aにおいて高周波信号の急激な伝搬方向の変化はなく、配線層における高周波信号が劣化するのを低減するものとなる。

(もっと読む)

基板と電子部品の接続構造

【課題】接点摺動を抑制し接触抵抗を低下させた基板と電子部品の接続構造を提供する。

【解決手段】プリント基板(1)のプリントされた接続端子(1’)と電子部品(2)の接続端子(2’)とを電気的に接続する接続構造であって、該接続構造は、前記プリント基板(1)のプリントされた接続端子(1’)に半田付けされた第1パット(4)と、前記電子部品(2)の接続端子(2’)に半田付けされた第2パット(3)と、前記第1パット(4)と第2パット(3)に、それぞれ、電気的に接続する接点を有する導電性ばね(7)と、前記導電性ばね(7)を位置決めする絶縁材の隔壁(5)と、を具備する接続構造において、前記第1パット(4)と第2パット(3)の前記接点に対する接続面を、導電性の良好な金属で被覆した接続構造とを特徴とする。

(もっと読む)

電子制御装置

【課題】小型化を可能にするとともに、放熱性も高めた電子制御装置を提供する。

【解決手段】配線パターンを有する回路基板2と、回路基板2上にて互いに隣り合って実装された複数の発熱電子部品の内、少なくとも一対の発熱電子部品5A、5Bとを備えた電子制御装置である。発熱電子部品5A、5Bは、一方の側に回路基板2と電気的及び機械的に接続するリード9を延出し、他方の側に放熱用金属プレート10を延出して構成されている。隣り合って実装された一対の発熱電子部品5A、5Bは、これらが隣り合う方向と交差する方向にリード9及び放熱用金属プレート10を向け、かつ、リード9及び放熱用金属プレート10の向く方向が互いに逆になるように配置されている。

(もっと読む)

プリント回路基板及びその製造方法

【課題】ファインピッチ及び半田ボールの高さを、従来より高く形成することができるとともに、設計自由度が向上するプリント回路基板及びその製造方法を提供する。

【解決手段】本発明のプリント回路基板100は、接続パッド120を有するベース基板110と、接続パッド120上に第1開口部を有する半田レジスト層130と、前記第1開口部に形成される半田ボール160と、を含み、半田ボール160が雪だるま状であるものである。

(もっと読む)

接点ピンの接続構造及び接点ピンの接続方法

【課題】導電パターン上の絶縁層に設けた孔に接点ピンを挿入した場合に、表面側の孔の部分に対応する箇所に影響を与えない接点ピンの接続構造及び接点ピンの接続方法を提供する。

【解決手段】接点ピンの接続構造は、導電パターンと、前記導電パターンの上に設けられた絶縁層と、前記絶縁層に設けられた孔に挿入されている導電性材料からなる接点ピンであって、前記孔の底で前記導電パターンと電気的に接続されている接点ピンと、前記孔の底で前記接点ピンを支持するピン支持部と、前記孔の底で、前記接点ピンと前記導電パターンとを電気的に接続する導電性ペーストと、を備える。

(もっと読む)

配線基板

【課題】簡単な作業でICの接続端子をメタルコア材に接続することが可能な配線基板を提供する。

【解決手段】導電性のメタルコア材21と、メタルコア材21の外周面を覆うように配設される絶縁層41,43と、複数の接続端子17a,18aを有し、絶縁層の少なくとも一方の面に実装されるIC12を備え、IC12に設けられる少なくとも一つの接続端子の領域に存在する絶縁層を除去し、この領域に銅板15を設ける。そして、接続端子とメタルコア材21とを、銅板15を介して電気的に接続する。これにより、簡単な作業でIC12の接続端子をメタルコア材21に接続することができ、ひいては放熱特性を向上させることができる。

(もっと読む)

プリント基板及びプリント基板の種別識別方法

【課題】比較的小さな面積で多くの種別を識別することができるプリント基板を提供する。

【解決手段】種別識別表示10には、4対のランド(12a1,12a2と12b1,12b2と12c1,12c2と12d1,12d2)が設けられている。それぞれのランドの対に対して、電子部品(抵抗器)5が実装されていない場合は“0”、実装されていれば“1”を示す。それぞれの箇所(4対)が示す数字の組み合わせにより、プリント基板の種別を示す識別番号を表す。

(もっと読む)

半導体装置の実装構造及び実装方法

【課題】半導体パッケージが基板表面に接続された実装構造体の不要な電磁波を抑制する。

【解決手段】本実装構造は、基板1表面上には、複数の第1の電極パッド12と、基板の電源層又はグラウンドに接続された複数の第3の電極パッド13とが形成されており、半導体パッケージ表面上には、複数の第2の電極パッド22と、半導体パッケージの電源層又はグラウンドに接続された複数の第4の電極パッド23とが形成されている。半導体パッケージと基板は、第1及び第2の電極パッドを電気的に接続する第1の導電性接合体31と、第3及び第4の電極パッドを電気的に接続する第2の導電性接合体32とにより接続され、第2の導電性接合体は、その大きさが第1の導電性接合体よりも小さく形成されるとともに、第1の導電性接合体のそれぞれの周囲を取り囲むように分布して配置されている。

(もっと読む)

配線基板

【課題】本発明は、汎用性が高く性能が安定した状態で磁性体デバイスを搭載する配線基板に関する。

【解決手段】配線基板1は、所定の平板状の基板2内にMRAM3が埋め込まれており、このMRAM3の埋め込まれている位置の基板2の表面2aには、周辺部品4aが、また、裏面2bには、周辺部品4bが配置されている。すなわち、配線基板1は、周辺部品4aと周辺部品4bが、基板2内に埋め込まれているMRAM3を挟んだ状態で配置されている。

(もっと読む)

1 - 20 / 1,191

[ Back to top ]