Fターム[5E346BB01]の内容

多層プリント配線板の製造 (97,916) | 配線パターンの形状、構造 (5,951) | 配線パターンが特定されたもの (3,046)

Fターム[5E346BB01]の下位に属するFターム

信号層に関するもの (1,481)

電源層に関するもの (380)

グランド層に関するもの (713)

Fターム[5E346BB01]に分類される特許

1 - 20 / 472

プリント基板組立体の配線設計方法及び製造方法

半導体モジュール

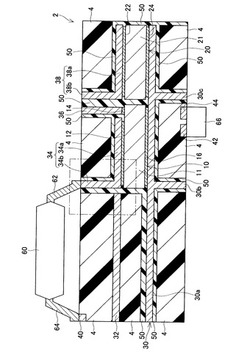

【課題】本明細書では、基板基材が熱によって劣化することを抑制することができる構造の半導体モジュールを開示する。

【解決手段】半導体モジュール2は、基板基材4内にIGBT10、ダイオード20、プリント配線30〜44、及び、断熱部50が配置されて形成されている。IGBT10とダイオード20は、基板基材4内に並べて配置されている。プリント配線30は、IGBT10及びダイオード20と接続されている。同様に、プリント配線34、36は、IGBT10と接続されている。また、プリント配線38は、ダイオード20と接続されている。プリント配線30〜44の一部は、基板基材4の表面に露出している。断熱部50は、IGBT10と基板基材4との間、ダイオード20と基板基材4との間、及び、プリント配線30、34、36、38と基板基材4との間に配置されている。

(もっと読む)

多層フレキシブル配線基板の製造方法、多層フレキシブル配線基板及びプローブカード

【課題】多層フレキシブル配線基板の製造途中で配線層毎のオープン・ショート検査を可能にする。

【解決手段】製造手順は次のとおりである。仮基板66と検査用配線層50を備える基礎部分を製造する。検査用配線層に検査端子56,58を形成する。電気めっき法により第1配線層70を形成する。検査プローブ72,74を用いて第1配線層70のショート検査を実施する。第1配線層70の上に絶縁層76を形成して、電気めっき法によりビア82を形成する。ビア82の形成の有無に基づいて第1配線層70のオープン欠陥の有無を判断する。第2配線層84以降についても同様の工程を繰り返す。仮基板66から多層配線部を剥離し、さらに、その多層配線部から選択エッチング法で検査用配線層50を除去する。

(もっと読む)

プリント基板

【課題】 複数のメタライズ層に形成されている導電トラックで構成されているコイルによって発生する、垂直巻線軸に沿う磁界の一様性を高めることができるプリント基板を提供する。

【解決手段】 このプリント基板においては、垂直方向に連続している第1のメタライズ層と第2のメタライズ層とに形成されている導電トラック(90、92、102、104、114、116、130、132、140、142、150、152)の、メタライズ層に平行な1つの平面上への重ね合わせによって、互いに直交しており、かつメタライズ層に平行である軸XおよびYを対称軸とする2軸対称性を有するパターンが形成され、重ね合わされる第1のメタライズ層および第2のメタライズ層の各々の単一または複数の導電トラックは、それだけでは、軸Xおよび/またはYを対称軸とする軸対称性を有していない。

(もっと読む)

リジッドフレキシブルプリント配線板の製造方法

【課題】剥離部が残留せず高精細な配線パターンが形成されるリジッドフレキシブルプリント配線板を得る。

【解決手段】フレキ部とリジッド部との境界部分に重なる枠状の補強用金属パターンを形成した内層フレキシブル配線板に樹脂の薄剥離フィルムを重ね、該薄剥離フィルムの表面から前記枠状の補強用金属パターンに達する加工用レーザー光を照射することで前記枠状の補強用金属パターンに添った枠状の第1の溝を形成し、前記枠状の第1の溝の外側の前記薄剥離フィルムを剥離して除去した前記内層フレキシブル配線板の上にビルドアップ層を積層し、前記ビルドアップ層の表面から前記枠状の補強用金属パターンに達する加工用レーザー光を照射することで前記フレキ部と前記リジッド部との境界部分の前記枠状の補強用金属パターン上に第2の溝を形成し、前記第2の溝で囲まれる前記ビルドアップ層及び前記薄剥離フィルムを除去する。

(もっと読む)

多層配線板の製造方法

【課題】ビアホールの形成工程を含まない多層配線板の製造方法を提供する。

【解決手段】絶縁性シート10と、絶縁性シート10の一方主面に埋め込まれた導電性の配線21〜27とを備える基板2を準備する工程と、基板2に形成された配線21〜27の所定位置に導電性インクを複数回吐出して、導電性の突起30が形成された基板5を作製する工程と、複数の基板51〜53を、一の基板52の一方主面に形成された突起30が他の基板53の他方主面に対向するように積層する工程と、積層した基板51〜53を加熱し、この積層方向に沿って押圧する工程を有する。

(もっと読む)

多層基板、及び多層基板の製造方法

【課題】電子回路モジュール製造工程の歩留まりを向上することができる多層基板を提供する。

【解決手段】複数の基板を積層された基板部2と、基板部2の厚さ方向に貫通するビア3と、ビア3の内部を充填した金属部4と、を備えた多層基板1において、金属部4は、ビア3の内壁に形成された第1の金属部20と、第1の金属部の内側に形成された第2の金属部21から構成され、基板部2内部におけるビア3の厚さ方向の中央部に配置され、かつ、第1の金属部20と基板部2の外部とを電気的に接続するように配置された導電部6と、を有することを特徴とする多層基板1とした。

(もっと読む)

コイル内蔵基板および電子装置

【課題】 コイル内蔵基板の内蔵コイルの重畳特性を向上させると共に、上面や下面に搭載された半導体チップやチップ部品に対するコイル用導体から発生する磁力線の影響を大幅に抑制することができるコイル内蔵セラミック基板および電子装置を提供すること。

【解決手段】

本発明のコイル内蔵基板は、内部にコイル導体4が埋設されているフェライト層2、3を、各々が非磁性フェライト層により形成されている一対の絶縁層1で挟持させて成り、コイルのコイル導体4間に非磁性フェライトからなる非磁性層が形成されており、コイルの上面および下面がフェライト層2、3で覆われている。

(もっと読む)

コイル内蔵基板および電子モジュール

【課題】コイル内蔵基板において磁性基体内に設けられたコイルの特性を向上させること。

【解決手段】コイル内蔵基板1は、磁性基体11を含む絶縁基体と、磁性基体11の内部に設けられたコイル12と、平面視において磁性基体11の複数の角部分に設けられた複数のキャスタレーション導体とを含んでいる。複数のキャスタレーション導体は、磁性基体11上に実装されるIC素子に電気的に接続される電源電位用導体と接地電位用導体と制御信号用導体とを含んでおり、電源電位用導体と接地電位用導体が制御信号用導体よりも大きい寸法を有している。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

積層回路基板の製造方法及び積層回路基板

【課題】複数の配線基板を、プリプレグをはさんで貼り合わせる積層回路基板の製造方法に於いて、それぞれの配線基板のランド間の接続信頼性を高めること。

【解決手段】鍍金スルーホール及びベタパターンが形成された第1の回路基板の表面に、前記鍍金スルーホールに到達する第1の孔及び前記ベタパターンに到達する第2の孔を有するプリプレグを形成する工程と、前記第1の孔内に導電性ペーストを充填する工程と、前記プリプレグを介して前記第1の回路基板に第2の回路基板を加圧する工程と、を有することを特徴とする積層回路基板の製造方法。

(もっと読む)

EBG構造及びプリント基板

【課題】 EBG構造を大型化することなくインダクタンス成分を増加させることで、バンドギャップ幅の広帯域化を実現したEBG構造及びプリント基板を提供する。

【解決手段】 導体プレーンと、導体プレーン上に設けられた誘電体層と、誘電体層上の複数の導体パッチと、導体パッチの隣り合う2つの導体パッチを電気的に接続する接続部とを有するEBG構造であって、接続部は、一方の導体パッチと接続される第1ビアと、他方の導体パッチと接続される第2ビアと、第1ビアと第2ビアを接続する接続配線とからなり、接続配線は、第1ビアと第2ビアとの間においてヘリカルインダクタまたはスパイラルインダクタを構成していることを特徴とする。

(もっと読む)

インターポーザ試験構造と方法

【課題】 インターポーザ試験構造と方法を提供する。

【解決手段】 具体例は、インターポーザを含む構造を開示する。インターポーザは、インターポーザの周辺に延伸する試験構造を有し、少なくとも一部の試験構造は、第一再配線素子中にある。第一再配線素子は、インターポーザの基板の第一表面上にある。試験構造は中間物で、少なくとも二個の探針パッドに電気的に結合される。

(もっと読む)

プリント基板の製造方法およびプリント基板

【課題】バックドリル加工におけるドリル加工の深さを適切に決定することが容易なプリント基板製造方法の提供。

【解決手段】プリント基板1には、バックドリル加工をするドリル4の径より狭い幅のテストパターン11を配線パターンと同じ内層に設けておく。テストパターン11は、スルーホールビア12,13を介して抵抗測定器2に接続されている。バックドリル加工を施す側のプリント基板1の表面におけるテストパターン対応領域からの軸に平行に、テストパターンの幅方向の中央に指向してドリル4でテストドリル加工を施し、電極12b,13b間の導通がなくなった時を抵抗測定器2で検出する。この時におけるテストドリル穴の深さを基に、バックドリル加工の目標深さを決定する。

(もっと読む)

電子装置の製造方法及び電子装置

【課題】モールド樹脂の硬化時に、樹脂基板とベアチップとの相対位置が変動することにより、ベアチップの電極パッドと貫通電極とを再配線で接続する際の歩留まりが低下してしまうことのない電子装置の製造方法及び電子装置を提供する。

【解決手段】機能素子が形成されたチップ15を支持体に仮固定するとともに、絶縁部材17を前記支持体に仮固定する。支持体に仮固定したチップ15及び絶縁部材17を、樹脂層16で被覆する。チップ15、絶縁部材17、及び樹脂層16を、支持体から引き離す。絶縁部材17が露出するまで樹脂層16を研磨することにより、チップ15、絶縁部材17、及び樹脂層16からなる再構築ウエハ10を得る。再構築ウエハ10の絶縁部材17に貫通孔を形成し、貫通孔内に貫通電極18を形成するとともに、再構築ウエハ10の上に、チップ15と貫通電極18とを接続する配線21を含む再配線層20を形成する。

(もっと読む)

積層基板の製造方法及び該方法で製造された積層基板

【課題】焼成時の内部応力を緩和でき、分割時のクラックの拡がりを抑制でき、焼成後の残留応力を低減できる積層基板の製造方法及び該方法で製造された積層基板を提供する。

【解決手段】(i)未焼成の上部絶縁層と未焼成の下部絶縁層との間に未焼成の中間絶縁層が挟まれるように積層して、複数個分の個基板になる個基板領域11a〜11dを含む未焼成の集合基板を形成する。中間絶縁層の少なくとも1層に、個基板領域11a〜11dの境界線11x,11yの一部を含む貫通孔30を予め形成し、貫通孔30によって集合基板の内部に空洞を形成する。(ii)未焼成の集合基板を焼成し、(iii)焼結済みの集合基板を、個基板領域11a〜11dの境界線11x,11yに沿って切断して、集合基板から個基板を分割する。

(もっと読む)

フレックスリジッドプリント配線板

【課題】電磁障害の発生を防止することができるフレックスリジッドプリント配線板を提供する。

【解決手段】複数のリジッド部1がフレックス部2を介して一体化されて形成されたフレックスリジッドプリント配線板Aに関する。銅箔10と樹脂層5を積層して形成された銅箔付き樹脂シート11の前記樹脂層5をフレキシブル基板7に重ねて前記銅箔付き樹脂シート11を前記フレキシブル基板7に接着する。所定領域の銅箔10を所定パターン形状となるように除去して導体回路8を形成する。この領域にリジッド基板9を積層して前記リジッド部1が形成されている。前記領域以外の領域に前記フレックス部2が形成されている。前記フレックス部2の銅箔10を除去し、これにより露出した前記樹脂層5に銀を蒸着又は銀ペーストを塗布・焼成することによって、前記フレックス部2に銀系の電磁波シールド層12が形成されている。

(もっと読む)

発光素子搭載用セラミック基板、その発光素子搭載用セラミック基板の製造方法、及び、発光素子搭載用セラミック基板を用いた発光素子搭載モジュール

【課題】安価な発光素子搭載用セラミック基板、及び発光素子搭載モジュールを提供する。

【解決手段】セラミック部2と、 セラミック部2の少なくとも1面に、酸化チタン(TiO2)もしくは酸化カルシウム(CaO)が拡散された反射改善層3と、から構成される発光素子搭載用セラミック基板1としたので、反射金属膜を形成する高価な工法(湿式めっき法、乾式めっき法、エッチング等)を使用する必要がなく、その結果として、安価な発光素子搭載用セラミック基板1、及び発光素子搭載モジュール6を提供することができる。

(もっと読む)

EBG構造及び基板

【課題】低周波数帯域のバンドギャップ特性を得ることが可能であり、小型化可能であるEBG構造、及びそれを備える基板を提供する。

【解決手段】本発明の一実施形態に示されるEBG構造は、導体層101と、導体層101とキャパシタンスを形成する導体層102と、導体層102にビア104aを介して接続される導体層103を有し、導体層103は導体板113a、113b、113c、113dから構成され、導体板113a、113b、113c、113dとビア104aとは導体線105a、105b、105c、105dを介してそれぞれ接続されているので、低周波数帯域のバンドギャップ特性を得ることができる。

(もっと読む)

セラミック多層基板

【課題】セラミック多層基板が実装された回路基板等から衝撃や応力が基板本体に作用しにくいセラミック多層基板を提供する。

【解決手段】セラミック多層基板は、(a)積層されたセラミック層を含み、セラミック層が積層された方向の片側に矩形の主面12bを有する基板本体と、(b)基板本体の主面12bに形成された外部電極14とを備える。すべて外部電極14が、基板本体の主面12bの互いに隣接する辺20a〜20dの中点22a〜22d同士を結ぶ第1の仮想線分30a〜30dに重なり、又は第1の仮想線分30a〜30dで囲まれた第1の仮想領域30xの内側に配置されている。

(もっと読む)

1 - 20 / 472

[ Back to top ]