Fターム[5E346DD13]の内容

多層プリント配線板の製造 (97,916) | 各層形成の方法 (10,210) | 導体層形成の方法 (4,026) | 塗布 (582)

Fターム[5E346DD13]に分類される特許

1 - 20 / 582

多層絶縁基板および多層絶縁基板の製造方法

セラミック多層基板の製造方法

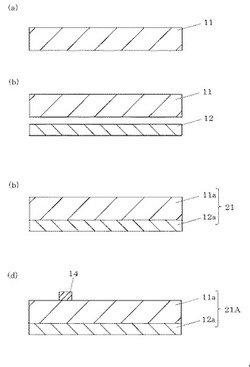

【課題】 上下の絶縁層間の密着性が高く、かつ絶縁層の層間から外側面への絶縁層の一部の突出等を抑制することが可能なセラミック多層基板の製造方法を提供すること。

【解決手段】 第1の樹脂材料を含む第1のセラミックグリーンシート層11(第1層11a)の下面に、第1の温度において第1の樹脂材料よりも弾性率が小さい第2の樹脂材料と、第1の温度よりも高い第2の温度において硬化する第3の樹脂材料とを含む第2のセラミックグリーンシート12層(第2層12a)を付着させる工程と、上面に金属ペースト13を印刷した2層セラミックグリーンシート21を第1の温度で積層する工程と、積層した2層セラミックグリーンシート21を第2の温度で加熱する工程とを備えるセラミック多層基板の製造方法である。積層時には第2層12aが柔軟であるため絶縁層1間の密着性が高く、積層後には第2層12aが変形しにくいため絶縁層1の突出を抑制できる。

(もっと読む)

焼結構造体の製造方法

【課題】セラミック積層基板のような焼結構造体を製造する際に、生積層体を焼成する過程において、セラミックグリーンシートが15〜30%程度収縮するため、焼結構造体の寸法精度を高めることが難しいという課題があった。

【解決手段】本発明の一態様に係る焼結構造体の製造方法は、第1セラミック部材および第2セラミック部材を準備する準備工程と、第2セラミック部材の2次元配列された開口部が第1セラミック部材の2次元配列された基体領域と上下に重なり合うように、これらのセラミック部材を交互に積層して積層体を得る積層工程と、積層体を焼成一体化する焼成工程と、個片に分割する分割工程とを有しており、第1セラミック部材に含まれる第1焼結材料と同じ焼成条件における焼結収縮率が第1焼結材料よりも小さい第2焼結材料を第2セラミック部材が含んでいることを特徴としている。

(もっと読む)

部品内蔵基板及びその製造方法並びに部品内蔵基板実装体

【課題】電子部品と導熱層との密着性を確保し、放熱特性を向上させる。

【解決手段】部品内蔵基板実装体100は、部品内蔵基板1と、これが実装された実装基板2とからなる。部品内蔵基板1は、第2〜第4プリント配線基材20〜40及びカバーレイフィルム3を熱圧着により一括積層した構造を備える。第2プリント配線基材20の第2樹脂基材21に形成された開口部29内には、電子部品90の裏面91aと導熱層23Aとが密着し、且つ孔部23Bを介して接着層9により固定された状態で内蔵されている。第4プリント配線基材40の実装面2a側にはバンプ49が形成されている。電子部品90の裏面91aに接する導熱層23Aやサーマルビア24を介して、各層のサーマルビア及びサーマル配線を通り、バンプ49から実装基板2に電子部品90の熱が伝わって、実装基板2にて放熱される。

(もっと読む)

多層基板

【課題】高性能な高周波伝送特性を実現したうえで、ビルドアップ接続の簡単化を図ることができる。

【解決手段】第1及び第2の誘電体層10,11の層面側の中心位置の周囲に所定位置ずらして放射状に配置した4個のビルドアップ接続部18を設けた接続用導体パターン17を有する高周波線路16を形成して、この第1及び第2の誘電体層10,11間に該第1及び第2の誘電体層10,11のビルドアップ接続部18がビルドアップ接続される4個のビルドアップ接続部18を所定角度ずらせて放射状に配置した接続用導体パターン17を有した第1乃至第3の中間誘電体層12〜14を積層配置してビルドアップ接続するように構成したものである。

(もっと読む)

多層セラミック基板の製造方法

【課題】収縮抑制シートを用いて無収縮焼成を行う場合に、グリーンシート積層体と収縮抑制シートとの密着性を高くでき、それにより、収縮バラツキを抑制できる多層セラミック基板の製造方法を提供すること。

【解決手段】脱脂工程において、収縮抑制シート23の平面方向における収縮率が0.05%以下と小さいので、脱脂工程及びその後の焼成工程におけるグリーンシート積層体31の収縮率が小さくなり、収縮バラツキも小さくなる。また、脱脂工程における収縮抑制シート23の収縮率がグリーンシート積層体31の収縮率より大きいので、収縮抑制シート23とグリーンシート積層体31との密着性が向上する。よって、グリーンシート積層体31の収縮を抑制することができる。従って、収縮バラツキを抑制することができるので、多層セラミック基板5における寸法バラツキを低減することができる。

(もっと読む)

配線基板ならびにその配線基板を備えた電子装置および電子モジュール装置

【課題】 実装信頼性が高い配線基板および電子装置ならびに電子モジュール装置を提供する。

【解決手段】 本発明の配線基板は、中央領域Mおよび周囲領域Sを有する上面を含んでおり、周囲領域Sに設けられておりそれぞれ電子部品Eが収納される複数の凹部3と中央領域Mまたは周囲領域Sに設けられており複数の凹部3を連結する連結部4とを有している絶縁基体2を備えており、同様の高さの部分をたどって中央領域Mから周辺領域Sを介して周辺領域Sの外側へつながる経路を有するように連結部4が配置されている。

(もっと読む)

配線基板及びその製造方法

【課題】半導体チップとの接続信頼性の優れた配線基板を提供すること。

【解決手段】オーガニック配線基板10の基板主面11側には、樹脂絶縁層21〜23と導体層24とを積層した第1ビルドアップ層31が形成されている。第1ビルドアップ層31における最表層の導体層24は、半導体チップをフリップチップ実装するための複数の接続端子部41を含む。複数の接続端子部41は、ソルダーレジスト25の開口部43を介して露出している。各接続端子部41は、半導体チップの接続領域51と、接続領域51から平面方向に延設されかつ接続領域51よりも幅が狭く形成された配線領域52とを有する。配線領域52の表面のはんだ濡れ性は接続領域51の表面のはんだ濡れ性よりも低くなっている。

(もっと読む)

光モジュールおよび多層基板

【課題】集積回路がフリップチップ実装された光モジュールにおいて、25Gbps以上の超高速伝送を行っても、隣接するチャンネル間のクロストークを低減し、良好な信号伝送を実現する光モジュールを提供する。

【解決手段】多層基板上の隣り合う第1および第2電極パッドのうち、第1電極パッドは第1導体ビア、第1内層導体配線と順次接続され、第2電極パッドは多層基板の表層導体配線、第3電極パッド、第2導体ビア、第2内層導体配線と接続され、第1内層導体配線と表層導体配線の間にはグランド導体ビアもしくは電源導体ビアが設けられ、第1内層導体配線が形成された第1形成層と第2内層導体配線が形成された第2形成層との間には、グランド導体配線層もしくは電源導体配線層が設けられる。第1および第2電極パッドは、それぞれ第1および第2光素子の表面に形成された電極パッドと接続される。

(もっと読む)

多層配線基板の製造方法、多層配線基板及びプローブカード

【課題】優れた信頼性を有する多層配線基板を製造し得る方法及び優れた信頼性を有する多層配線基板を提供する。

【解決手段】配線14を構成するためのビア導体15が内部に複数配されたセラミックグリーンシートを複数積層し、積層体を作製する。積層体を作製する際に、積層方向xにおいて隣り合うセラミックグリーンシートの間に、隣り合うビア導体15間に位置するように絶縁材20を配する。積層体を積層方向xにプレスする。プレスされた積層体を焼成することにより多層配線基板1を得る。

(もっと読む)

フレキシブルプリント配線板の製造装置および製造方法

【課題】一例として、より不都合の少ない基板を製造しやすい製造装置を得る。

【解決手段】実施形態にかかるフレキシブルプリント配線板の製造装置は、複数の装置を備える。第二導体層を設ける装置は、第一導体層の面に部分的に第二導体層を設ける。第一絶縁層を設ける装置は、第一導体層の面に部分的に第一絶縁層を設ける。第一導体層、第二導体層、第一絶縁層、および第三導体層を一体化する装置は、第一導体層の面に設けられた第二導体層および第一絶縁層が第一導体層とは反対側から第三導体層で覆われた状態で、一体化する。導体パターンを形成する装置は、第一導体層、第二導体層、第一絶縁層、および第三導体層が一体化された構造の第一導体層および第三導体層のうち少なくとも一方を部分的に除去して導体パターンを形成する。第二絶縁層で覆う装置は、導体パターンが形成された構造の両側を第二絶縁層で覆う。

(もっと読む)

回路モジュール

【課題】集積回路素子を有するICパッケージに、集積回路素子に接続されていない補助配線を設けることで、高密度配線が可能な回路モジュールを提供する。

【解決手段】集積回路素子5を有するICパッケージ2と、ICパッケージ2が実装される配線基板3とを備え、集積回路素子5がICパッケージ2の表面に形成された複数のパッドのうちの一部を介して配線基板3の複数のランド電極に接続されている回路モジュールにおいて、複数のパッドのうち集積回路素子5に接続されていない少なくとも2つのパッドが、ICパッケージ2に設けられ、かつ、集積回路素子5に接続されていない補助配線8により接続されるとともに、配線基板3に設けられた複数の配線パターン10が、集積回路素子5に接続されていない少なくとも2つのパッドと補助配線8を介して接続される。

(もっと読む)

多層セラミック基板及びその製造方法

【課題】無収縮焼成法を用いて、セラミック基板は、収縮されず、電極パターンは、水平方向に自由に収縮されて、微細な線幅及びパターン位置の精密度の両方を満足する多層セラミック基板及びその製造方法を提供する。

【解決手段】内部電極回路パターンの設けられたセラミック積層体を製造するステップと、前記セラミック積層体の外部に有機層を形成するステップと、前記有機層上に表面電極を形成するステップと、前記有機層及び前記表面電極の設けられたセラミック積層体を焼結するステップとを含む。

(もっと読む)

多層プリント配線基板及びその製造方法

【課題】導体回路層とビアとの間のクラックの進行を効果的に抑制して、層間接続の信頼性を向上させる。

【解決手段】多層プリント配線基板100は、第1及び第2プリント配線基材10,20を積層してなる。第1及び第2導体回路層11,12は、ビアホール13内のビア14により層間接続されている。第1導体回路層11のビアホール13側の面には、ビアホール13の開口径W1よりも第1絶縁基材19の面10a方向に大径の内径W2を有する凹部15が形成されている。ビア14は、ビアホール13及び凹部15内に充填された導電ペーストなどの導電材からなる。第1導体回路層11とビア14との接合界面の面積が、従来のインナービアを用いたものよりも大きいので、接合界面に沿ったクラックの進行経路長を延長し、進行方向を変化させ、接合界面の近傍が完全に破断することを抑制して、層間接続の信頼性を向上させる。

(もっと読む)

部品内蔵配線基板の製造方法

【課題】樹脂充填材とコア基板との密着性を改善することにより、信頼性に優れた部品内蔵配線基板を製造することが可能な部品内蔵配線基板の製造方法を提供すること。

【解決手段】コア基板準備工程ではコア基板11を準備し、収容穴部形成工程では収容穴部90をコア基板11に形成し、貫通穴部形成工程では貫通穴部14を形成する。めっき層形成工程では、収容穴部90の内壁面91に対してめっき層92を形成するとともに、貫通穴部14の内壁面に対して、空洞部を有するスルーホール導体となるめっき層71を形成する。収容工程では、部品101を収容穴部90に収容する。樹脂埋め工程では、収容穴部90の内壁面91と部品側面106との隙間、及び、空洞部に対して、樹脂充填材93を充填して埋める。

(もっと読む)

配線基板

【課題】信号配線に30GHz以上の超高周波の信号を効率よく伝送させることが可能な配線基板を提供すること。

【解決手段】絶縁層1を貫通する貫通導体3Sと、絶縁層1の表面に貫通導体3Sを覆うランド部Lを有して配設された帯状の信号配線2Sと、絶縁層1の表面に信号配線2Sの周囲を所定の間隔をあけて取り囲むように配設された接地導体2Gまたは電源導体2Pと、を具備して成る配線基板であって、信号配線2Sは、ランド部Lの直径よりも広い幅で接地導体2Gまたは電源導体2Pとの間隔が一定である幅広部Wと、幅広部Wとランド部Lとの間を接続し、ランド部Lの直径よりも狭い幅で且つ信号配線2Sを伝播する信号の波長の4分の1未満の長さの幅狭部Nとを有する配線基板である。

(もっと読む)

配線基板

【課題】絶縁基板とサーマルビアとの界面におけるクラックの抑制および発光素子で発生した熱の放熱性の向上。

【解決手段】配線基板20は、外部接続用電極層120、セラミックス層130および配線層140を備える。セラミックス層130は、アルミナとホウ珪酸ガラスを材料として形成されており、熱伝導率が6W/m・K以下である。セラミックス層130は、複数の第1のサーマルビア132、および、第1のサーマルビア132より小さい直径を有する第2のサーマルビア134を配置することにより、熱伝導率の低いセラミックス層130を用いた配線基板20において、発光素子150で生じる熱の放熱性能を向上している。第1のサーマルビア132は、発光素子搭載領域150a内に格子状に配置され、第2のサーマルビア134は、隣接する全ての第1のサーマルビア132から等距離離れた位置に配置されている。

(もっと読む)

多層セラミック基板およびその製造方法

【課題】構造欠陥の少ない多層セラミック基板およびその製造方法を得る。

【解決手段】多層基板10は、第1のセラミック層12a〜12dと第2のセラミック層14a〜14cとを交互に積層した構成を有する。第1のセラミック層12b,12c,12d上には、第1の内部電極16、第2の内部電極20、第3の内部電極22が形成される。第1の内部電極16の主面上に、第3のセラミック層18が形成される。第2の内部電極20および第3の内部電極22の主面および端部を覆うように、第3のセラミック層18が形成される。第3の内部電極22が形成された層において、第3のセラミック層18は、第1のセラミック層12dの全面を覆うように形成される。

(もっと読む)

コンデンサ及びその製造方法

【課題】ビア電極と表層電極との接続強度を高め、接続信頼性の高いコンデンサを提供する。

【解決手段】セラミックコンデンサ101のコンデンサ本体104は、コンデンサ主面102及びコンデンサ裏面103を有し、複数のセラミック誘電体層105及び複数の内部電極層141,142を積層してなる。複数のコンデンサ内ビア導体131,132は、コンデンサ本体の積層方向に貫通形成された貫通ビア130内に充填形成されており、各内部電極層141,142に接続されている。貫通ビア130は、コンデンサ主面102側の開口に向かうに従って拡径するように形成された拡径部135を有する。表層電極111,112は、コンデンサ主面102上において拡径したビア導体131,132の端面全体を覆うように設けられている。

(もっと読む)

高周波部品及び通信装置

【課題】小型化を図った高周波部品および通信装置を提供する。

【解決手段】複数の誘電体層を積層してなる積層基板に高周波信号処理回路を備えた高周波部品であって、高周波信号の入力、出力端子および高周波信号処理回路の複数の電源端子を含む端子群が積層基板の一方の主面に形成されており、積層基板を構成する誘電体層には、インダクタンス素子用等のパターン電極が構成され、一端がそれぞれ電源端子に接続された複数の電源ラインは、誘電体層1に形成されたビア電極を介して高周波信号処理回路が有する少なくとも一つの半導体素子に接続され、複数の電源ラインのうち少なくとも二つの電源ラインは、それぞれ、隣接する二以上の誘電体層1にわたって積層方向から見て重なるように形成されたビア電極列2を有し、少なくとも二つの電源ラインのビア電極列2は、隣接する誘電体層間において、他の導体パターンを介さずに近接している。

(もっと読む)

1 - 20 / 582

[ Back to top ]