Fターム[5F003BF06]の内容

バイポーラトランジスタ (11,930) | エミッタ・ベース接合 (716) | JE接合 (461) | ヘテロJE (433)

Fターム[5F003BF06]に分類される特許

1 - 20 / 433

三次元配置部品を有する化合物半導体集積回路

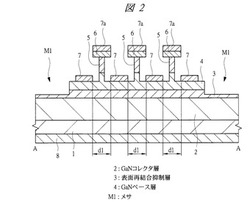

半導体装置

【課題】窒化物半導体を用いたメサ型の半導体装置のp型層の抵抗を低減する。また、窒化物半導体を用いたメサ型の半導体装置に高い値でばらつくオン抵抗が生じることを防ぐ。

【解決手段】窒化物半導体からなり、所定のベース電極間隔を有するヘテロ接合バイポーラトランジスタにおいて、GaNベース層4およびGaNコレクタ層2の間に表面再結合抑制層3を設け、GaNベース層4を貫通して表面再結合抑制層3の途中深さまで開口するメサM1を形成することでGaNベース層4を分離する。

(もっと読む)

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

電子装置

【課題】カーボンによるバンドギャップ・エンジニアリングを可能とし、カーボン原子に基づく多彩なエレクトロニクスを達成して、信頼性の高い電子装置を実現する。

【解決手段】電子装置は、単層のグラフェン膜1と、グラフェン膜1上の両端に設けられた一対の電極2,3とを有しており、グラフェン膜1では、電極2,3間の領域において、中央部位のBC間が複数のアンチドット10が形成されてなる第1の領域1aとされており、第1の領域1aの両側におけるAB間及びCD間がアンチドットの形成されていない第2の領域1bとされている。

(もっと読む)

半導体装置およびその製造方法

【課題】ヘテロ構造のpn接合において、電子が妨げられることなく注入されるようにする。

【解決手段】Gaを含む窒化物半導体からなるn型の窒化物半導体層101と、窒化物半導体層101に接合して形成されたp型のシリコンからなるp型シリコン層102とを少なくとも備える。窒化物半導体層101とp型シリコン層102とは、接合界面103により接合している。

(もっと読む)

トランジスタ素子

【課題】単体構造のHBTデバイスと同等の信頼性を得る。

【解決手段】化合物半導体からなる、高電子移動度トランジスタ(HEMT)とヘテロバイポーラトランジスタ(HBT)とを、同一基板上に重ねてエピタキシャル成長した多層構造のトランジスタ素子において、エピ層として内在するインジウムガリウムリン層(InGaP)のバンドギャップエネルギを1.91eV以上にすることを特徴とする。

(もっと読む)

トランジスタ素子

【課題】n型不純物としてTeを用いたノンアロイ層を有していても、ベース電流、コレクタ電流のリーク電流が少ないトランジスタ素子を提供する。

【解決手段】基板11と、基板11上に設けられた高電子移動度トランジスタ構造層28と、高電子移動度トランジスタ構造層28上に設けられたヘテロバイポーラトランジスタ構造層29とを備えたトランジスタ素子10において、ヘテロバイポーラトランジスタ構造層29のノンアロイ層26,27は、n型不純物としてTeがドーピングされており、n型不純物濃度が1.0×1019cm-3以上2.0×1019cm-3以下にされているものである。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタメサ表面で発生するコレクタリーク電流を抑制し、微細なHBTのコレクタ耐圧特性を改善する。

【解決手段】第2サブコレクタ層103は、第1サブコレクタ層102より平面視で小さい面積に形成されている。また、コレクタ層104は、第2サブコレクタ層103を構成している半導体層132より平面視で大きい面積に形成されている。また、ベース層105は、コレクタ層104より平面視で小さい面積に形成されている。また、エミッタ層106は、ベース層105より平面視で小さい面積に形成されている。加えて、第2サブコレクタ層103を構成している半導体層132およびベース層105は、平面視でコレクタ層104の内側の領域に形成されている。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

III−V族化合物半導体エピタキシャルウエハ

【課題】充分な選択比を備え、また、除去が比較的容易なエッチングストッパ層を得る。

【解決手段】GaAs基板10上に設けられた高電子移動度トランジスタ構造20と、高電子移動度トランジスタ構造20の上に設けられたヘテロ接合バイポーラトランジスタ構造40と、を備え、高電子移動度トランジスタ構造20とヘテロ接合バイポーラトランジスタ構造40との間には、As濃度が1.0×1016atoms/cc以上1.0×1021atoms/cc以下のInGaAsP層からなるエッチングストッパ層30を備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTにおいて、高周波特性を犠牲にすることなく、さらにオフ耐圧を向上させる。

【解決手段】InPからなる基板101の上に形成された第1コレクタ層102と、この上に形成された第2コレクタ層103と、この上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層104と、この上に形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを少なくとも備える。第2コレクタ層103は、第1コレクタ層102およびベース層104に接した状態で、ベース層104の伝導帯端のエネルギー準位よりも低く、第1コレクタ層102の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層104の価電子帯端のエネルギー準位よりも低い価電子帯端のエネルギー準位を有したものとなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】InP系の微細構造デバイスをより効果的に冷却できるようにする。

【解決手段】主表面を(001)面としたInPからなる基板101の上にInGaAsからなるバッファ層102を形成し、バッファ層102の上に接して配置されたInPの層を含んでバッファ層102の上に形成されたデバイス103を形成し、デバイス103の周囲のバッファ層102を露出させた状態でデバイス103を覆う保護層104を形成し、露出したバッファ層102の上に金を堆積して金層105を形成し、次に、バッファ層102の表面に接触している金層105よりデバイス103の下部のバッファ層102に金を拡散させる。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタのエミッタ窓における絶縁膜厚の変動をなくし、素子特性が安定した半導体装置を提供する。

【解決手段】バイポーラトランジスタを、コレクタ領域を含む基板1、基板1上にエピタキシャル成長で形成されたSiGe層126、SiGe層126上にポリシリコンによって形成されたエミッタ108を備え、エミッタ108とSiGe層126との界面において、ポリシリコン膜106とSiN膜127とでエミッタ窓120を形成し、SiN膜127がSiGe層126の直上に配置されるように形成する。

(もっと読む)

半導体発光素子

【課題】平坦性が向上した半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成されたInGaNからなる多重井戸構造を備える活性層15とを備え、n型積層構造が、GaN層11と、GaN層11上に形成されたドープ層10と、ドープ層10上に設けられた窒化物系III−V族化合物半導体層12と、窒化物系III−V族化合物半導体層12よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTで、大きな電流利得が得られるようにする。

【解決手段】コレクタ層102の上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層103と、ベース層103の上に接して形成されたスペーサ層104と、スペーサ層104の上に接して形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを備える。スペーサ層104は、ベース層103の伝導帯端のエネルギー準位よりも低く、エミッタ層105の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層103の価電子帯端のエネルギー準位よりも低く、エミッタ層105の価電子帯端よりも高い価電子帯端のエネルギー準位を有した状態で、ベース層103およびエミッタ層105に接して形成されている。

(もっと読む)

1 - 20 / 433

[ Back to top ]