Fターム[5F003BF07]の内容

バイポーラトランジスタ (11,930) | エミッタ・ベース接合 (716) | JE接合 (461) | ショットキーJE (6)

Fターム[5F003BF07]に分類される特許

1 - 6 / 6

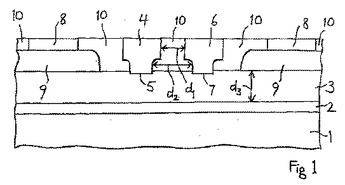

横方向のエミッタおよびコレクタを有するバイポーラトランジスタならびに製造方法

バイポーラトランジスタは、半導体材料からなる基板(1)と、基板内の高移動度層(2)と、高移動度層に隣接したドナー層(3)とを含む。エミッタ端子(4)がドナー層上のエミッタコンタクト(5)を形成し、コレクタ端子(6)がドナー層上のコレクタコンタクト(7)を形成する。ベース端子(8)が高移動度層に導電接続される。当該トランジスタは、GaAsのHEMT技術またはBiFET技術で製造可能である。  (もっと読む)

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

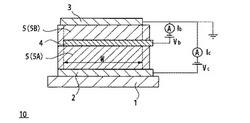

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

ショットキーバリア量子井戸共振型トンネルトランジスタ

【課題】ショットキーバリア量子井戸のトンネルトランジスタを提供する。

【解決手段】素子構造は、一つ或は複数の導電ベースリージョン33、第一半導体バリアーリージョン、第二半導体バリアーリージョン、導電エミッタリージョン31、導電コレクタリージョン35などを含み、第一半導体バリアーリージョン或は第二半導体バリアーリージョンのサイズは100Åより小く、第一ショットキーバリアの接合を第一半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第二ショットキーバリアの接合を第二半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第三ショットキーバリアの接合を導電エミッタリージョンと第一半導体バリアーリージョンのインターフェイスで生じ、第四ショットキーバリアの接合を導電コレクタリージョンと第二半導体バリアーリージョンのインターフェイスで生じる。

(もっと読む)

有機トランジスタ素子と電子・電気機器

【課題】 大気圧下加熱処理などを行わずに、MBOT素子構造の改良により良好な電流増幅特性やON/OFF比を得る。

【解決手段】 エミッタ電極とコレクタ電極との間に有機半導体層とシート状のベース電極が設けられている有機トランジスタ素子であって、前記ベース電極とコレクタ電極の間に、電荷透過促進層を有するものとする。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びヘテロ接合バイポーラトランジスタの製造方法

【課題】 チップ面積の増加や高周波特性の劣化を抑制しながら、熱安定性を向上させ、耐破壊性を向上することを目的とする。

【解決手段】 外部ベース領域下のコレクタ領域にイオン注入を行い、その上部の外部ベース領域上に容量膜110を設けることにより、入力された高周波の入力信号は、容量膜110を通って真性ベース領域に到達し、ベース電極に入力された直流電流は外部ベース領域を通って真性ベース領域に到達するため、チップ面積の増加や高周波特性の劣化を抑制しながら、熱安定性を向上させ、耐破壊性を向上することができる。

(もっと読む)

1 - 6 / 6

[ Back to top ]