Fターム[5F003BJ11]の内容

バイポーラトランジスタ (11,930) | 複合 (843) | 他素子との組合せ (551)

Fターム[5F003BJ11]の下位に属するFターム

Fターム[5F003BJ11]に分類される特許

1 - 12 / 12

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

トランジスタ素子

【課題】移動度が高いトランジスタ素子を提供する。

【解決手段】基板2上に高電子移動度トランジスタ(HEMT)3が形成され、そのHEMT3上にヘテロバイポーラトランジスタ(HBT)4が形成されたトランジスタ素子1において、HEMT3に、キャリア濃度が1×1019cm-3以下である電子供給層6,10を備える。

(もっと読む)

光電子集積回路

【課題】 ヘテロ接合バイポーラトランジスタ及びフォトダイオードが電気信号の劣化を伴うことなく接続され、全面再成長の特徴である高集積度を損ねることなく、動作速度及び受光感度に優れた光電子集積回路を提供する。

【解決手段】 光電子集積回路は、光素子2のアノード電極9又はカソード電極8からの配線19が[011]方向に形成されて素子に接続されることを特徴としている。

(もっと読む)

バイポーラ型半導体装置の順方向電圧回復方法、積層欠陥縮小方法およびバイポーラ型半導体装置

【課題】炭化珪素単結晶基板の表面から成長させた炭化珪素エピタキシャル膜の内部で通電時に電子と正孔が再結合するバイポーラ型半導体装置において、電流通電により拡大した積層欠陥面積を縮小し、増加した炭化珪素バイポーラ型半導体装置の順方向電圧を回復させる方法を提供する。

【解決手段】電流通電により積層欠陥面積が拡大し、順方向電圧が増加した炭化珪素バイポーラ型半導体装置を350℃以上の温度で加熱し、積層欠陥回復させる。

(もっと読む)

金属ベーストランジスタおよびそれを用いた発振器

【課題】 テラヘルツ帯の分光ならびに透視装置を小型・低コストで実現する上で、これに用いられる発振器を小型・低コスト化することが最重要課題であった。

【解決手段】 発振器の能動素子に金属ベーストランジスタを採用し、その最大発振周波数を数THzにまで向上するために、電子の飽和速度の高いInN或いはInNを主成分とする材料をコレクタに用いた。特性を再現性よく得るために、コレクタとベースの界面にInGaNを挿入することが有用である。本発明の金属ベーストランジスタを用いてテラヘルツ帯の発振を可能とする発振器を構成することが可能である。又、この発振器を信号源あるいは局所発振器の少なくとも一つに適用した分光装置を提供する。

(もっと読む)

半導体装置およびその製造方法ならびに電子装置

【課題】 熱的安定性と信頼性を両立し、さらに静電破壊耐量を向上したHBTを備えた半導体装置を提供する。

【解決手段】 化合物半導体からなる基板の主面上に、順に形成されたサブコレクタ層、コレクタ層、ベース層4およびエミッタ層5、ならびにコレクタ層4と電気的に接続されたコレクタ電極、ベース層4と電気的に接続されたベース電極、エミッタ層5上に形成され、エミッタ層5と電気的に接続されたエミッタメサ層6M、およびエミッタメサ層6Mと電気的に接続されたエミッタ電極13を備えたHBTであって、このエミッタメサ層6Mが、n型GaAs層からなる半導体層6と、半導体層6上のn+型GaAs層からなる高濃度半導体層6Bと、高濃度半導体層6B上のn型InGaAs層からなるバラスト抵抗層7とを有する。

(もっと読む)

ホット・キャリアにより誘起されるバイポーラ・デバイスの劣化を回復させるための方法

【課題】 ホット・キャリアにより誘起されるバイポーラ・デバイスの劣化を回復させるための方法を提供すること。

【解決手段】 アバランシェ劣化を示すアイドル状態のバイポーラ・トランジスタを、トランジスタの温度を上昇させて、バイポーラ・トランジスタのアバランシェ劣化を回復させる熱アニール・ステップに曝すステップを含む、アバランシェ・ホット・キャリアにより引き起こされる劣化を回復させるための方法が提供される。一実施形態においては、アニール源は、バイポーラ・トランジスタのエミッタと並んで配置されるSi含有レジスタである自己発熱構造体である。回復ステップ中、自己発熱構造体を含むバイポーラ・トランジスタはアイドル・モード(すなわちバイアスなし)に置かれ、別個の回路からの電流は自己発熱構造体を通って流れる。本発明の別の実施形態においては、アニール・ステップは、アバランシェ条件(1Vより低いVCB)以下で動作させながら、高い順方向電流(およそピークfT電流であるか又はそれより高い)をバイポーラ・トランジスタに与えた結果である。上述の条件下で、劣化の約40%又はそれ以上を回復させることができる。本発明のさらに別の実施形態においては、熱アニール・ステップは、急速加熱アニール(RTA)、炉アニール、レーザ・アニール又はスパイク・アニールを含むことができる。

(もっと読む)

半導体装置

【課題】増幅器としての高周波特性を損ねることなく、バイポーラトランジスタの過電流による熱的な粗密を緩和することができ、半導体素子の破壊を小規模な回路構成で防ぐことができる半導体装置を提供する。

【解決手段】複数のHBTを並列接続した高出力トランジスタの各ベースごとにバイアス電流の印加を制御し、また、エミッタ数が、ベースの数nに対して2の(n−1)乗倍で増大するマルチエミッタ素子を使うことにより、2進数により表せる値で各ベースごとのバイアス電流の印加を制御し、また、非常に大きな構造を有する方向性結合器の代わりに、高出力トランジスタのエミッタをマルチエミッタ構造にし、そのエミッタの一つの電流をモニタする。

(もっと読む)

半導体装置

【課題】ヘテロバイポーラトランジスタの単一セル内での動作が均一化され、信号増幅用として用いた場合に、その利得の低下および電力効率の低下を防止し、トランジスタ素子としての特性劣化および破壊をなくすことができる半導体装置を提供する。

【解決手段】単一のヘテロバイポーラトランジスタに複数存在するベース1、2を配線5により短絡して実効Vbeを共通化することにより、ヘテロバイポーラトランジスタの単一セル内に発生する熱的な粗密によるコラプス現象を完全に抑制する。

(もっと読む)

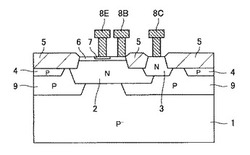

半導体装置

【課題】トランジスタのターンオフ時間を短くするため、トランジスタが組み込まれる外部回路で抵抗とダイオードを組み込むと、その抵抗やダイオードを組み込むスペースやその配線が回路基板などに確保される必要があり、電子機器の小形化の妨げになると共に、部品増および組立工数増などによるコストアップの原因になっている。

【解決手段】半導体基板に形成されるトランジスタのベース領域2と同時に形成されるダイオードのアノード領域4と、トランジスタのエミッタ領域3と同時に形成されるダイオードのカソード領域5とでダイオードを形成すると共に、導電体層6の一端とダイオードのアノード領域5が接続され、他の一端とダイオードのカソード領域4とが接続されている。トランジスタのベース領域2とカソード電極9との間に抵抗とダイオードを並列に接続することで、トランジスタのターンオフ時間を早くする。

(もっと読む)

半導体装置

【課題】 高周波動作時における各トランジスタの高周波電力利得の差の発生を抑制し、高周波での動作の均一性に優れた半導体装置を提供する。

【解決手段】 半導体装置10は、接地配線の接地距離の長さがより大きいGaAsHBT12のベース引き出し配線14−コレクタ引き出し配線15間に接続された容量素子20の容量をより小さくしている。これによって、各GaAsHBT12の接地インダクタンスの増加に伴う高周波電力利得の低下を、容量素子20の容量の低減による高周波電力利得の増加によって補償することができる。したがって接地インダクタンスの差異によって生じる各GaAsHBT12の高周波電力利得の差を少なくすることができる。このように半導体装置10では、高周波動作時における各GaAsHBT12の不均一な動作の発生を抑制することができる。

(もっと読む)

発光装置

【課題】 アクティブマトリクス方式に代表される、トランジスタ4を駆動素子として用いる電流駆動方式の発光装置において、簡素な構成によって従来よりも発光効率を向上させる。

【解決手段】 発光素子2と、発光素子2を駆動する駆動回路3とを備える発光装置であって、駆動回路3中にトランジスタ4が介装されるとともに、トランジスタ4の電流経路に、発光素子2から発する光により電気抵抗が低下する物質を含有させる。

(もっと読む)

1 - 12 / 12

[ Back to top ]