Fターム[5F003BJ90]の内容

保護回路 (75)

Fターム[5F003BJ90]に分類される特許

1 - 20 / 75

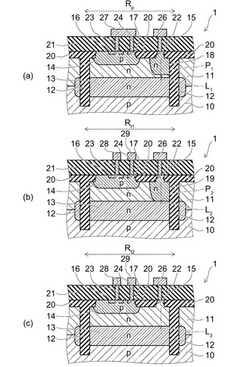

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

半導体素子の製造方法、ESD保護素子の製造方法

【課題】半導体ウエハに厚みばらつきがある前提で、コストアップをすることなく高品質の半導体素子を提供すること。

【解決手段】第1導電型の活性層の下に第1導電型の埋込拡散層を有する半導体基板を準備するステップと、活性層と埋込拡散層の総厚を測定し、測定した総厚から前記活性層の厚さを求めるステップと、活性層に、埋込拡散層との間で電流が流れる第1導電型のコレクタ領域をイオン注入によって形成するステップと、活性層に、埋込拡散層との間で電流が流れる第2導電型のベース領域をイオン注入によって形成するステップと、ベース領域内に、ベース領域との間で電流が流れる第1導電型のエミッタ領域をイオン注入によって形成するステップとを備え、ベース領域を形成するステップは、活性層の厚さに応じてイオン加速エネルギーを変化させるステップであることを特徴とする。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

高電圧バイポーラベースESD保護構造

【課題】面積効率の良い高電圧の単極性ESD保護デバイスを提供する。

【解決手段】ESD保護デバイス300は、p型基板303と、基板内に形成され、カソード端子に接続されるn+及びp+コンタクト領域310、312を包含し、第1のpウェル308−1と、基板内に形成され、アノード端子に接続されるp+コンタクト領域311のみを包含する第2の別個のpウェル308−2と、第1及び第2半導体領域を取り囲み且つこれら半導体領域を分離するように基板内に形成された、電気的にフローティングのアイソレーション構造304、306、307−2とを含む。カソード及びアノードの端子に、トリガー電圧レベルを上回る正電圧が印加されると、ESD保護デバイスは、構造を通り抜ける低インピーダンス経路を提供してESD電流を放電するよう、内在サイリスタをスナップバックモードに入らせる。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタにおいてオフ耐圧及び破壊電流量の双方を高くする。

【解決手段】第2のベース領域116は、ディープウェル112の表層に形成されており、平面視において第1のベース領域114とシンカー110との間に位置している。そして第2のベース領域116は、第1のベース領域114に接続しており、第1のベース領域116よりも不純物濃度が高く、かつ第1のベース領域116よりも深さが浅い。埋込層108は、半導体層106に形成され、上面がディープウェル112及びシンカー110に接しており、ディープウェル112よりも不純物濃度が高い。

(もっと読む)

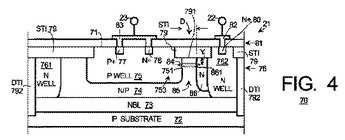

ESD保護デバイスおよび方法

関連するデバイスまたは回路24を保護する静電気放電(ESD)保護クランプ21、21’、70、700は、バイポーラ21、21’、70、700を備える。アバランシェ降伏が、上にある誘電体・半導体界面791から離れ、デバイス70、700のベース領域74、75の部分84,84以内に望ましく起こるように向かうベース75およびコレクタ86領域のドーパントを構成される。例えば、半導体ダイまたはウェハのトランジスタ21、21’、70、700の異なる方位配向のおかげで、ESDトリガ電圧の最大変化(△Vt1)MAXはベース・コレクタ間隔寸法Dの関数である。トリガ電圧一貫性および製造歩留まりが改良される。  (もっと読む)

(もっと読む)

ESD保護素子、半導体装置およびプラズマディスプレイ装置

【課題】 製造コストを上昇させることなくSOI構造の高耐圧半導体集積回路装置に組み込むことができるとともに、チップ面積の増大を抑制できるESD保護素子を提供する。

【解決手段】

ESD保護素子は、埋め込み絶縁膜2上に形成され、素子分離領域17で囲まれた第1導電型半導体層3、半導体層3に形成された第1導電型第1半導体領域8、第1導電型第1半導体領域8から離間して半導体層3に形成された第2導電型第1半導体領域16、第2導電型第1半導体領域16に形成され、それより高不純物濃度の第2導電型第2半導体領域10、第2導電型第2半導体領域10に形成された高不純物濃度の第1導電型第2半導体領域9からなる構造を有している。また、第1電極12および第2電極13は高耐圧半導体回路に電気的に接続され、第2導電型第1および第2半導体領域16、10は電気的にフローティング状態となっている。

(もっと読む)

半導体装置

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

静電気保護用半導体装置

【課題】 半導体集積回路をESDの過電流ノイズ及びラッチアップ試験の過電流ノイズから保護する保護回路であって、電源端子から保護素子への配線の配置の自由度を高めることができ、チップ面積の増大とはならない、保護回路を提供する。

【解決手段】 ラッチアップ試験の過電流ノイズから保護するバイポーラトランジスタ12のベース接地電流増幅率を0.5〜1.0になるような構造とすることで、I/O端子10から入ったラッチアップ試験の過電流ノイズは、バイポーラトランジスタ12を通り接地端子11へ流れるので、電源端子9からバイポーラトランジスタ12のベースへの配線を細くすることが可能となり、配線配置の自由度が高まる。

(もっと読む)

半導体装置

【課題】ドレイン端での電流集中を防止して静電放電に対する耐性に優れた半導体装置を提供する。

【解決手段】保護素子1は、MOS構造のデバイスの一部に、縦型バイポーラトランジスタQ1と寄生バイポーラトランジスタQ2とを形成した構造になっている。N+ドレイン領域3とゲート直下のチャネル領域4との間にはNドリフト領域5が形成されている。N+ソース領域6に隣接してP+ベースコンタクト領域7が形成されている。ソース側に縦型トランジスタQ1を形成して、静電放電時に発生したホール電流を縦型トランジスタQ1に流すようにしたため、N+ドレイン領域のベース側端部での電流集中を緩和できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バイポーラトランジスタが動作する際に、ベース領域のうちコレクタ側の端部が破壊されることを抑制する。

【解決手段】ベース領域150は、ウェル110内に形成されている。エミッタ領域170はベース領域150の中に形成され、ベース領域150より浅い。コレクタ領域140はウェル110内に形成され、ベース領域150の外側に位置している。第1埋込領域180は、少なくとも一部がベース領域150の中に位置しており、ベース領域150よりも不純物濃度が高い。そして第1埋込領域180は、平面視において、エミッタ領域170とコレクタ領域140の間に少なくとも一部が位置している。また第1埋込領域180は、エミッタ領域170の縁のうち少なくとも一辺と重なっており、かつエミッタ領域170の全面には重なっていない。

(もっと読む)

ESD保護素子

【課題】ESD耐量及びノイズ耐性を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、NPNバイポーラトランジスタTr1と、一端がパッド10に接続されたトリガ素子20とを具備する。NPNバイポーラトランジスタTr1は、第1ベース拡散層204と、パッド10に接続されたコレクタ拡散層4と、第1ベース拡散層204上に形成され、第1配線L1を介してトリガ素子20の他端に接続されたトリガタップ1と、第1ベース拡散層204上に形成され、第1配線L1と異なる第2配線L2を介してGNDに共通接続されたエミッタ拡散層2及び第2ベース拡散層3とを備える。

(もっと読む)

化合物半導体素子及びその製造方法

【課題】高速動作が可能でかつ、ESD耐性の高い化合物半導体素子及びその製造方法を提供すること。

【解決手段】本発明に係る化合物半導体素子は、電界効果トランジスタ又はヘテロ接合バイポーラトランジスタからなるトランジスタ部と、トランジスタ部と並列に接続されたESD保護部114と、を備え、ESD保護部114は、第1導電型の不純物を含有する第1及び第2の半導体層109、113と、第1及び第2の半導体層109、113の間に形成され、第1及び第2の半導体層109、113の禁制帯幅よりも禁制帯幅が広く、かつ、不純物濃度が1×1017cm−3以下である第3の半導体層111と、を備えるものである。

(もっと読む)

1 - 20 / 75

[ Back to top ]