Fターム[5F003BP94]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 多工程のエッチング方法 (270)

Fターム[5F003BP94]の下位に属するFターム

リフトオフ (34)

エッチングレートの差を利用するもの (76)

酸化後のエッチング (10)

Fターム[5F003BP94]に分類される特許

1 - 20 / 150

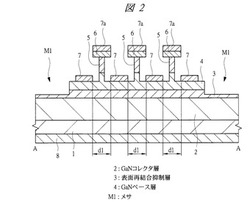

半導体装置

【課題】窒化物半導体を用いたメサ型の半導体装置のp型層の抵抗を低減する。また、窒化物半導体を用いたメサ型の半導体装置に高い値でばらつくオン抵抗が生じることを防ぐ。

【解決手段】窒化物半導体からなり、所定のベース電極間隔を有するヘテロ接合バイポーラトランジスタにおいて、GaNベース層4およびGaNコレクタ層2の間に表面再結合抑制層3を設け、GaNベース層4を貫通して表面再結合抑制層3の途中深さまで開口するメサM1を形成することでGaNベース層4を分離する。

(もっと読む)

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

炭化珪素半導体装置

【課題】エミッタ層からコレクタ層を経由してベース層へ移動する電荷の移動を阻止し、エミッタ層からコレクタ層を経由してベース層に注入される電荷を無くすことで、コレクタ層における欠陥の成長を防止することが可能な炭化珪素半導体装置を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素半導体基板により構成された炭化珪素半導体装置であり、第1の導電型のコレクタ層102と、コレクタ層の上部に設けられた第2の導電型のベース層104と、ベース層の一部として設けられたベース電極105と、ベース層上に設けられベース電極と離間して設けられたエミッタ層107と、ベース電極からエミッタ層に対して移動する電荷の経路において、コレクタ層内に設けられた、コレクタ層内における電荷の経路を遮断する絶縁体層112とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタのエミッタ窓における絶縁膜厚の変動をなくし、素子特性が安定した半導体装置を提供する。

【解決手段】バイポーラトランジスタを、コレクタ領域を含む基板1、基板1上にエピタキシャル成長で形成されたSiGe層126、SiGe層126上にポリシリコンによって形成されたエミッタ108を備え、エミッタ108とSiGe層126との界面において、ポリシリコン膜106とSiN膜127とでエミッタ窓120を形成し、SiN膜127がSiGe層126の直上に配置されるように形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTで、大きな電流利得が得られるようにする。

【解決手段】コレクタ層102の上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層103と、ベース層103の上に接して形成されたスペーサ層104と、スペーサ層104の上に接して形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを備える。スペーサ層104は、ベース層103の伝導帯端のエネルギー準位よりも低く、エミッタ層105の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層103の価電子帯端のエネルギー準位よりも低く、エミッタ層105の価電子帯端よりも高い価電子帯端のエネルギー準位を有した状態で、ベース層103およびエミッタ層105に接して形成されている。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】パターン形成不良が発生することを抑制する。

【解決手段】まず、N型コレクタとなる基板110上に、第1開口部(不図示)を有するシリコン酸化膜120を形成する。次いで、シリコン酸化膜120及び第1開口部に露出した基板110の表面上に第1絶縁膜を形成する。次いで、第1絶縁膜をエッチバックすることにより、シリコン酸化膜120の第1開口部における側壁のみに、第1絶縁膜を残存させて、側壁部を形成する。次いで、シリコン酸化膜120等の上に、ベース引出部144となるポリシリコン膜を形成する。次いで、ポリシリコン膜上に、第2開口部(不図示)を有する第2絶縁膜を形成する。次いで、第2絶縁膜をマスクとして、ポリシリコン膜のうち、第2開口部により露出している部分を酸化してシリコン酸化膜に変化させる。次いで、シリコン酸化膜に変化させた部分を選択的に除去する。次いで、側壁部と第2絶縁膜を選択的に除去する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】セルフアライメントにより容易に電極を形成することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】エッチングストッパ層2の上方に、Sbを含み、所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いSb含有層3bを形成し、Sb含有化合物半導体層3b上に、Asを含み、前記所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いAs含有層3cを形成する。そして、前記所定の溶液を用いて、導電膜4をエッチングマスクとし、Sb含有層3b及びAs含有層3cをメサ状にウェットエッチングし、平面視でSb含有層3b及びAs含有層3cから離間した位置において化合物半導体層1の上方に導電膜5aを形成する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型のドリフト層23との間に形成されている厚さを20μmとしたn型のバッファ層22が、p型のアノード層24,25からの正孔のトラップとして働いて、正孔(少数キャリア)がn型SiC基板21へ到達することを防ぐ。これにより、正孔(少数キャリア)がn型SiC基板21へ到達することを防いで、n型SiC基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

バイポーラ半導体素子

【課題】制御電極による制御能力を向上できるバイポーラ半導体素子を提供する。

【解決手段】このゲートターンオフサイリスタは、隣り合う2列R1,R2のメサ型のアノードエミッタ層5の間で列方向に延在している列間の第1のコンタクトホール20Bに形成された第1のゲート端子15だけでなく、各列R1,R2の端側で各列R1,R2に沿って列方向に延在している端側の第2,第3のコンタクトホール20C,20Dに形成された第2,第3のゲート端子16,17を有する。これにより、列間の第1のゲート端子15と端側の第2,第3のゲート端子16,17とでターンオフ時の転流を分担できて、転流の不揃いを抑制できる。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

1 - 20 / 150

[ Back to top ]