Fターム[5F003BP96]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 多工程のエッチング方法 (270) | エッチングレートの差を利用するもの (76)

Fターム[5F003BP96]に分類される特許

1 - 20 / 76

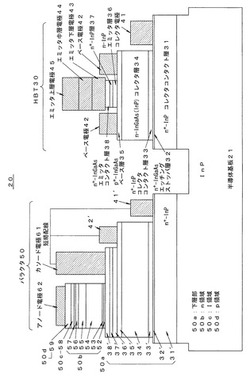

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタメサ表面で発生するコレクタリーク電流を抑制し、微細なHBTのコレクタ耐圧特性を改善する。

【解決手段】第2サブコレクタ層103は、第1サブコレクタ層102より平面視で小さい面積に形成されている。また、コレクタ層104は、第2サブコレクタ層103を構成している半導体層132より平面視で大きい面積に形成されている。また、ベース層105は、コレクタ層104より平面視で小さい面積に形成されている。また、エミッタ層106は、ベース層105より平面視で小さい面積に形成されている。加えて、第2サブコレクタ層103を構成している半導体層132およびベース層105は、平面視でコレクタ層104の内側の領域に形成されている。

(もっと読む)

III−V族化合物半導体エピタキシャルウエハ

【課題】充分な選択比を備え、また、除去が比較的容易なエッチングストッパ層を得る。

【解決手段】GaAs基板10上に設けられた高電子移動度トランジスタ構造20と、高電子移動度トランジスタ構造20の上に設けられたヘテロ接合バイポーラトランジスタ構造40と、を備え、高電子移動度トランジスタ構造20とヘテロ接合バイポーラトランジスタ構造40との間には、As濃度が1.0×1016atoms/cc以上1.0×1021atoms/cc以下のInGaAsP層からなるエッチングストッパ層30を備える。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】電流利得や電流利得遮断周波数などの他の素子性能を劣化させることなく、ヘテロ接合バイポーラトランジスタのオン電圧が効果的に低減できるようにする。

【解決手段】基板101の上に、サブコレクタ層102、コレクタ層103、ベース層104、第1エミッタ層105、第2エミッタ層106、および、キャップ層107が順次積層されており、第2エミッタ層106は、第1エミッタ層105に対してウェットエッチング法により選択的に除去される半導体材料によって形成され、かつ、第2エミッタ層106を構成する半導体が不純物添加によって縮退している。加えて、このHBTの第1エミッタ層105は、ベース層104の側に配置されて不純物が添加された第1半導体層151と、第2エミッタ層106の側に第1半導体層151に接して配置されて不純物が無添加の第2半導体層152とから構成されている。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

トランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法

【課題】GaAs基板からHBT構造層に伝搬する転位を抑制したトランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ構造層3が形成され、高電子移動度トランジスタ構造層3上にヘテロバイポーラトランジスタ構造層4が形成されたトランジスタ素子において、GaAs基板2の転位密度が10,000/cm2以上100,000/cm2以下であり、高電子移動度トランジスタ構造層3とヘテロバイポーラトランジスタ構造層4との間に、InGaPからなるエッチングストッパ層12と、エッチングストッパ層12上に設けられたGaAsからなる安定化層21と、を設けたものである。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】セルフアライメントにより容易に電極を形成することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】エッチングストッパ層2の上方に、Sbを含み、所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いSb含有層3bを形成し、Sb含有化合物半導体層3b上に、Asを含み、前記所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いAs含有層3cを形成する。そして、前記所定の溶液を用いて、導電膜4をエッチングマスクとし、Sb含有層3b及びAs含有層3cをメサ状にウェットエッチングし、平面視でSb含有層3b及びAs含有層3cから離間した位置において化合物半導体層1の上方に導電膜5aを形成する。

(もっと読む)

半導体装置

【課題】同一基板上にヘテロ接合バイポーラトランジスタ(HBT)と電界効果トランジスタ(FET)とが形成され、HBTのコレクタ抵抗が低減されてHBTの特性が向上され、かつFETのゲートリセスのエッチング精度が良好で、FETのオン抵抗が低い半導体装置を安定的に提供する。

【解決手段】HBT101Aにおいては、サブコレクタ層が複数の半導体層13〜15の積層構造からなり、かつ、サブコレクタ層においてコレクタ層17より張り出した部分上にコレクタ電極28が形成されている。FET101B、101Cにおいては、HBT101Aのサブコレクタ層をなす複数の半導体層のうち半導体基板1側の少なくとも1層の半導体層13が、キャップ層の少なくとも一部の層を兼ねている。HBTサブコレクタ層の総膜厚が500nm以上であり、FETキャップ層の総膜厚が50nm以上300nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタをより高速に動作させることができるようにする。

【解決手段】リン酸および過酸化水素水を用いたウェットエッチングにより選択的にInGaAsをエッチングすることで、n−InGaAs層102をパターニングしてソースコンタクト層(第1半導体層)112を形成するとともに、チャネル層114の側部をエッチングして幅が狭くされたチャネル層114aを形成する。このウェットエッチングにより、所望のメサ幅(例えば15nm)としたチャネル層114aを形成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

シリコンゲルマニウムトランジスタの製造方法

【課題】犠牲エミッタ膜を高い選択性で除去することにより特性のバラツキを抑制し、高精度なホトリソグラフィー技術を必要としないシリコンゲルマニウムトランジスタの製造方法を提供する。

【解決手段】SiGe膜6上のシリコン酸化膜8上にN型の犠牲エミッタポリシリコン23を形成し、その周囲にシリコン窒化膜からなるサイドウォール7を形成する。次に、ノンドープのポリシリコン膜24を形成し、サイドウォール7及び犠牲エミッタポリシリコン23をマスクにSiGe膜6にP型不純物をイオン注入して、外部ベース領域を形成する。次に、犠牲エミッタポリシリコン23をエッチングして除去し、その下のシリコン酸化膜8も除去する。その後、犠牲エミッタポリシリコン23等が除去されたエミッタ部分にエミッタポリシリコンを形成する。犠牲エミッタポリシリコン23をエッチングして除去する工程では、エッチャントとしてTMAH水溶液を使用する。

(もっと読む)

トランジスタ素子

【課題】GaAs基板上にHEMT、HBTを順次積層してなるトランジスタ素子において、HEMTの移動度の低下を抑制することが可能なトランジスタ素子を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ(HEMT)3が形成され、HEMT3上にヘテロバイポーラトランジスタ(HBT)4が形成されたトランジスタ素子において、HEMT3がアンドープInGaAsPからなるバリア層10を有する。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、窒化シリコン(SiN)からなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲からベース電極111の上面にかけて(渡って)窒化シリコンからなる第2絶縁層109が形成されている。第2絶縁層109は、第1絶縁層108の側面、レッジ構造部105aとベース電極111との間のベース層104の上、およびベース電極111の上面を覆うように形成されている。基板101の平面方向において、レッジ構造部105aの外形は第1絶縁層108の外形と同じに形成されている。また、エミッタメサより離れる方向のベース電極111の外周部分が、第1絶縁層108の外周部分に重なって形成されている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】エミッタメサの加工精度を損ねることなく、HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、SiNからなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲には、酸化シリコンからなる第2絶縁層109が形成されている。第2絶縁層の下端部には、レッジ構造部1105aが形成されている領域より外側に延在し、第1絶縁層108およびレッジ構造部105aの側方のベース層104との間に空間を形成する庇部109aが形成されている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBT(ヘテロジャンクション・バイポーラトランジスタ)による段差を低減し、接合面積をより小さくできる製造方法を提供する。

【解決手段】半絶縁性のInPからなる基板101の上に形成されたアンドープInPからなる第1半導体層102と、第1半導体層102の上に接して形成された第1導電型のInPからなるエミッタ層103と、第1半導体層102の上に接して形成されたInGaAsからなるコレクタ層108と、第1半導体層102の上に接して形成され、エミッタ層103およびコレクタ層108に挟まれて配置された第2導電型のInGaAsからなるベース層105とを備える。また、半絶縁性のInPからなる第1分離層106aおよび第2分離層106bを備える。

(もっと読む)

半導体装置の製造方法

【課題】CMPによる平坦化処理の工程数を減らし、平坦化処理の際に用いられるストッパー膜の膜厚バラツキを低減できるようにした半導体装置の製造方法を提供する。

【解決手段】第1の溝h1及び第2の溝h2をポリシリコン膜12で充填するとともに、素子形成領域4をポリシリコン膜12で覆う工程と、シリコン酸化膜9をマスクにポリシリコン膜12をエッチングすることで、素子形成領域4からポリシリコン膜12を除去する工程と、素子形成領域4からポリシリコン膜12を除去した後で、第1の溝h1及び第2の溝h2をシリコン酸化膜13で充填するとともに、素子形成領域4をシリコン酸化膜13で覆う工程と、シリコン酸化膜13の上面をCMPにより平坦化する工程とを含む。

(もっと読む)

1 - 20 / 76

[ Back to top ]