Fターム[5F004AA04]の内容

半導体のドライエッチング (64,834) | 目的 (7,312) | 選択性の向上 (1,192) | エッチングマスクの改良 (327)

Fターム[5F004AA04]に分類される特許

1 - 20 / 327

発光ダイオード

半導体装置およびその製造方法

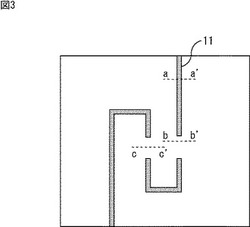

【課題】同一レイヤに成膜された後、複数回のエッチングにより形成された導電性被加工物を、下地層に段差を作ることなく、異なる電位に固定する。

【解決手段】同一レイヤに成膜された後、複数回のエッチングにより線状に形成された導電性被加工物を備え、導電性被加工物は、自身を電気的に分断する2以上の分断部分を有し、分断部分における導電性被加工物は、その一部が平行になるように形成されており、平行に形成された部分の少なくとも一方は分断されている。複数回のエッチングに用いられるレジストパターンのうちの、所定回数目のエッチングに用いられる第1のレジストパターンと、他の回数目のエッチングに用いられる第2のレジストパターンとが重なる領域の、平行に形成された部分に対応する箇所の幅は、エッチングによる導電性被加工物の後退量より小さい。本技術は、半導体装置に適用することができる。

(もっと読む)

ラインエッジ粗さを低減させた特徴のエッチング

【課題】ラインエッジ粗さを低減させて特徴をエッチングする

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

(もっと読む)

エッチング方法

【課題】被加工材とレジストのエッチングの選択比を高くすることのできるエッチング方法、、このエッチング方法により加工されたサファイア基板、及び、このサファイア基板を備える発光素子を提供する。

【解決手段】プラズマエッチング装置を用いたエッチング方法であって、被加工材上にレジスト膜を形成するレジスト膜形成工程と、前記レジスト膜に所定のパターンを形成するパターン形成工程と、前記パターンが形成された前記レジスト膜を所定の変質用条件にてプラズマに曝し、前記レジスト膜を変質させてエッチング選択比を高くするレジスト変質工程と、被加工材を変質用条件と異なるエッチング用条件にてプラズマに曝し、エッチング選択比が高くなった前記レジスト膜をマスクとして被加工材のエッチングを行う被加工材のエッチング工程と、を含むようにした。

(もっと読む)

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

パターン形成方法及びパターン形成体

【課題】複数回のリソグラフィ工程を実施することなく、多段の凸形状からなる微細3次元構造パターンを形成することが可能なパターン形成方法及びパターン形成体を提供する。

【解決手段】基板900の面上に第1と第2のエッチングマスク層100,200と、パターニング処理した第3層目のエッチングマスク301を積層し、この第1層目から第3層目のエッチングマスク層100,200、301において、隣接する上層のエッチングマスクをエッチング用マスクとして下層のエッチングマスクをエッチングし上層のエッチングマスクに形成されたパターンを下層のエッチングマスクに転写する。そして、第3層目のエッチングマスク301のパターンをトリミングした後、該トリミング後のエッチングマスクとエッチング後の第1及び第2層目のエッチングマスクを用いて基板を順にエッチングし、第1及び第2層目のエッチングマスクのパターンを基板900に転写する。

(もっと読む)

半導体装置の製造方法

【課題】低コスト化を図ることができる半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上にボロンを含む膜を形成する工程と、前記ボロンを含む膜上に酸化シリコンを含む膜を形成する工程と、前記酸化シリコンを含む膜をパターニングする工程と、前記パターニングされた前記酸化シリコンを含む膜をマスクとして、前記ボロンを含む膜を、塩素を含むガスを用いてエッチングする工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

二層レジストプラズマエッチングの方法

【課題】プラズマエッチング室内において、基板の上に形成された二層レジストをエッチングするための方法を提供する。

【解決手段】二層レジストの第1の層の上にパターンを形成された基板をエッチング室に導入する工程から開始される。次いで、SiCl4ガスがエッチング室に流し込まれる。次に、SiCl4ガスを流し入れつつエッチング室内においてプラズマを発生させる。次いで、二層レジストがエッチングされる。

(もっと読む)

埋め込みヘテロ構造半導体レーザの製造方法及び埋め込みヘテロ構造半導体レーザ

【課題】耐圧特性を十分に維持しながら放熱特性を向上させることが可能な埋め込みヘテロ構造半導体レーザの製造方法等を提供する。

【解決手段】埋め込みヘテロ構造半導体レーザの製造方法は、半導体基板1上に半導体積層9とマスク層11を形成する工程と、マスク層11を用いて半導体構造物10をエッチングすることにより、第1方向に沿って延びる半導体メサ15であって、第1方向と直交する第2方向において被エッチング領域17と隣接する半導体メサ15を形成する工程と、マスク層11を半導体メサ15上に残した状態で、被エッチング領域17の第1領域17A1のみに埋め込み層19Aを形成する工程と、上部電極25を形成する工程と、を備える。上部電極25は、半導体メサ15の上面15Tから被エッチング領域17の第2領域17A2に亘って形成されることを特徴とする。

(もっと読む)

プラズマエッチング方法

【課題】マスクをプラズマから保護することができ、形成する穴部の側壁を基板の表面に対して垂直にできるプラズマエッチング方法を提供する。

【解決手段】上方にパターニングされたシリコン酸化膜が形成されてなる被処理基板におけるシリコン層を第1の処理ガスによりエッチングして穴部を形成するプラズマエッチング方法において、一酸化炭素ガスを含む第2の処理ガスによりシリコン酸化膜の表面に保護膜を堆積させる第1の堆積ステップS11と、第1の処理ガスによりシリコン層をエッチングする第1のエッチングステップS12と、穴部の側壁に第2の処理ガスにより保護膜を堆積させる第2の堆積ステップS13と、第1の処理ガスによりシリコン層を更にエッチングする第2のエッチングステップS14とを有し、第2の堆積ステップS13と第2のエッチングステップS14とを少なくとも2回ずつ交互に繰り返す。

(もっと読む)

均一性を制御したエッチング

【課題】パターンを形成するエッチングに際してより均一なエッチングを可能にする方法を提供する。

【解決手段】ウエハ上に半導体素子を形成する方法が提供されている。エッチング層が、ウエハの上に形成される104。フォトレジストマスクが、エッチング層の上に形成される108。フォトレジストマスクは、ウエハの外縁付近のみ除去されて、ウエハの外縁付近のエッチング層が露出される112。炭素および水素を含有する種を備えた蒸着ガスが供給される116。蒸着ガスから、プラズマが形成される120。ポリマ層が、ウエハの外縁付近の露出エッチング層に蒸着される124。この時、ポリマは、蒸着ガス由来のプラズマから形成される。フォトレジストマスクと、ウエハの外縁付近の露出エッチング層に蒸着されたポリマとが消費されつつ、フォトレジストマスクを介してエッチング層がエッチングされる128。

(もっと読む)

半導体デバイスの製造方法

【課題】半導体ウェハの端部に欠けが発生するのを抑制することが可能で、且つ、製造歩留まりの向上を図ることが可能な半導体デバイスの製造方法を提供する。

【解決手段】半導体ウェハ121の表面側に薄膜部123を形成する薄膜部形成工程と、薄膜部123上にレジスト膜124を形成するフォトリソグラフィ工程と、レジスト膜124をエッチングマスクとして薄膜部123をエッチングすることで半導体ウェハ121の表面の一部121dを露出させる第1エッチング工程と、半導体ウェハ121の表面の一部121dから半導体ウェハ121をエッチングする第2エッチング工程とを備え、フォトリソグラフィ工程では、薄膜部123のうち半導体ウェハ121の端部131に形成されている部位123dにレジスト膜124を形成しないようにし、第1エッチング工程では、薄膜部123の上記部位123aをエッチング装置に設けた遮蔽物126によって保護する。

(もっと読む)

窒化物半導体発光素子の製造方法

【課題】成長用基板に形成された窒化物半導体層を容易に剥離できる窒化物半導体発光素子の製造方法を提供する。

【解決手段】窒化物半導体発光素子の製造方法では、第1のサイズd1を有する第1基板31に窒化物半導体層11を形成する。窒化物半導体層11上に第1のサイズd1より小さい第2のサイズd2を有する第1接着層12aを形成し、第2基板32上に第2接着層12b形成する。第1および第2接着層12a、12bを重ね合わせ、第1および第2基板31、32を張り合わせる。第2のサイズd2より大きいまたは等しい第3のサイズd3を有する凹部31aを生じるように第1基板31を除去する。凹部31aに薬液を注入し、窒化物半導体層11が露出するまで第1基板31をエッチングする。薬液で、露出した窒化物半導体層11を更にエッチングし、窒化物半導体層11の露出面を粗面化する。

(もっと読む)

シリコンウエハの加工方法及び貫通電極付3次元シリコンインターポーザ並びにチップサイズパッケージ

【課題】シリコンウエハに貫通孔を形成することが不可欠なチップサイズパッケージや3次元積層型のパッケージについて、シリコンウエハに直接識別記号を形成する技術を提供することを目的とした

【解決手段】少なくとも、シリコンウエハ上に感光性レジストを塗布する塗布工程、感光性レジストを所定のパターンを有する濃度分布マスクを介して露光する露光工程、感光性レジストにシリコンウエハが露出する開口部と露出しない開口部とを形成する現像工程、ドライエッチングにより感光性レジスト開口部に対応する部位のシリコンウエハを除去してシリコンウエハに導通用の貫通孔と非貫通孔から構成される識別記号とを同時に形成する工程、残余の感光性レジストを除去する工程、とを有することを特徴とするシリコンウエハの加工方法である。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

アモルファスカーボン膜の成膜方法、それを用いた半導体装置の製造方法、およびコンピュータ読取可能な記憶媒体

【課題】耐プラズマ性が高く、低温成膜が可能なアモルファスカーボン膜の成膜方法、およびそのようなアモルファスカーボン膜の成膜方法を適用した、半導体装置の製造方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器内に炭素と水素と酸素とを含む処理ガスを供給し、処理容器内の基板を加熱して処理ガスを分解して、基板上にアモルファスカーボン膜を堆積する。この方法を半導体製造装置のエッチングマスクの形成に適用して半導体装置を得る。

(もっと読む)

エッチングマスクスタックを用いたマルチマスクプロセス

【課題】基板の上のエッチング層内にエッチング特徴を形成するための方法が提供される。

【解決手段】エッチングマスクスタックが、エッチング層の上に形成される。第1のマスクが、エッチングマスクスタックの上に形成される。第1のマスクによって定められる間隔の幅を低減させる側壁層が、第1のマスクの上に形成される。側壁層を通して、第1組の特徴が、エッチングマスクスタック内へとエッチングされる。マスクおよび側壁層は、除去される。追加の特徴のステップが実施される。該ステップは、追加のマスクをエッチングマスクスタックの上に形成することと、側壁層を追加のマスクの上に形成することと、第2組の特徴を少なくとも部分的にエッチングマスクスタック内へとエッチングすることと、を含む。エッチングマスクスタック内の第1組の特徴および第2組の特徴を通して、複数の特徴がエッチング層内にエッチングされる。

(もっと読む)

モールドの製造方法

【課題】離型層としての堆積膜を表面に有するモールドの製造において、モールドの製造におけるスループットをより向上させることを可能とする。

【解決手段】離型層14としての堆積膜を表面に有するモールド1の製造において、堆積性ガス5a・5bを含むエッチングガスを用いて、石英基板10およびマスク層Mからなる構造体に所望の形状の凹凸パターンが形成されるとともに、堆積性ガス5a・5bの堆積物からなる堆積膜がこの凹凸パターンに沿って形成されるように石英基板10をプラズマエッチングする。

(もっと読む)

半導体装置及びその製法において用いられるアモルファスカーボン膜の製造法

【課題】ハードマスクとして好適に用いられるアモルファスカーボン膜の製造法を提供する。また、半導体装置における保護膜や封止膜に適したアモルファスカーボン膜の製造法を提供する。

【解決手段】プラズマ雰囲気形成領域を内部に有するチャンバーを備えるCVD装置を用意し、チャンバー内圧を6.66Pa以下、バイアス印加手段を介して成膜用の基体を設置するステージに印加するバイアスを100〜1500W、基体の成膜時の基体温度を200℃以下、成膜用の原料ガスの流量を100〜300cc/min.(0℃、大気圧)、プラズマ雰囲気を形成するための希ガスの流量を50〜400cc/min.(0℃、大気圧)とし、基体をプラズマ雰囲気に対面させ、基体上にアモルファスカーボン膜を形成する。

(もっと読む)

1 - 20 / 327

[ Back to top ]