Fターム[5F004EA00]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711)

Fターム[5F004EA00]の下位に属するFターム

マスク構成 (1,627)

アンダーエッチング、サイドエッチング (32)

ウェットエッチング (243)

サイドウォール (408)

反転エッチング (32)

抜きパターン (41)

リフトオフ (35)

斜めイオン入射、蒸着 (17)

ペリフェラルエッチング (9)

ダミー (47)

反射防止膜 (216)

エッチングストッパー (168)

フロー工程 (20)

エッチバック (120)

多段階エッチング (731)

低温ドライエッチング (2)

バイアススパッタ (15)

異なる領域を同時にエッチング (59)

位置合わせ (10)

気相エッチング (177)

エッチング形状の制御 (314)

マスクレスエッチング (327)

その他 (56)

Fターム[5F004EA00]に分類される特許

1 - 5 / 5

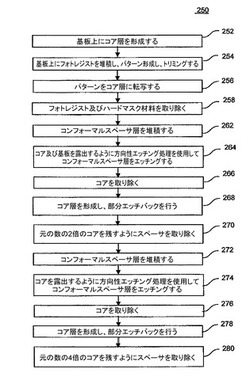

高度な微小寸法コンタクトのための自己整合多重パターン形成

【課題】 基板上の特徴部の密度を増大させる処理シーケンスを提供すること。

【解決手段】 本発明の実施形態は、単一の高解像度フォトマスクを使用する標準のフォトリソグラフィ処理技法を使用して可能なものに比較して、2次元において減少ピッチを有するパターン形成特徴部を基板上に形成する方法に関する。方形の角部の4つのコアの中心にディンプルを残すように選択された厚さを有するスペーサ層が、コアの2次元方形格子上に形成される。上記スペーサ層は、上記方形の中心において上記基板をさらすように、エッチングバックされる。上記コア材料を除去することにより、コアのフォトリソグラフィ画成格子のパターン密度が2倍とされる。露出された基板の領域には、再びコア材料を充填することができ、上記処理は、上記パターン密度が4倍となるように繰り返される。

(もっと読む)

半導体発光素子及び半導体発光素子の製造方法

【課題】光取り出し効率に優れ、且つ、低い駆動電圧で動作可能な半導体発光素子及びその製造方法を提供することを目的とする。

【解決手段】基板1と、基板1上に形成されたn型半導体層3、n型半導体層3に積層された発光層4及び発光層4に積層されたp型半導体層5とからなる積層半導体層15と、積層半導体層15の上面15aの全部または一部に形成された光取り出し効率向上のための凹凸部33と、積層半導体層15の凹凸部33を成す凸部33a上に積層された、p型半導体層5よりもドーパント濃度が高い高濃度p型半導体層8と、少なくとも高濃度p型半導体層8上に積層された透光性電流拡散層20と、を具備してなる半導体発光素子11を用いることにより、上記課題を解決できる。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】半導体素子の微細パターン形成方法に関し、露光装備の解像度の限界を克服するため二重パターニング(Double Patterning)工程を行うことにおいて、第1マスク工程と第2マスク工程を整列する工程が容易でなく不良が発生する。

【解決手段】半導体基板400上部にハードマスク層410及びエッチング静止膜420を形成する段階と、前記エッチング静止膜上部に犠牲酸化膜パターンを形成する段階と、前記犠牲酸化膜パターンの側壁にスペーサを形成する段階と、前記犠牲酸化膜パターンを除去する段階と、前記スペーサをマスクに前記エッチング静止膜及び前記ハードマスク層をエッチングしてハードマスクパターンを形成する段階とを含むことを特徴とする。

(もっと読む)

ナノパターン製造方法およびナノパターン基板、半導体メモリセル

【課題】

製造の複雑さを過度に増大させることなく、分子レベルで微細パターンの表面ラフネスを制御できる製造方法を提供すること。

【解決手段】

本発明のナノパターンの製造方法は基板に光異性化化合物を有する配向膜を形成する工程と、前記配向膜上に、主鎖および側鎖を有する液晶性高分子を含有する液晶層を形成する工程と、直線偏光している紫外線を前記配向膜に照射して、前記紫外線により光異性化した光異性化化合物に対応して前記液晶層の液晶性高分子の主鎖を所定方向に配向させる工程と、前記液晶層をマスクとして、前記基板の異方性ドライエッチングを行い、前記液晶性高分子の側鎖の長さに対応した一定のピッチの凸部を有するナノパターンを形成する工程とを備える構成とする。

(もっと読む)

微細パターン形成装置、その製造方法、および形成方法

【課題】 ナノインプリントによるパターニングのアライメント可能な微細パターン形成装置、その製造方法、および形成方法を提供する。

【解決手段】 ナノインプリントのモールドを、光等を透過可能なモールド基板に設け、このモールド基板に位置参照用のマークを設ける。ウェハにも、モールド基板のマークに対応したマークを形成する。モールド基板でのモールドの位置決めを精度良く行うために、ナノインプリントのモールドは、モールド基板にマークを形成した後に、マーク位置を参照して形成する。モールド基板にモールドとマークを形成することによって、ウェハ上側から、光等によってモールド基板を透過してモールド基板のマークとウェハのマークを同時に観察・参照することでウェハとモールドとの相対位置をアライメントする。

(もっと読む)

1 - 5 / 5

[ Back to top ]