Fターム[5F004EA03]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380)

Fターム[5F004EA03]の下位に属するFターム

Fターム[5F004EA03]に分類される特許

1 - 20 / 430

発光ダイオード

発光ダイオード

半導体装置の製造方法

【課題】膜パターンの倒れを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線技術を提供する。

【解決手段】第一の絶縁膜は、シリコン、酸素及び炭素を含むシロキサン構造を含む少なくとも1層以上の絶縁膜であり、第一の絶縁膜内部のシロキサン構造は炭素原子数がシリコン原子数よりも多く、第一の絶縁膜と金属との界面及び第一の絶縁膜と第二の絶縁膜との界面のうち少なくとも何れか一方に、第一の絶縁膜内部よりも単位体積当たりの炭素原子数が少なく、且つ酸素原子数が多い改質層が形成されていることを特徴とする半導体装置。

(もっと読む)

成膜装置及びその運用方法

【課題】処理容器内の処理空間に接する部材の表面に対するカーボン膜の密着性を向上させてパーティクルの発生を抑制することができる成膜装置の運用方法を提供する。

【解決手段】処理容器2内で保持手段22に保持された被処理体Wの表面にカーボン膜を成膜する成膜工程を行うと共に不要なカーボン膜を除去するためにクリーニングガスでクリーニング工程を行なうようにした成膜装置の運用方法において、成膜工程に先立って、処理容器内の処理空間に接する部材の表面にカーボン膜74の密着性を向上させ且つクリーニングガスに対して耐性を有する耐性プリコート膜70を形成す。これにより、カーボン膜の密着性を向上させ、しかも不要なカーボン膜を除去するクリーニング処理を行っても耐性プリコート膜を残存させる。

(もっと読む)

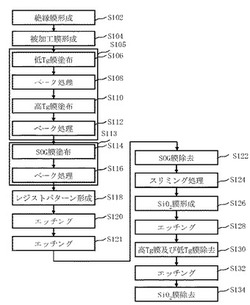

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

三次元ナノ構造体アレイ

【課題】複雑な構造で、高精確性を有し、且つ生産コストが低い三次元ナノ構造体アレイ及びその製造方法を提供することを目的とする。

【解決手段】本発明の三次元ナノ構造体アレイの製造方法は、基板を提供する第一ステップと、前記基板の表面にマスク層を設置する第二ステップと、前記マスク層を加工して、前記マスク層の表面に、並列した複数のストリップ状の突部構造を形成し、隣接する該ストリップ状の突部構造の間に、凹溝を形成させる第三ステップと、前記マスク層をエッチングして、前記凹溝と対応する領域における前記基板の表面を露出させる第四ステップと、エッチングによって、前記隣接するストリップ状の突部構造を二つずつ互いに接近させて、更に接触させ、三次元ナノ構造体予備成形物を形成する第五ステップと、前記マスク層を取り除き、三次元ナノ構造体アレイを形成する第六ステップと、を含む。

(もっと読む)

エッチング方法、エッチング装置、および記憶媒体

【課題】工程および装置構成を煩雑にすることなく、高エッチングレートで銅を異方性エッチングする装置、及びその方法を実施するプログラムを記憶した媒体を提供する。

【解決手段】チャンバ内に表面に銅膜104を有する基板101を配置し、チャンバ内を真空状態としつつ、チャンバ内に有機化合物106を供給し、銅膜に酸素ガスクラスターイオンビームを照射し、酸素ガスクラスターイオンビーム中の酸素ガスクラスターイオン107により、銅膜の銅を酸化させて酸化銅とするとともに、酸化銅と有機化合物を反応させて銅膜を異方的にエッチングする。

(もっと読む)

3Dフラッシュ構造用のエッチングプロセス

【課題】プラズマ処理室において、ウェハ上でスタックを形成するシリコン系の複数の二重層の中に高アスペクト比のフィーチャをエッチングするための方法を提供する。

【解決手段】プラズマ処理室に主エッチングガスが流入される。第1の圧力を提供しながら、主エッチングガスがプラズマにされる。20℃未満のウェハ温度が維持される。プラズマにより上記複数のシリコン系二重層のうちの複数の組を貫いてエッチングする間に、第1の圧力よりも低い第2の圧力まで圧力を降下させる。上記複数の二重層のうち第1の複数の組がエッチングされた後に、主エッチングガスの流入を停止させる。

(もっと読む)

パターン形成方法及びパターン形成体

【課題】複数回のリソグラフィ工程を実施することなく、多段の凸形状からなる微細3次元構造パターンを形成することが可能なパターン形成方法及びパターン形成体を提供する。

【解決手段】基板900の面上に第1と第2のエッチングマスク層100,200と、パターニング処理した第3層目のエッチングマスク301を積層し、この第1層目から第3層目のエッチングマスク層100,200、301において、隣接する上層のエッチングマスクをエッチング用マスクとして下層のエッチングマスクをエッチングし上層のエッチングマスクに形成されたパターンを下層のエッチングマスクに転写する。そして、第3層目のエッチングマスク301のパターンをトリミングした後、該トリミング後のエッチングマスクとエッチング後の第1及び第2層目のエッチングマスクを用いて基板を順にエッチングし、第1及び第2層目のエッチングマスクのパターンを基板900に転写する。

(もっと読む)

ダイヤモンド複合体

【課題】単結晶ダイヤモンドと多結晶ダイヤモンドの双方の利点を活かしながら、更に板状の構造を可能にするために、多結晶ダイヤモンドの研磨の困難性も回避し、研磨が容易なダイヤモンド複合体を提供すること。

【解決手段】少なくとも2種類の結晶性の異なる結晶からなる構造の複合体であり、その内の第一の結晶は高圧合成法により合成した単結晶ダイヤモンドか、あるいは気相合成法により合成した単結晶ダイヤモンドであり、第二の結晶は欠陥を面内に周期的なパターン形状で含む気相合成法により合成したダイヤモンドであり、該第一の結晶及び第二の結晶はいずれも、主面が平行になるように層状に形成されていることを特徴とするダイヤモンド複合体。

(もっと読む)

半導体装置およびその製造方法

【課題】 所望の深さを有し幅の狭い凹部を半導体基板に安定して形成することが可能な製造方法を提供すること。

【解決手段】 本発明は、半導体基板10の一部に酸素イオン注入を行うことで第1酸素含有領域24を形成する工程と、半導体基板10に熱処理を行い、第1酸素含有領域24に含まれる酸素を用いて第1酸素含有領域24を酸化させることで、第1酸素含有領域24を第1酸化領域26とする工程と、第1酸化領域26を除去することで半導体基板10に凹部16を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

パターン成形用構造体および微細パターン形成方法

【課題】レジストパターンの開口面積および開口率の大小あるいは開口形状によらず高い精度で微細パターンの形成が可能なパターン成形用構造体と微細パターン形成方法とを提供する。

【解決手段】パターン成形用構造体を、被エッチング体と、この被エッチング体の所望の面に位置するハードマスク材料層と、ハードマスク材料層上に位置するレジストパターンとを備えたものとし、レジストパターンは複数種の開口部を有するものとし、レジストパターンの開口部のうち、少なくともレジストパターンを介したハードマスク材料層のドライエッチング時のエッチング速度が最も大きい開口部内のハードマスク材料層上にレジストを存在させ、かつ、エッチング速度が最も大きい開口部内に存在するレジストを他の開口部内に存在するレジストよりも厚いものとする。

(もっと読む)

プラズマエッチング方法

【課題】マスクをプラズマから保護することができ、形成する穴部の側壁を基板の表面に対して垂直にできるプラズマエッチング方法を提供する。

【解決手段】上方にパターニングされたシリコン酸化膜が形成されてなる被処理基板におけるシリコン層を第1の処理ガスによりエッチングして穴部を形成するプラズマエッチング方法において、一酸化炭素ガスを含む第2の処理ガスによりシリコン酸化膜の表面に保護膜を堆積させる第1の堆積ステップS11と、第1の処理ガスによりシリコン層をエッチングする第1のエッチングステップS12と、穴部の側壁に第2の処理ガスにより保護膜を堆積させる第2の堆積ステップS13と、第1の処理ガスによりシリコン層を更にエッチングする第2のエッチングステップS14とを有し、第2の堆積ステップS13と第2のエッチングステップS14とを少なくとも2回ずつ交互に繰り返す。

(もっと読む)

発光素子

【課題】光抽出構造が形成されることで、発光効率及び信頼性を向上できる発光素子を提供する。

【解決手段】本発明の発光素子は、金属又は半導体からなる支持層;支持層上に位置する第1の電極;第1の電極上に位置し、発光層を含む多層構造の半導体層;及び半導体層上に配置され、少なくとも一つのホール又は柱形状の単位構造で形成される光抽出構造;を含む。光抽出構造はランダムに配置され、光抽出構造の高さは、nを光抽出構造が形成された物質の屈折率とし、λを発光層の中心波長とした場合にλ/2n〜3000ナノメートルであり、光抽出構造の周期又は隣接する単位構造の各中心間の平均距離は400〜3000ナノメートルであり、光抽出構造の単位構造はホール又は柱形状であり、単位構造の内側表面の半径と外側表面の半径とが互いに異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2膜33およびSiC膜35からなる積層膜36を形成し、この積層膜36をパターニングすることによりハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、当該エッチングによりSiC膜35から解離したCを含む反応生成物を含む側壁保護膜32を、エッチング途中のAlCu膜30の側面に形成しながらAlCu配線層34をパターニングすることによって、第1AlCu配線20を形成する。

(もっと読む)

半導体デバイスの製造方法

【課題】半導体ウェハの端部に欠けが発生するのを抑制することが可能で、且つ、製造歩留まりの向上を図ることが可能な半導体デバイスの製造方法を提供する。

【解決手段】半導体ウェハ121の表面側に薄膜部123を形成する薄膜部形成工程と、薄膜部123上にレジスト膜124を形成するフォトリソグラフィ工程と、レジスト膜124をエッチングマスクとして薄膜部123をエッチングすることで半導体ウェハ121の表面の一部121dを露出させる第1エッチング工程と、半導体ウェハ121の表面の一部121dから半導体ウェハ121をエッチングする第2エッチング工程とを備え、フォトリソグラフィ工程では、薄膜部123のうち半導体ウェハ121の端部131に形成されている部位123dにレジスト膜124を形成しないようにし、第1エッチング工程では、薄膜部123の上記部位123aをエッチング装置に設けた遮蔽物126によって保護する。

(もっと読む)

窒化物半導体発光素子の製造方法

【課題】成長用基板に形成された窒化物半導体層を容易に剥離できる窒化物半導体発光素子の製造方法を提供する。

【解決手段】窒化物半導体発光素子の製造方法では、第1のサイズd1を有する第1基板31に窒化物半導体層11を形成する。窒化物半導体層11上に第1のサイズd1より小さい第2のサイズd2を有する第1接着層12aを形成し、第2基板32上に第2接着層12b形成する。第1および第2接着層12a、12bを重ね合わせ、第1および第2基板31、32を張り合わせる。第2のサイズd2より大きいまたは等しい第3のサイズd3を有する凹部31aを生じるように第1基板31を除去する。凹部31aに薬液を注入し、窒化物半導体層11が露出するまで第1基板31をエッチングする。薬液で、露出した窒化物半導体層11を更にエッチングし、窒化物半導体層11の露出面を粗面化する。

(もっと読む)

基板の製造装置および基板の製造方法

【課題】エッチング対象が透光性を有し、且つパターンが微細である場合であってもエッチング処理の終点検出の精度を向上させることができる基板の製造装置および基板の製造方法を提供することである。

【解決手段】実施形態に係る基板の製造装置は、処理容器と、前記処理容器の内部にガスを供給するガス供給部と、前記処理容器の内部を排気する排気部と、前記処理容器の内部にプラズマを発生させるプラズマ発生部と、前記処理容器の内部に設けられ基板を載置する載置部と、前記載置部に載置された前記基板の前記載置部に対峙する側の面に検出光を入射させ、前記基板からの反射光に基づいてエッチング処理の終点を検出する終点検出部と、を備えている。そして、前記終点検出部は、前記基板の前記面に対して垂直な方向から前記検出光を入射させ、前記基板の透光性を有する材料から形成された部分における前記エッチング処理の終点を検出する。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜を確実に除去して半導体装置の欠陥発生を低減する。

【解決手段】第1の層間絶縁膜の上に、絶縁膜と、反射防止膜と、レジスト膜とを順番に形成する。レジスト膜を用いて反射防止膜と絶縁膜をエッチングし、絶縁膜からハードマスクを作成する。この後、ラジカル照射によってレジスト膜と反射防止膜を除去する。ラジカル照射は、基板温度を100℃、150℃、250℃と順番に上昇させながら行う。基板温度が低い初期段階では、反射防止膜の膜材料の飛散防止と、反射防止膜の表面に残留する他の物質の除去が行われる。この後、基板温度を高くすることで、反射防止膜が確実に除去される。

(もっと読む)

1 - 20 / 430

[ Back to top ]