Fターム[5F004EA06]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380) | SiO2膜 (416)

Fターム[5F004EA06]に分類される特許

1 - 20 / 416

プラズマエッチング方法

半導体装置の製造方法

【課題】酸化シリコン層又は窒化シリコン層が側壁部に形成されたシリコン含有層の除去を、残渣が生じることなく、かつ、下層膜のロスを生じさせずに行うことができ、良質な半導体装置を製造することのできる半導体装置の製造方法を提供する。

【解決手段】基板上に形成され、パターニングされたシリコン含有層の側壁部を窒化シリコン層又は酸化シリコン層で覆うように窒化シリコン層又は酸化シリコン層を形成する成膜工程と、シリコン含有層を選択的に除去し、側壁部に形成された窒化シリコン層又は酸化シリコン層を残すプラズマエッチング工程とを具備した半導体装置の製造方法であって、プラズマエッチング工程では、SF6ガスを含むエッチングガスを用いる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置に含まれる炭化珪素層の側面の面方位を特定の結晶面により近づけることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板1上に、主表面が設けられた炭化珪素層19が形成される。炭化珪素層19の主表面の一部を覆うマスク17が形成される。主表面に対して傾斜した側面SSが炭化珪素層19に設けられるように、マスク17が形成された炭化珪素層19の主表面に対して、塩素系ガスを用いた熱エッチングが行われる。熱エッチングを行う工程は、塩素系ガスの分圧が50%以下である雰囲気下で行われる。

(もっと読む)

エッチング方法

【課題】被加工材とレジストのエッチングの選択比を高くすることのできるエッチング方法、、このエッチング方法により加工されたサファイア基板、及び、このサファイア基板を備える発光素子を提供する。

【解決手段】プラズマエッチング装置を用いたエッチング方法であって、被加工材上にレジスト膜を形成するレジスト膜形成工程と、前記レジスト膜に所定のパターンを形成するパターン形成工程と、前記パターンが形成された前記レジスト膜を所定の変質用条件にてプラズマに曝し、前記レジスト膜を変質させてエッチング選択比を高くするレジスト変質工程と、被加工材を変質用条件と異なるエッチング用条件にてプラズマに曝し、エッチング選択比が高くなった前記レジスト膜をマスクとして被加工材のエッチングを行う被加工材のエッチング工程と、を含むようにした。

(もっと読む)

半導体装置の製造方法

【課題】膜パターンの倒れを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

(もっと読む)

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

配線構造及びその製造方法

【課題】配線間の絶縁性に優れ信頼性の高い配線構造及びその製造方法を提供する。

【解決手段】スピンコート法により、ベースポリマーがポリイミド樹脂である非感光性樹脂のワニスを塗布後、ベーク、キュアしてポリイミド樹脂を硬化、膜を形成する。これを第1絶縁膜12とする。次いで、めっきシード層18形成、フォトレジスト溝パターン22形成、めっき、フォトレジスト溝パターン22除去、配線下以外のめっきシード層18除去に依り、第1の絶縁膜上に配線26を形成する。そして、第1絶縁膜の表面上にシリカ粒子30を分散し、散したシリカ粒子30をマスクとして、CF4及びO2を混合したガスで、第1絶縁膜12をドライエッチングすることに依り、段差が100nm以上の凹凸32を形成する。最後に前述と同様にして、スピンコート法により、第2絶縁膜としてのポリイミド樹脂膜34を形成する。

(もっと読む)

パターン形成方法及びパターン形成体

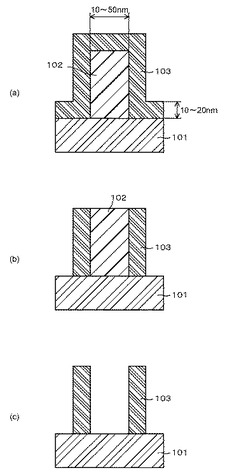

【課題】複数回のリソグラフィ工程を実施することなく、多段の凸形状からなる微細3次元構造パターンを形成することが可能なパターン形成方法及びパターン形成体を提供する。

【解決手段】基板900の面上に第1と第2のエッチングマスク層100,200と、パターニング処理した第3層目のエッチングマスク301を積層し、この第1層目から第3層目のエッチングマスク層100,200、301において、隣接する上層のエッチングマスクをエッチング用マスクとして下層のエッチングマスクをエッチングし上層のエッチングマスクに形成されたパターンを下層のエッチングマスクに転写する。そして、第3層目のエッチングマスク301のパターンをトリミングした後、該トリミング後のエッチングマスクとエッチング後の第1及び第2層目のエッチングマスクを用いて基板を順にエッチングし、第1及び第2層目のエッチングマスクのパターンを基板900に転写する。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

磁気記録媒体

【課題】磁気記録媒体のような被エッチング材料の表裏両面へのプラズマ処理を行う際、基板の材質に関わらず被エッチング材料両表面に効率よくバイアスを印加し、両面処理ができるプラズマエッチング装置及びその方法を提供する。

【解決手段】略円環状の被エッチング材料に高周波電力を印加する一対の導電体を有し、略円環状の被エッチング材料の内縁を一対の導電体で挟持することで、略円環状の被エッチング材料の両面をエッチングするプラズマエッチング装置において、前記一対の導電体の一方に設置された導電体接続部材により、該略円環状の被エッチング材料の両面が電気的に導通するようにした。

(もっと読む)

プラズマエッチング方法

【課題】ワイドギャップ半導体基板にテーパ状の凹部を形成することができるプラズマエッチング方法を提供する。

【解決手段】まず、ワイドギャップ半導体基板Kの表面に開口部を有したマスクMを形成する。そして、マスクMが形成されたワイドギャップ半導体基板Kを基台に載置し、当該ワイドギャップ半導体基板Kを200℃以上に加熱した後、処理チャンバ内に供給されたエッチングガス及び保護膜形成ガスをプラズマ化するとともに、基台にバイアス電位を与え、プラズマ化されたエッチングガスによるワイドギャップ半導体基板Kのエッチングと、プラズマ化された保護膜形成ガスによる保護膜の形成とを並行して行い、保護膜によって保護しつつ、炭化ケイ素基板Kのエッチングを進行させ、炭化ケイ素基板Kにテーパ状の凹部を形成する。

(もっと読む)

有機膜の除去方法

【課題】低誘電率絶縁膜の誘電率の上昇を抑制しつつ、確実に有機膜の除去を行うことのできる有機膜の除去方法を提供する。

【解決手段】少なくともシリコンと酸素と炭素とを含み、二酸化シリコンよりも誘電率の低い低誘電率絶縁膜と、低誘電率絶縁膜の上層に形成された有機膜と、を含む積層構造のパターンが形成された被処理基板の有機膜を除去する有機膜の除去方法であって、酸素又は窒素を含む第1のガスと、CxHy(x,yは正の整数)で示される第2のガスと、水素ガスとの混合ガスのプラズマを被処理基板に作用させて有機膜を除去する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】チャネル移動度を高め、かつチャネル長のばらつきを抑制することができる炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】基板1には、基準面から5度以内のオフ角を有する主表面MSが設けられている。基準面は、六方晶系の場合は{000−1}面であり、立方晶系の場合は{111}面である。炭化珪素層は基板の主表面MS上にエピタキシャルに形成されている。炭化珪素層には、互いに対向する第1および第2の側壁20a、20bを有する溝6が設けられている。第1および第2の側壁20a、20bの各々はチャネル領域を含む。また第1および第2の側壁20a、20bの各々は、六方晶系の場合は実質的に{0−33−8}面および{01−1−4}面のいずれか一方を含み、立方晶系の場合は実質的に{100}面を含む。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】特性の安定した高品質の半導体装置を得ることができる、半導体装置の製造方法を提供する。

【解決手段】炭化珪素層上に堆積法によってマスク層17が形成される。マスク層17がパターニングされる。パターニングされたマスク層17をマスクとして用いたエッチングによって炭化珪素層を部分的に除去することで、側壁20を有するゲート溝6が形成される。ゲート溝6の側壁20上にゲート絶縁膜が形成される。ゲート絶縁膜上にゲート電極が形成される。炭化珪素層は六方晶および立方晶のいずれかの結晶型を有し、ゲート溝の側壁は、炭化珪素層の結晶型が六方晶の場合には実質的に{0−33−8}面および{01−1−4}面のいずれか一方を含み、炭化珪素層の結晶型が立方晶の場合には実質的に{100}面を含む。

(もっと読む)

半導体装置の製造方法

【課題】低コスト化を図ることができる半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上にボロンを含む膜を形成する工程と、前記ボロンを含む膜上に酸化シリコンを含む膜を形成する工程と、前記酸化シリコンを含む膜をパターニングする工程と、前記パターニングされた前記酸化シリコンを含む膜をマスクとして、前記ボロンを含む膜を、塩素を含むガスを用いてエッチングする工程と、を備える。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】複雑な構成を必要としない、スパッタエッチングの均一性を調整する手段を備えたプラズマ処理装置を提供する。

【解決手段】対向する一対の電極5a,5bの外周部に異極同士が対向するように永久磁石8a,8bを設置し、各電極の外周の前方近傍から中心寄りの電極表面に至る部分にマグネトロン磁場(半円筒形磁場)が、一対の電極の外周部間に電極表面に垂直方向の対向磁場が形成できるようにし、各電極にプラズマ電力を供給し、導入口2よりアルゴンなどを供給して、一方の電極5b上に載置した被処理基板13に対しプラズマエッチングを行う。各電極の背面に磁場調整手段12a,12bを設けてプラズマ空間の磁場を調整してエッチングの均一性を調整する。

(もっと読む)

液体吐出装置の流路板の製造方法

【課題】貫通孔の側壁を平坦に加工することのできる液体吐出装置の流路板の製造方法を提供する。

【解決手段】本発明の一実施形態に係る液体吐出装置の流路板の製造方法は、面方位が{110}であるシリコン基板の一方の面と他方の面とを貫通する貫通孔と、前記一方の面側に形成され前記貫通孔と接続する流路と、を備えた液体吐出装置の流路板の製造方法であって、前記シリコン基板の前記一方の面上に第1マスクを形成し、前記第1マスク上に第2マスクを形成するマスク形成工程と、前記第2マスクを介して少なくとも一部にドライエッチングを含むエッチングを行い、前記貫通孔を形成する貫通孔形成工程と、前記第2マスクを除去した後、前記第1マスクを介して前記貫通孔に対して結晶異方性エッチングを行い、前記貫通孔の側壁面を、前記シリコン基板の面方位{111}の面で構成するように前記貫通孔の側壁を加工する側壁加工工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

半導体基板を均一にエッチングするためのガス噴射

【課題】半導体基板を改良された限界寸法均一性でエッチングする方法を提供する。

【解決手段】誘導結合プラズマエッチングチャンバ内の基板支持体上に半導体基板を支持することと、第1のエッチングガスをシャワーヘッドノズル23により半導体基板の上の中央領域に供給することと、少なくとも1種類のシリコン含有ガスを含む第2のガスであって、第2のガス中のシリコン濃度が第1のエッチングガス中のシリコン濃度より高い第2のガスをプラズマチャンバの側壁を通して噴射器20により半導体基板の上の中央領域を囲む周辺領域に供給することと、第1のエッチングガスおよび第2のガスからプラズマを発生させることと、半導体基板の露出面をプラズマエッチングすることとを含む。

(もっと読む)

半導体基板の製造方法

【課題】トレンチ内を結晶性の高いエピタキシャル膜で埋めることができ、特にpnコラムの形成に適する半導体基板の製造方法を提供する。

【解決手段】ドライエッチングにより半導体基板10aにトレンチT1を形成するトレンチ形成工程と、120℃以下の低温で行うケミカルドライエッチング(CDE)またはウエットエッチングによりトレンチT1の表層部をエッチングして、第1ダメージ層D1を除去する第1ダメージ層除去工程と、半導体基板10aを非酸化性かつ非窒化性の雰囲気下において1050℃以上の高温で熱処理を行い、第1ダメージ層D1の下層に存在する第2ダメージ層D2の結晶性を回復する第2ダメージ層回復工程と、トレンチT1内にエピタキシャル膜3を形成して、トレンチT1をエピタキシャル膜3で埋め込むトレンチ埋め込み工程とを有してなる半導体基板10の製造方法とする。

(もっと読む)

1 - 20 / 416

[ Back to top ]