Fターム[5F004EA11]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | サイドウォール (408)

Fターム[5F004EA11]の下位に属するFターム

Fターム[5F004EA11]に分類される特許

1 - 20 / 45

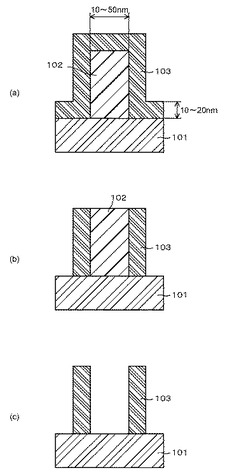

半導体装置の製造方法

【課題】酸化シリコン層又は窒化シリコン層が側壁部に形成されたシリコン含有層の除去を、残渣が生じることなく、かつ、下層膜のロスを生じさせずに行うことができ、良質な半導体装置を製造することのできる半導体装置の製造方法を提供する。

【解決手段】基板上に形成され、パターニングされたシリコン含有層の側壁部を窒化シリコン層又は酸化シリコン層で覆うように窒化シリコン層又は酸化シリコン層を形成する成膜工程と、シリコン含有層を選択的に除去し、側壁部に形成された窒化シリコン層又は酸化シリコン層を残すプラズマエッチング工程とを具備した半導体装置の製造方法であって、プラズマエッチング工程では、SF6ガスを含むエッチングガスを用いる。

(もっと読む)

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

レジストパターン形成方法およびそれを用いたパターン化基板の製造方法

【課題】レジストパターンの形成において、残膜をエッチングする工程後のレジストパターンの凸部の幅が、残膜をエッチングする工程前におけるレジストパターンの凸部の幅以上の所望の幅となることを可能とする。

【解決手段】凹凸パターンが転写されたレジスト膜2の残膜エッチング工程が、エッチングの際に堆積物4を生成する堆積性ガスを含有する第1のエッチングガスを用いて、レジストパターンにおける凸部の側壁に堆積物4が堆積しかつ残膜がエッチングされる条件でレジスト膜2をエッチングする第1のエッチング工程を含み、堆積物4を含めた上記凸部の幅が残膜エッチング工程前における上記凸部の幅以上の所望の幅となるように第1のエッチング工程以後の工程によってレジスト膜2をエッチングする。

(もっと読む)

プラズマ処理方法

【課題】本発明は、密部スペース幅20nm以下のパターンにおいて、疎密マイクロローディングの低減を可能とするプラズマ処理方法を提供する。

【解決手段】本発明は、シリコン基板上に密部スペース幅20nm以下のパターンのマスクを有する試料のシリコンをプラズマエッチングするプラズマ処理方法において、Cl2ガスとN2ガスの混合ガスを用い、0.1Pa以下の圧力で、デューティー比5%〜50%の時間変調された間欠的な高周波電力を前記試料に印加しながら、シリコンのエッチングを行うことを特徴とするプラズマ処理方法である。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

残存フォトレジスト及び残留側壁パッシベーションを除去する、その場でのポストエッチング工程

【課題】金属エッチングと、残存フォトレジスト及び残留側壁パッシベーションの剥離のための改良された技術を提供する。

【解決手段】単一のエッチングチャンバ内で、金属エッチングと、エッチングマスク剥離と、残留側壁パッシベーションの除去とを実行する方法。ウエハは、エッチングチャンバ内に配置される。ウエハ上で、金属エッチングが実行される。酸素とアルゴンとの混合物等の剥離ガスが、エッチングチャンバに提供され、酸素プラズマを形成するために励起される。酸素プラズマは、エッチングマスクをウエハから剥離させ、残留側壁パッシベーションを除去する。酸素プラズマは、更に、エッチングチャンバをクリーニングする。

(もっと読む)

半導体装置の製造方法

【目的】マスクの厚さを所定の値にし、後退量とエッチング量の比を所定の値にしてトレンチの開口部の端部を丸めることで、ゲート酸化膜形成温度を950℃未満の低い処理温度にした場合でもゲート酸化膜の良好な耐圧特性と長期信頼性が得られる半導体装置の製造方法を提供すること。

【解決手段】マスクであるシリコン酸化膜2の端部10をトレンチ8の開口部9の端部Aから後退させる量Xと、等方性ドライエッチングによるエッチング量Yとの比(X/Y)を2以上5以下に設定することで、Qbdの値を高くすることができて、良好なトレンチ8の開口部9の端部Aと段差12の端部Bの形状を丸めることができる。その結果、その後形成するゲート酸化膜14の熱処理温度を、950℃未満、あるいは、900℃以下で行った場合でも、ゲート酸化14の良好な耐圧特性と長期信頼性を得ることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】D−RAMのキャパシタを形成するシリンダのドライエッチ加工において、従来技術の製造方法ではアスペクト比が高いシリンダやコンタクトの形状がボーイング形状となり隣接するホール間ショートの問題やホール内に形成する電極成膜のカバレッジ異常などの問題が発生する。

【解決手段】本発明ではシリコン酸化膜4aにコンタクトホールを形成する際にボーイングが発生する部分にLow−k膜の炭化シリコン酸化膜5を挿入して積層構造とし、ドライエッチでシリコン酸化膜4aのエッチング速度に対し、炭化シリコン酸化膜5のエッチング速度が1/5〜1/10と遅い条件にすることでボーイング形状の抑制を可能にした。

(もっと読む)

半導体装置の製造方法

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】スペーサーを形成すべき凸部の相互間隔、溝の幅、又は孔の径が小さい場合に、基板保護膜を用いる必要がなく、かつノッチを生じさせずにスペーサーを形成する。

【解決手段】スペーサーを形成する時の異方性エッチングにおいて、「1−(異方性エッチングおける第2スペーサー形成膜5の垂直方向のエッチングレートに対する水平方向のエッチングレートの比)」を異方性度と定義し、「(第1スペーサー形成膜4の膜厚T1−第2スペーサー形成膜5の膜厚T2)/(第1スペーサー形成膜4の膜厚T1)」を第1スペーサー形成膜4の第2スペーサー形成膜5に対する膜厚増分率と定義した時に、第2スペーサー形成膜5の垂直方向のエッチングレートを第1スペーサー形成膜4の垂直方向のエッチングレートより小さく、かつ第1スペーサー形成膜4の垂直方向のエッチングレートに異方性度と膜厚増分率のうち小さい方を乗じた値より大きいエッチング条件にする。

(もっと読む)

半導体装置の製造方法

【課題】微細なパターンを精度良く形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工体1上にCを含む材料からなる芯材2を選択的に形成する工程と、芯材2の上面および側面を覆うように、酸素を含まない材料からなる保護膜3を形成する工程と、保護膜3を介して芯材2と被加工体1を覆うように酸化膜4を形成する工程と、芯材2の側方に少なくとも酸化膜4からなる側壁5を加工形成する工程と、少なくとも芯材2を除去した後、側壁5をマスクとして用いて被加工体1をエッチングし、側壁5のパターンを転写する工程と、を含む。

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPにおいて、側壁部の形状の対称性を高め、被エッチング膜をエッチングするときの加工精度を向上させることができるマスクパターンの形成方法を提供する。

【解決手段】基板上の被エッチング膜の上に形成されたシリコン膜よりなる第1のライン部が配列したシリコン膜パターンの表面を等方的に被覆するように、カーボン膜を成膜する成膜工程S18と、カーボン膜を第1のライン部の上部から除去すると共に、第1のライン部の側壁部として残存するように、カーボン膜をエッチバックするエッチバック工程S19と、第1のライン部を除去し、側壁部が配列したマスクパターンを形成するシリコン膜除去工程S20とを有する。

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPによりマスクパターンを形成する場合に、反射防止膜のエッチング工程を省略し、マスクパターンのパターン倒れを防止することができるマスクパターンの形成方法を提供する。

【解決手段】レジストパターン列の表面を等方的に酸化シリコン膜で被覆するステップS14と、レジストパターン列の間をカーボン膜で埋め込むと共に、上部をカーボン膜で被覆するステップS15と、カーボン膜を、レジストパターン列の上部から除去すると共に、レジストパターン列の間に残存するようにエッチバック処理するステップS16と、残存するカーボン膜を除去すると共に、レジストパターン列の上部を被覆する酸化シリコン膜をエッチバック処理するステップS17と、レジストパターン列をアッシング処理し、中央部と、中央部を両側から挟む膜側壁部とを有する、酸化シリコン膜よりなる第1のマスクパターン列を形成するステップS18とを有する。

(もっと読む)

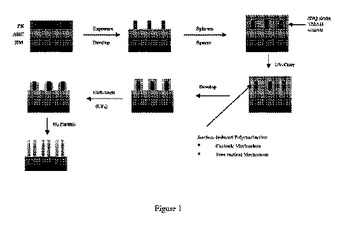

ダブルパターニング方法及び材料

シルセスキオキサン樹脂をパターン形成フォトレジストの上に塗布し、硬化して、パターン表面上に硬化シルセスキオキサン樹脂を生成する。次に未硬化シルセスキオキサン樹脂を除去し、パターン表面上に硬化シルセスキオキサン樹脂を残す。水平表面上の硬化シルセスキオキサン樹脂を除去し、下にあるフォトレジストを露光する。このフォトレジストを除去し、硬化シルセスキオキサンのパターンを残す。任意で、新規パターンを下層へ転写することができる。  (もっと読む)

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】多層レジストや、メタルゲート/High−k等の積層膜のドライエッチング加工において、高精度の加工精度が要求される。

【解決手段】複数層の連続エッチング加工において、エッチング後の寸法測定することなく、加工の形状または寸法を、真空処理室1の内壁または半導体基板4と、真空処理室1内に生成されたプラズマとの間の電荷量に応じて変動するバイアス電位を計測し、また、プラズマ中の波長の異なる各イオン種の発光強度を測定し、これらから予め設定したモデル式にて、各膜種のエッチング処理毎に、エッチング後の各膜種の加工寸法を予測し、次の膜のエッチング後寸法が、所定の寸法値になるよう処理条件を変更し、連続して次の膜種のエッチング処理を行うことで、寸法や形状を補正するドライエッチング方法および装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】露光可能限界寸法よりも小さい間隔のパターンを形成することができる半導体装置の製造方法を提供する。

【解決手段】基板10上に形成された被加工膜11上にレジスト膜23を形成する工程と、前記レジスト膜を露光、現像し、第1の方向に伸長し、前記第1の方向に垂直な第2の方向にくびれ部を有する開口パターン31Aを形成する工程と、ガス存在雰囲気下で前記レジスト膜上に前記ガスを構成する元素を含む堆積物24を堆積し、前記くびれ部における前記開口パターンの底部を前記第2の方向に前記堆積物で接続した膜パターン25を形成する工程と、前記膜パターンが転写されるように、ドライエッチング法によって前記被加工膜をエッチングする工程と、を含む。

(もっと読む)

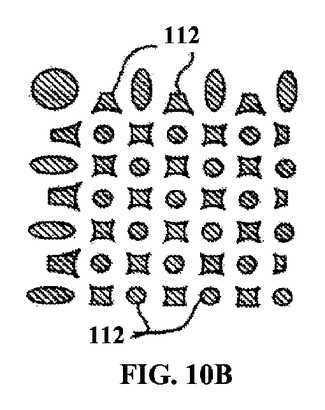

柱状構造のためのレジストフィーチャおよび除去可能スペーサピッチを倍増するパターニング法

半導体装置を製作する方法が、基板上に少なくとも1つの層を形成することと、少なくとも1つの層の上に画像形成性材料よりなる少なくとも2つの離間されたフィーチャを形成することと、少なくとも2つのフィーチャ上に側壁スペーサを形成することと、第1のフィーチャ上の第1の側壁スペーサと第2のフィーチャ上の第2の側壁スペーサとの間の空間をフィラーフィーチャで充填することと、を含む。この方法はまた、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャを互いに離間した状態で残すように、側壁スペーサを選択的に除去することと、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャをマスクとして使用して少なくとも1つの層をエッチングすることと、を含む。  (もっと読む)

(もっと読む)

プラズマエッチング装置及びプラズマクリーニング方法

【課題】処理容器内のクリーニング性能を確保しつつ、被処理体を載置する高周波電極に設けられる静電チャックのエロージョンを効率的に低減する。

【解決手段】真空排気可能な処理容器10に上部電極38と下部電極12とが平行に配置され、下部電極12には第1高周波電源32より第1整合器34を介して第1の高周波が印加される。制御部68は、半導体ウエハWの無い処理容器10内で行われるプラズマクリーニングに際して、プラズマ生成に寄与する第1の高周波が、プラズマを生成させる第1の振幅を有する第1の期間と、プラズマを実質的に生成させない第2の振幅を有する第2の期間とを所定の周期で交互に繰り返すように、第1高周波電源32を制御する。

(もっと読む)

1 - 20 / 45

[ Back to top ]