Fターム[5F004EA13]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | サイドウォール (408) | 側壁保護膜の形成 (258)

Fターム[5F004EA13]に分類される特許

1 - 20 / 258

半導体装置の製造方法、半導体エッチングプロセスにおける計測方法

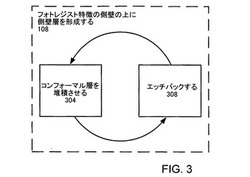

ラインエッジ粗さを低減させた特徴のエッチング

【課題】ラインエッジ粗さを低減させて特徴をエッチングする

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

(もっと読む)

ノズルプレートの製造方法及び流体噴射ヘッドの製造方法

【課題】テーパー形状と垂直形状が連通した形状を効率的に形成できる微細構造の形成方法及び流体噴射ヘッドの製造方法の提供。

【解決手段】基板1に垂直な側壁部を有する第1開口部7と、第1開口部7と連通するテーパー状の側壁部を有する第2開口部10と、を備えた微細構造の形成方法であって、基板1上に階段状の構造を有する貫通孔5を備えたマスク2を形成する第1工程と、マスク2を介してドライエッチング工程と、保護膜8を形成するパッシベーション工程とを交互に連続して繰り返すことにより第1開口部7と第2開口部10とを形成する第2工程と、を備え、第2工程では、ドライエッチングにおけるエッチング量をパッシベーションにおいて形成される保護膜8の量よりも多くし、第2開口部10の側壁部となる基板1の一部をエッチングしつつ第1開口部7の底面をエッチングすることで、第2開口部10の側壁部をテーパー状に形成する。

(もっと読む)

プラズマ処理装置

【課題】カバレージ性の高い、面内均一性に優れたプラズマ処理方法及びプラズマ処理装置を提供する。

【解決手段】プラズマによりターゲット(31)から叩き出されたスパッタ粒子を基板(W)の表面に堆積させるに際して、そのスパッタ粒子をプラズマで分解して活性種を生成した後、基板表面へ堆積させる。これにより、プラズマCVDに類似した成膜形態が得られ、カバレージ性の高い、面内均一性に優れたスパッタ成膜が可能となる。特に、プラズマ源に高周波電場と環状磁気中性線(25)を用いているので、磁場ゼロ領域で非常に高密度なプラズマを効率よく発生させることができる。このプラズマは、磁気中性線の形成位置、大きさを任意に調整することで面内均一性の高いプラズマ処理が実現可能となる。

(もっと読む)

基板処理方法

【課題】処理対象の基板に対し、半導体デバイスの小型化要求を満たす寸法の開口部であって、エッチング対象膜に転写するための開口部をマスク膜又は中間膜に形成する基板処理方法を提供する。

【解決手段】アモルファスカーボンの下層レジスト膜71、ハードマスクとしてのSiON膜72、反射防止膜73及びフォトレジスト膜74が順に積層されたシリコン基材70において、CF3IガスとH2ガスとの混合ガスから生成されたプラズマによってフォトレジスト膜74の開口部75の側壁面にデポ76を堆積させて開口部75の開口幅を縮小させるシュリンク工程と、反射防止膜73及びSiON膜72をエッチングするエッチング工程とを1ステップで行う。

(もっと読む)

プラズマエッチング方法

【課題】ワイドギャップ半導体基板にテーパ状の凹部を形成することができるプラズマエッチング方法を提供する。

【解決手段】まず、ワイドギャップ半導体基板Kの表面に開口部を有したマスクMを形成する。そして、マスクMが形成されたワイドギャップ半導体基板Kを基台に載置し、当該ワイドギャップ半導体基板Kを200℃以上に加熱した後、処理チャンバ内に供給されたエッチングガス及び保護膜形成ガスをプラズマ化するとともに、基台にバイアス電位を与え、プラズマ化されたエッチングガスによるワイドギャップ半導体基板Kのエッチングと、プラズマ化された保護膜形成ガスによる保護膜の形成とを並行して行い、保護膜によって保護しつつ、炭化ケイ素基板Kのエッチングを進行させ、炭化ケイ素基板Kにテーパ状の凹部を形成する。

(もっと読む)

急速交互プロセス(RAP)のリアルタイム制御のためのシステム、方法、及び装置

【課題】急速交互プロセス(RAP)制御技術を提供する。

【解決手段】RAPシステム、及びこれを動作させる方法は、RAPチャンバ(RAPC)と、これに結合され、対応するプロセスガス源流量コントローラを各々が含む、複数のプロセスガス源と、RAPCに結合されたバイアス信号源と、RAPCに結合されたプロセスガス検出器と、RAPC、バイアス信号源、プロセスガス検出器、及び複数のプロセスガス源に結合されたRAPCコントローラとを含み、RAPCコントローラは、第1のRAP段階を開始させるためのロジックを含み、該第1のRAP段階を開始させるためのロジックは、第1のプロセスガスをRAPCに投入するためのロジックと、RAPCの中で第1のプロセスガスを検出するためのロジックと、RAPCの中で第1のプロセスガスが検出された後に、対応する第1の段階バイアス信号をRAPCに印加するためのロジックとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

単粒子膜エッチングマスクを有する表面微細凹凸構造体形成基板の製法

【課題】太陽光発電基板面のサブ波長反射防止微細構造のような反射防止微細凹凸構造の形成に好適な単粒子膜エッチングマスクを有する基板の製造方法を提供する。

【解決手段】易揮発性分散媒中の球形単粒子分散液を調製する工程、該単粒子分散液を、該単粒子及び該分散媒と非親和性の液体収容槽中の液体面に滴下して単粒子分散液膜を形成する工程、該単粒子分散液膜中の分散媒を揮発させて単粒子が2次元に最密充填配列している単粒子膜を形成する工程、単粒子膜を基板面に移し取る工程を有する。

(もっと読む)

ドライエッチング方法

【課題】本発明は、ダミー材料の除去により形成される溝や孔に容易にトップラウンドを設けることができるドライエッチング方法を提供する。

【解決手段】本発明は、層間酸化膜に周囲を囲まれたダミー材料を除去することにより溝または孔を形成するドライエッチング方法において、前記ダミー材料を所定の深さまでエッチングし、前記エッチング後に等方性エッチングを行い、等方性エッチング後に前記ダミー材料の残りを除去することを特徴とするドライエッチング方法である。

(もっと読む)

プラズマエッチング方法

【課題】基板の表面をエッチングして穴部を形成する際に、穴部の側壁を基板の表面に対して垂直にできるとともに、高速にシリコン層をエッチングできるプラズマエッチング方法を提供する。

【解決手段】シリコン層の上方にレジスト層が形成されてなる被処理基板が設置されている処理容器内に、酸素ガスとフッ化硫黄ガスとを含んだエッチングガスを所定の流量で供給し、供給したエッチングガスをプラズマ化したプラズマにより、シリコン層をエッチングするプラズマエッチング方法において、フッ化硫黄ガスの流量に対する酸素ガスの流量の流量比を第1の流量比とした状態でエッチングする第1のステップS1と、流量比が第1の流量比から第1の流量比よりも小さい第2の流量比になるように、酸素ガスの流量を減少させながらエッチングする第2のステップS2と、流量比を第2の流量比とした状態でエッチングする第3のステップS3とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】SiCからなる第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、第2層間膜17をエッチングすることにより低段部28を形成する。このとき、第2層間膜17(SiC)からCを解離させ、その解離したCを含む反応生成物を側壁保護膜32に定着させることによって、側壁保護膜32を厚くする。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2膜33およびSiC膜35からなる積層膜36を形成し、この積層膜36をパターニングすることによりハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、当該エッチングによりSiC膜35から解離したCを含む反応生成物を含む側壁保護膜32を、エッチング途中のAlCu膜30の側面に形成しながらAlCu配線層34をパターニングすることによって、第1AlCu配線20を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、この配線20を窒素プラズマに曝露する。これにより、既存の側壁保護膜32にAlNが合わさって側壁保護膜32を分厚くすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、この配線20の表面を覆うように、SiN膜38を形成する。これにより、既存の側壁保護膜36にSiN膜38が合わさって側壁保護膜32が形成される。

(もっと読む)

貼り合せ構造体及び貼り合せ構造体の製造方法、並びに被処理基板の構造体の製造方法

【課題】被処理基板における凹凸形状を備えた面と下地基板の表面とを仮接着した後に減圧下において処理する際の、加工精度、処理効率、及び/又は処理の安全性を高める。

【解決手段】本発明の1つの貼り合せ構造体40の製造方法は、凹部42A及び凸部42Bが形成された第1表面を備える被処理基板41の第1表面42上に、25℃における粘度が0.02Pa・s以上0.1Pa・s以下である溶液状仮接着材を供給する溶液状仮接着材供給工程と、その溶液状仮接着材を加熱することにより、第1表面42の凸部42Bを10μm超20μm以下の厚みの仮接着材46Bによって覆う仮接着材形成工程と、その仮接着材46Bを介して、第1表面42と平板状の下地基板48とを一時的に貼り合わせる貼り合せ工程とを含む。

(もっと読む)

シリコンウエハの加工方法及び貫通電極付3次元シリコンインターポーザ並びにチップサイズパッケージ

【課題】シリコンウエハに貫通孔を形成することが不可欠なチップサイズパッケージや3次元積層型のパッケージについて、シリコンウエハに直接識別記号を形成する技術を提供することを目的とした

【解決手段】少なくとも、シリコンウエハ上に感光性レジストを塗布する塗布工程、感光性レジストを所定のパターンを有する濃度分布マスクを介して露光する露光工程、感光性レジストにシリコンウエハが露出する開口部と露出しない開口部とを形成する現像工程、ドライエッチングにより感光性レジスト開口部に対応する部位のシリコンウエハを除去してシリコンウエハに導通用の貫通孔と非貫通孔から構成される識別記号とを同時に形成する工程、残余の感光性レジストを除去する工程、とを有することを特徴とするシリコンウエハの加工方法である。

(もっと読む)

半導体レーザ素子の製造方法

【課題】リッジ部を形成するためのエッチングの際にGaAsキャップ層の側壁にサイドエッチングが進行することを防止できる半導体レーザ素子の製造方法を提供する。

【解決手段】本発明の半導体レーザ素子の製造方法は、半導体基板2上にnクラッド層3と、活性層4と、第1pクラッド層5と、エッチングストップ層6と、第2pクラッド層7と、キャップ層9とを順次積層して形成する工程と、キャップ層9の一部を除去した開口部10AにZnO層11を形成して窓領域を形成する工程と、開口部10Aからキャップ層9上にかけてストライプ状の絶縁膜マスクパターン16を形成し、絶縁膜マスクパターン16から露出したキャップ層9をエッチング除去する工程と、絶縁膜マスクパターン16から露出しているキャップ層9の側壁を酸化する工程と、エッチングストップ層6に達するまでエッチングを行ってリッジを形成する工程とを含むことを特徴とする。

(もっと読む)

半導体素子の作製方法

【課題】半導体からのV族原子の脱離を抑制しつつ同一面内でエッチング深さが異なる形状を簡易に加工することができる半導体素子の作製方法を提供する。

【解決手段】酸素プラズマの所定の濃度に対して、開口部幅の異なる領域毎に、半導体表面にて酸素プラズマによりポリマーの生成を抑制しつつ半導体表面のエッチングが進行する状態のみが発現するように前記開口部幅1905が設定された開口部1901を有するマスク1900を半導体表面に形成する第1の工程と、マスク1900が形成された前記半導体表面に前記炭化水素系プラズマおよび前記酸素プラズマを照射し、前記酸素プラズマを前記マスクの開口部幅方向にて前記開口部に拡散させることによりポリマーの生成を抑制するとともにエッチングに寄与する炭化水素系プラズマの濃度を制御する第2の工程を有するようにした。

(もっと読む)

エッチングマスクスタックを用いたマルチマスクプロセス

【課題】基板の上のエッチング層内にエッチング特徴を形成するための方法が提供される。

【解決手段】エッチングマスクスタックが、エッチング層の上に形成される。第1のマスクが、エッチングマスクスタックの上に形成される。第1のマスクによって定められる間隔の幅を低減させる側壁層が、第1のマスクの上に形成される。側壁層を通して、第1組の特徴が、エッチングマスクスタック内へとエッチングされる。マスクおよび側壁層は、除去される。追加の特徴のステップが実施される。該ステップは、追加のマスクをエッチングマスクスタックの上に形成することと、側壁層を追加のマスクの上に形成することと、第2組の特徴を少なくとも部分的にエッチングマスクスタック内へとエッチングすることと、を含む。エッチングマスクスタック内の第1組の特徴および第2組の特徴を通して、複数の特徴がエッチング層内にエッチングされる。

(もっと読む)

1 - 20 / 258

[ Back to top ]