Fターム[5F005AC03]の内容

Fターム[5F005AC03]に分類される特許

1 - 11 / 11

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

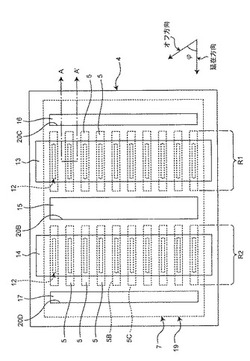

半導体装置

【課題】例えばSIThyに適用した場合に、ゲート電極とカソード電極との短絡を防止すると共に、ゲート電流の増大、チャネル領域の面積の拡大を図る。

【解決手段】半導体基板12の一主面に複数のランド20と複数のグルーブ22が形成されている。ランド20の表面部にカソード領域24が形成され、グルーブ22の底部にゲート領域26が形成されている。グルーブ22内にゲート電極16が形成され、ランド20の上面にカソード電極14が形成されている。ランド20の上面とグルーブ22の底面にわたって絶縁膜28が形成されている。カソード電極14の側面とゲート電極16と絶縁膜28とを覆うように層間絶縁膜30が形成され、カソード電極14上面と層間絶縁膜30とを覆うように接続電極32が形成されて各カソード電極14が電気的に接続されている。グルーブ22の側壁とゲート電極16の側壁との間に絶縁膜28のみが介在している。

(もっと読む)

半導体装置

【課題】保持電流特性に影響を与えずに、点弧動作感度の高感度化を実現するサイリスタ(半導体装置)を提供する。

【解決手段】サイリスタ100は、p領域1とn領域2とp領域3とn領域4とが順に接合されるサイリスタを有する。また、サイリスタ100は、n領域2とp領域3とに接して形成され、n領域2とp領域3との接合耐圧より接合耐圧が低い低耐圧領域10を有する。低耐圧領域10は、該領域において接合面にかかる電界方向の該領域幅が、サイリスタ100のブレークダウン電圧によって該領域に生成される空乏層幅より広く、サイリスタ100のブレークオーバ電圧によって接合面がブレークダウンする範囲において狭く形成される。

(もっと読む)

半導体装置

【課題】保護素子としてサイリスタを用いる場合に、サイリスタのトリガ電圧をホールド電圧から独立して変更することができるようにする。

【解決手段】第1の第1導電型拡散層120、第1の第2導電型拡散層130、第2の第1導電型拡散層150、及び第2の第2導電型拡散層140はこの順に並んでいる。そして第2の第2導電型拡散層140及び第1導電型層100が互いに接する領域におけるこれらの不純物濃度は、第2の第2導電型拡散層140の底面に位置する部分よりも、第2の第2導電型拡散層140の側面に位置する部分のほうが高い。

(もっと読む)

圧接型半導体装置

【課題】主電極にめっきを施しつつ、主電極の端部を含む面に圧接電極を面接合させることができる圧接型半導体装置を提供する。

【解決手段】半導体基体12と、めっき処理され、該半導体基体12の主面に固着されためっき付き主電極22と、該めっき付き主電極22のめっき22aが形成された面に重なるように圧接された圧接電極と、を備える。そして、該めっき付き主電極22の側面には溝22bが形成され、該溝22bは、該半導体基体12と該めっき付き主電極22が重なる部分の直上領域より外側に形成されたことを特徴とする。

(もっと読む)

パワー半導体デバイス

4層npnp構造、カソード面11およびアノード面12があり、ゲート電極4を介してターンオフできるパワー半導体デバイス1。カソード電極2とアノード電極3との間に以下の順で複数の層が配置される。−外側縁によって囲まれ、中央領域がある第1導電型カソード層5、カソード層5はカソード電極2と直接の電気的コンタクトにある,−第2導電型ベース層6,−カソード層5よりも低いドーピング濃度を有する第1導電型ドリフト層7、アノード電極3と電気的コンタクトにある第2導電型アノード層8。ゲート電極4は、カソード面11上にカソード電極2の横に配置され、ベース層6と電気的コンタクトにある。ベース層6は、カソード層5の中央領域に接触している、連続的な層としての、第1の深さに最大ドーピング濃度がある少なくとも1つの第1の層61を具備する。第1の層61よりも高いドーピング濃度を有し、第1の層61とカソード層5との間に配置され、第1の層61のほうを向いているカソード層5の外側縁をカバーする第2導電型抵抗減少層10,10’,10’’、この中でカソード層5の外側縁とベース層6との間の接合での抵抗が低減される。 (もっと読む)

半導体装置の製造方法

【課題】より高耐圧で高性能な半導体装置を製造することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板102を準備する半導体基板準備工程と、半導体基板102の表面に不純物イオン注入用マスクM1を形成し、不純物イオン注入用マスクM1の開口部からn型不純物イオンを注入する不純物イオン注入工程と、半導体基板102を所定のアニール温度に加熱してn型不純物イオンを活性化するアニール工程と、半導体基板102を所定の埋め込み拡散温度に加熱してアニール工程で活性化されたn型不純物原子の埋め込み拡散を行う埋め込み拡散工程とをこの順序で含む半導体装置の製造方法において、半導体基板準備工程において準備する半導体基板102は、埋め込み拡散工程でドナー化される酸素原子の量の分だけ、n型不純物の不純物濃度の設定値よりもn型不純物の不純物濃度を低くした半導体基板であることを特徴とする。

(もっと読む)

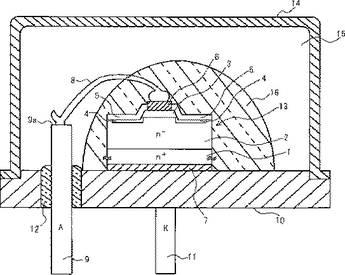

サイリスタ

【課題】 本発明の目的は良好なdV/dt−VCL特性を得る。

【解決手段】 第1導電型のエミッタ層2と、前記第1導電型と反対の第2導電型のベース層3と、前記第1導電型のバルク層5と、前記第2導電型の対面ベース層6とが順に平行的に配置され、前記ベース層および前記バルク層間に、該バルク層より高濃度の第1導電型の埋め込み層4が配置されたサイリスタ1において、前記埋め込み層は、前記ベース層と接する面を第1接合面および前記バルク層と接する面を第2接合面とするとき、該第2接合面の端が前記第1接合面に向かって傾斜を有して接し、かつ前記第1接合面の端が前記第2接合面の端に向かって所定の傾斜を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】良好なアバランシェ耐量を維持しつつ、オン抵抗を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】第1導電型の第1半導体領域10と、第1半導体領域10の表面に形成された第2導電型の第2半導体領域11と、第2半導体領域11の内部に形成された第1導電型の第3半導体領域14と、第2半導体領域11の下方に位置するように、第1半導体領域10の内部に形成された第2導電型の第4半導体領域12と、第2半導体領域11の側方に位置するように、第4半導体領域12に隣接して第1半導体領域10の表面に形成された第2導電型の第5半導体領域13とを備え、第4半導体領域12は、第5半導体領域13と同電位である。

(もっと読む)

高耐熱半導体装置

150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得るために、ワイドギャップ半導体素子の外面を合成高分子化合物で被覆する前記合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAと、シロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。  (もっと読む)

(もっと読む)

基板上に作製された半導体電子デバイス

【課題】IV族元素半導体、III−V族化合物半導体、II−V族化合物半導体、IV族化合物半導体、有機半導体、金属結晶もしくはそれらの誘導体又はガラスから成る基板上に作製された高耐圧電子デバイスおよび耐環境電子デバイスを提供する。

【解決手段】本発明においては、ダイオードやトランジスタ等の電子デバイス中で電子又は正孔が走行する領域に、既存の半導体デバイスに用いられている材料から成る基板上に必要に応じて酸化モリブデンから成るバッファ層を介して形成された高純度の酸化モリブデンが用いられる。これにより、高耐圧特性及び高耐環境特性を有する安価な電子デバイスが実現できる。

(もっと読む)

1 - 11 / 11

[ Back to top ]