Fターム[5F005AF02]の内容

Fターム[5F005AF02]に分類される特許

1 - 20 / 68

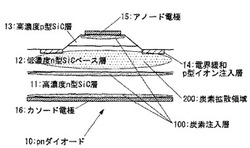

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

半導体素子および半導体装置

【課題】

順逆両方向の高耐圧と高信頼性と高い量産性を有する逆阻止半導体素子および逆阻止半導体装置を提供する。

【解決手段】

逆阻止半導体素子において、順方向耐圧達成用の第1のターミネーションのみを一方の主表面に形成し、逆方向耐圧達成用の第2のターミネーションは他方の主表面の活性領域の周囲に設けた第1の凹部の中に形成し、高い順逆両方向耐圧と高い量産性を実現する。第1の凹部により分断された半導体層を半導体支持体として活用して、ダイボンディング時のストレスによるセル内の各種欠陥の発生と稼働時の欠陥拡張とを抑制し、高耐圧と高信頼性を実現する。また逆阻止半導体装置において、素子を半田付けする主配線には素子の端部に対向して溝を設けて端部と主配線間の絶縁破壊電圧を高くし、高い逆方向耐圧を確保する。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

半導体装置

【課題】例えばSIThyに適用した場合に、ゲート電極とカソード電極との短絡を防止すると共に、ゲート電流の増大、チャネル領域の面積の拡大を図る。

【解決手段】半導体基板12の一主面に複数のランド20と複数のグルーブ22が形成されている。ランド20の表面部にカソード領域24が形成され、グルーブ22の底部にゲート領域26が形成されている。グルーブ22内にゲート電極16が形成され、ランド20の上面にカソード電極14が形成されている。ランド20の上面とグルーブ22の底面にわたって絶縁膜28が形成されている。カソード電極14の側面とゲート電極16と絶縁膜28とを覆うように層間絶縁膜30が形成され、カソード電極14上面と層間絶縁膜30とを覆うように接続電極32が形成されて各カソード電極14が電気的に接続されている。グルーブ22の側壁とゲート電極16の側壁との間に絶縁膜28のみが介在している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐電圧特性の温度依存性を改善した半導体装置及び半導体装置の製造方法を提供する。

【解決手段】アノード端子T2に、カソード端子T1に対して大きな電圧を印加したときに形成される空乏層DLに、N型半導体領域N4から到達する電子が増加しないように、N型半導体領域N4を、不純物を高濃度に含む高濃度N型半導体領域N4aと、高濃度N型半導体領域N4aに比較して不純物を低濃度に含む低濃度N型半導体領域N4bとが交互に配置される構成とする。

(もっと読む)

圧接型GTOサイリスタ

【課題】均一なターンオフ動作をさせ、ターンオフ動作の失敗による素子の破壊を抑制可能な圧接型GTOサイリスタを提供することを目的とする。

【解決手段】本発明にかかる圧接型GTOサイリスタは、半導体基体12と半導体基体12上に平面視環状に配置されてカソード電極18を形成するエレメントパターンと、環状の中央近傍において、半導体基体12上に圧接されたゲート電極38と、ゲート電極38の所定方向の側面に接続されたゲートリード44とを備え、環状の中心位置である第1平面中心Aが、ゲート電極38の平面視における中心位置である第2平面中心Bに対し、所定方向にずれて位置する。

(もっと読む)

バイポーラ半導体素子

【課題】ドリフト層とドリフト層に隣接する層との界面の応力を低減して、順方向電圧を低く抑えることができるバイポーラ半導体素子を提供する。

【解決手段】このpinダイオード20は、n型SiCドリフト層23の膜厚の各範囲(300μm以下200μm超),(200μm以下100μm超),(100μm以下50μm超)に対応して、n型SiCバッファ層22の不純物濃度の各上限値(5×1017cm−3),(7×1017cm−3),(10×1017cm−3)が設定されている。これにより、n型SiCドリフト層23とn型SiCバッファ層22との界面の応力を低減でき、順方向電圧を低減できる。

(もっと読む)

バイポーラ半導体素子

【課題】制御電極による制御能力を向上できるバイポーラ半導体素子を提供する。

【解決手段】このゲートターンオフサイリスタは、隣り合う2列R1,R2のメサ型のアノードエミッタ層5の間で列方向に延在している列間の第1のコンタクトホール20Bに形成された第1のゲート端子15だけでなく、各列R1,R2の端側で各列R1,R2に沿って列方向に延在している端側の第2,第3のコンタクトホール20C,20Dに形成された第2,第3のゲート端子16,17を有する。これにより、列間の第1のゲート端子15と端側の第2,第3のゲート端子16,17とでターンオフ時の転流を分担できて、転流の不揃いを抑制できる。

(もっと読む)

逆阻止型サイリスタ

【課題】本発明は、高い周波数のスイッチング動作に対応でき、且つ、電力損失を低減できる逆阻止型サイリスタを提供することを目的とする。

【解決手段】P領域(1a、1b)とN領域(2a、2b)とP領域3とN領域4とが順に接合された逆阻止型サイリスタ100は、P領域(1a、1b)からN領域4に順方向電圧が印加された場合にP領域(1a、1b)とN領域4の間を導通させる前の最大電圧値を示すブレークオーバ電圧が、N領域4からP領域(1a、1b)に逆方向電圧が印加された場合にN領域4とP領域(1a、1b)の間の導通を阻止する限界の電圧値を示すブレークダウン電圧より低くなるように電圧差を生じさせる電圧差生成領域30を有する。

(もっと読む)

半導体装置

【課題】オン電圧を低減した半導体装置を提供する。

【解決手段】第1導電型の第1の半導体層と、前記第1の半導体層の上に設けられた第2導電型の第2の半導体層と、前記第1の半導体層の上に前記第2の半導体層と接して設けられた前記第1の半導体層よりも不純物濃度の高い第1導電型の第3の半導体層と、前記第2の半導体層に接続された第1の金属層と、前記第3の半導体層に接続され前記第1の金属層とは異なる金属からなる第2の金属層と、を有する第1の主電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置の動作方法

【課題】ワイドギャップ半導体素子を動作させる半導体装置の動作方法であって、積層欠陥の発生による素子破壊を招くことなく簡単に実現できるとともに、定格電流に達するまでの時間を短縮できるものを提供すること。

【解決手段】ゼロから定格電流までの或る電流の値I1を設定して、上記通電電流がゼロからI1に達するまでの電流上昇率を一定値dI1/dtとし、上記通電電流がI1から上記定格電流に達するまでの電流上昇率をdIn/dtとする。上記ワイドギャップ半導体素子内の積層欠陥の発生による上記ワイドギャップ半導体素子の破壊を防止するように、上記dI1/dtは、一定値で、かつ0.5秒<(I1÷(dI1/dt))なる関係式を満たす。上記dIn/dtは、(dI1/dt)<(dIn/dt)なる関係式を満たす。

(もっと読む)

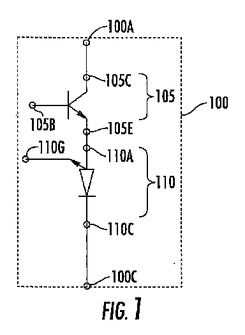

非負の温度係数及び関連した制御回路を有するワイド・バンドギャップ・バイポーラ・ターンオフ・サイリスタ

アノード、カソード及びゲート端子を有するワイド・バンドギャップ・サイリスタと、ベース、コレクタ及びエミッタ端子を有するワイド・バンドギャップ・バイポーラ・トランジスタを含む。バイポーラ・トランジスタとサイリスタとが直列接続されるように、バイポーラ・トランジスタのエミッタ端子は、サイリスタのアノード端子に直接結合される。バイポーラ・トランジスタ及びサイリスタは、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスを特徴付け、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスは、非導通状態と、ベース端子への第一制御信号の印加及びゲート端子への第二制御信号の印加に応答してバイポーラ・トランジスタのコレクタ端子に対応する第1主端子とサイリスタのカソード端子に対応する第2主端子との間に電流を流すことができる導通状態との間を切り替えるように構成される。関連した制御回路も開示される。  (もっと読む)

(もっと読む)

半導体装置の動作方法

【課題】ワイドギャップ半導体素子を動作させる半導体装置の動作方法であって、積層欠陥の発生による素子破壊を招くことなく簡単に実現できるものを提供すること。

【解決手段】この発明の半導体装置の動作方法では、ワイドギャップ半導体素子の通電開始時に通電電流Iを或る電流上昇率でゼロから定格電流Inまで上昇させる。ワイドギャップ半導体素子内の積層欠陥の発生によるワイドギャップ半導体素子の破壊を防止するように、通電電流Iをゼロから定格電流Inまで上昇させるソフトスタート時間tsを0.5秒から10秒までの範囲内に設定する。

(もっと読む)

縦型のバイポーラトランジスタとその製造方法

【課題】 ダイシングラインに沿って深部に至る深い不純物拡散領域を形成することによって必要な耐圧を確保する技術において、深い不純物拡散領域8を短時間の熱処理で製造可能な技術を提供する。

【解決手段】半導体基板4に不純物拡散領域を形成する際に、注入エネルギーを変えながら複数回に亘って不純物を注入する工程と、その後に半導体基板4を熱処理する工程を備えている。複数の深さL1〜L5に不純物を注入しておいてから熱処理をするので、深い不純物拡散領域8を短時間の熱処理で形成することができる。このバイポーラトランジスタ2の場合、複数の深さL1〜L5において不純物濃度のピークが観測される。

(もっと読む)

ゲートターンオフサイリスタ装置およびバイポーラトランジスタ装置

【課題】オフゲート電流によるサージ電圧によるアノードとゲートとの間の故障の発生を回避可能で信頼性を向上でき、かつ、小型化を図れるゲートターンオフサイリスタ装置を提供する。

【解決手段】このSiC GTO装置によれば、オフゲート電流によって発生するアノード電極12とゲート電極13との間のサージ電圧をツェナーダイオード構造部6によって抑制できる。また、n型SiC基板1とn型SiCバッファ層2とp型SiCバッファ層3とp型SiCドリフト層4とn型SiCベース層5およびp型SiCアノード層7とp型SiCコンタクト層8が構成するGTO素子自体にツェナーダイオード構造部6が組み込まれているので、GTO素子とは別個にツェナーダイオードを設ける場合に比べて、小型化を図れる。

(もっと読む)

低角度オフカット炭化ケイ素結晶上の安定なパワーデバイス

【課題】炭化ケイ素中の結晶欠陥を低減することができるプロセスならびにその結果得られる構造体およびデバイスを提供すること。

【解決手段】炭化ケイ素ベースのパワーデバイスが、<0001>方向に対して8°よりも小さいオフアクシス角を形成する平坦な表面を有する炭化ケイ素ドリフト層を含む。

(もっと読む)

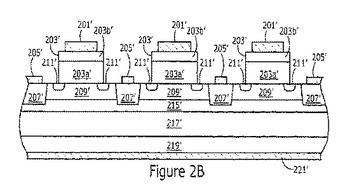

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

点滅回路

【課題】消費電力を少なくするとともに、部品点数を少なくすることで低コスト化を図った点滅回路を提供することを目的とする。

【解決手段】発光サイリスタ20の第1端子であるアノード端子は、抵抗13を介して電源VDDに接続するとともにコンデンサ15を介してグランドに接続し、第2端子であるカソード端子は抵抗14を介してグランドに接続し、第3端子であるゲート端子は抵抗11と抵抗12の直列回路の接続中心に接続する。

(もっと読む)

バイポーラ型半導体装置

【課題】表面欠陥に起因する積層欠陥が生じても、リーク電流を低減でき、最小点弧電流の増大を防止できるバイポーラ型半導体装置を提供する。

【解決手段】n型の半導体基板とその半導体基板上にエピタキシャル成長により順に形成された複数の半導体層とを備えたシリコンカーバイト(SiC)を母材とする主構造体1と、上記主構造体1の半導体層の最上層に形成され、半導体基板のオフ方向に対してストライプ方向(矢印R1)が略直交するメサストライプ部2と、上記メサストライプ部2のメサ2a上に形成されたアノード電極3と、上記半導体基板の裏面に形成されたカソード電極5と、上記メサストライプ部2のメサ2a間に露出する半導体層上に形成されたゲート電極4とを備える。

(もっと読む)

電力半導体デバイスのためのメサ終端構造とメサ終端構造をもつ電力半導体デバイスを形成するための方法

【課題】デバイスのピーク電界強度が低減し、実効的降服電圧を増加させ、デバイスの歩留まりを改善すること。

【解決手段】第1の伝導型を有するドリフト層と、前記ドリフト層上にあって、前記第1の伝導型とは反対の第2の伝導型を有し、前記ドリフト層とP−N接合を形成するバッファ層と、前記P−N接合の近傍の前記ドリフト層内にあって前記第2の伝導型を有する接合終端拡張領域とを含む電子デバイスを提供する。前記バッファ層は、前記接合終端拡張領域の埋め込み部分上を延びる階段部分を含む。関連する方法も開示される。

(もっと読む)

1 - 20 / 68

[ Back to top ]